General Hardware Design

3.8.1Signal Interface

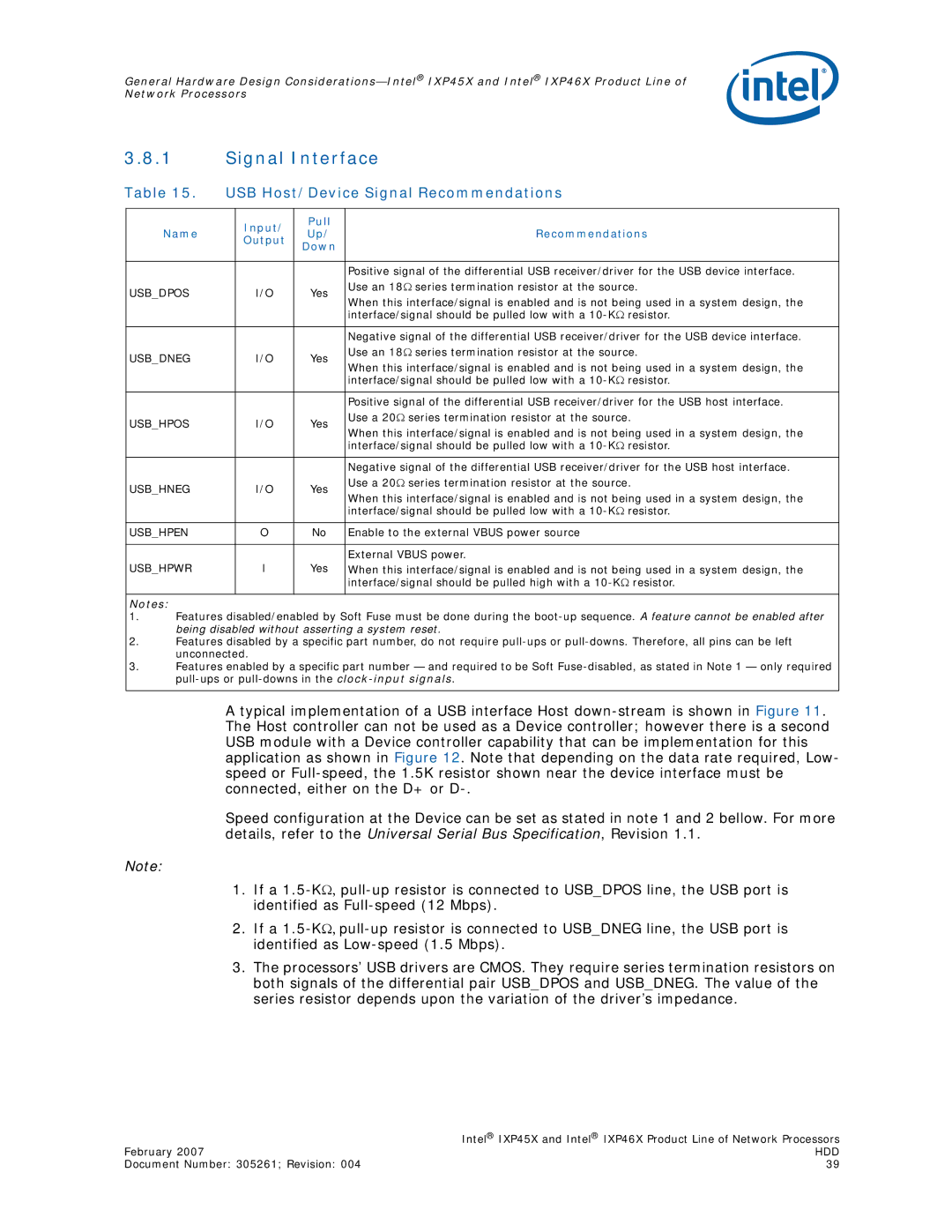

Table 15. | USB Host/Device Signal Recommendations | ||||

|

|

|

|

|

|

|

|

| Input/ | Pull |

|

| Name |

| Up/ | Recommendations | |

|

| Output | |||

|

|

| Down |

| |

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| Positive signal of the differential USB receiver/driver for the USB device interface. |

USB_DPOS |

| I/O | Yes | Use an 18Ω series termination resistor at the source. | |

| When this interface/signal is enabled and is not being used in a system design, the | ||||

|

|

|

|

| |

|

|

|

|

| interface/signal should be pulled low with a |

|

|

|

|

|

|

|

|

|

|

| Negative signal of the differential USB receiver/driver for the USB device interface. |

USB_DNEG |

| I/O | Yes | Use an 18Ω series termination resistor at the source. | |

| When this interface/signal is enabled and is not being used in a system design, the | ||||

|

|

|

|

| |

|

|

|

|

| interface/signal should be pulled low with a |

|

|

|

|

|

|

|

|

|

|

| Positive signal of the differential USB receiver/driver for the USB host interface. |

USB_HPOS |

| I/O | Yes | Use a 20Ω series termination resistor at the source. | |

| When this interface/signal is enabled and is not being used in a system design, the | ||||

|

|

|

|

| |

|

|

|

|

| interface/signal should be pulled low with a |

|

|

|

|

|

|

|

|

|

|

| Negative signal of the differential USB receiver/driver for the USB host interface. |

USB_HNEG |

| I/O | Yes | Use a 20Ω series termination resistor at the source. | |

| When this interface/signal is enabled and is not being used in a system design, the | ||||

|

|

|

|

| |

|

|

|

|

| interface/signal should be pulled low with a |

|

|

|

|

| |

USB_HPEN |

| O | No | Enable to the external VBUS power source | |

|

|

|

|

|

|

|

|

|

|

| External VBUS power. |

USB_HPWR |

| I | Yes | When this interface/signal is enabled and is not being used in a system design, the | |

|

|

|

|

| interface/signal should be pulled high with a |

|

|

|

|

| |

Notes: |

|

|

|

| |

1. | Features disabled/enabled by Soft Fuse must be done during the | ||||

| being disabled without asserting a system reset. | ||||

2. | Features disabled by a specific part number, do not require | ||||

| unconnected. |

|

| ||

3. | Features enabled by a specific part number — and required to be Soft | ||||

| |||||

|

|

|

|

|

|

A typical implementation of a USB interface Host

Speed configuration at the Device can be set as stated in note 1 and 2 bellow. For more details, refer to the Universal Serial Bus Specification, Revision 1.1.

Note:

1.If a

2.If a

3.The processors’ USB drivers are CMOS. They require series termination resistors on both signals of the differential pair USB_DPOS and USB_DNEG. The value of the series resistor depends upon the variation of the driver’s impedance.

| Intel® IXP45X and Intel® IXP46X Product Line of Network Processors |

February 2007 | HDD |

Document Number: 305261; Revision: 004 | 39 |