Intel® IXP45X and Intel® IXP46X Product Line of Network

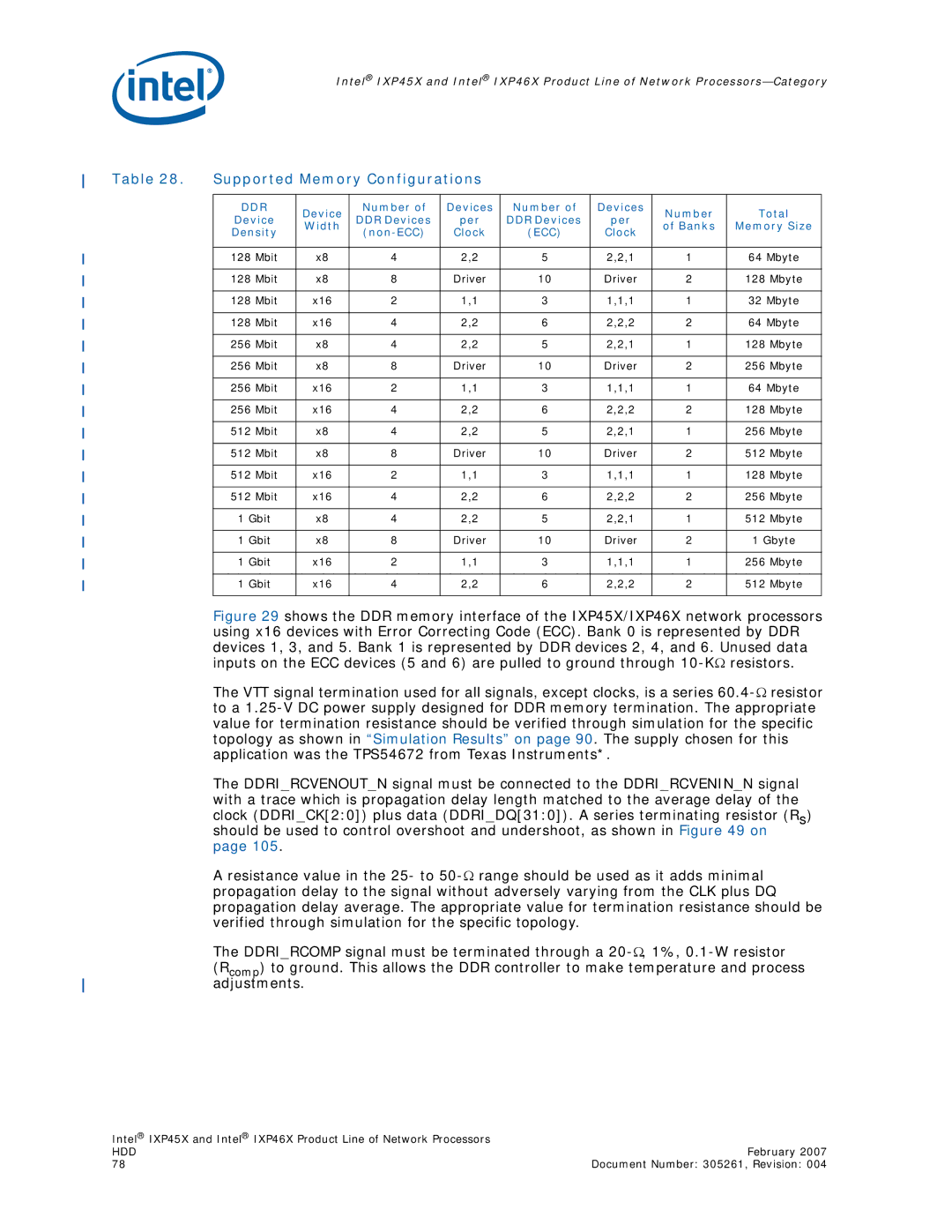

Table 28. | Supported Memory Configurations |

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| DDR | Device | Number of | Devices | Number of | Devices | Number | Total |

| Device | DDR Devices | per | DDR Devices | per | |||

| Density | Width | Clock | (ECC) | Clock | of Banks | Memory Size | |

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| 128 Mbit | x8 | 4 | 2,2 | 5 | 2,2,1 | 1 | 64 Mbyte |

|

|

|

|

|

|

|

|

|

| 128 Mbit | x8 | 8 | Driver | 10 | Driver | 2 | 128 Mbyte |

|

|

|

|

|

|

|

|

|

| 128 Mbit | x16 | 2 | 1,1 | 3 | 1,1,1 | 1 | 32 Mbyte |

|

|

|

|

|

|

|

|

|

| 128 Mbit | x16 | 4 | 2,2 | 6 | 2,2,2 | 2 | 64 Mbyte |

|

|

|

|

|

|

|

|

|

| 256 Mbit | x8 | 4 | 2,2 | 5 | 2,2,1 | 1 | 128 Mbyte |

|

|

|

|

|

|

|

|

|

| 256 Mbit | x8 | 8 | Driver | 10 | Driver | 2 | 256 Mbyte |

|

|

|

|

|

|

|

|

|

| 256 Mbit | x16 | 2 | 1,1 | 3 | 1,1,1 | 1 | 64 Mbyte |

|

|

|

|

|

|

|

|

|

| 256 Mbit | x16 | 4 | 2,2 | 6 | 2,2,2 | 2 | 128 Mbyte |

|

|

|

|

|

|

|

|

|

| 512 Mbit | x8 | 4 | 2,2 | 5 | 2,2,1 | 1 | 256 Mbyte |

|

|

|

|

|

|

|

|

|

| 512 Mbit | x8 | 8 | Driver | 10 | Driver | 2 | 512 Mbyte |

|

|

|

|

|

|

|

|

|

| 512 Mbit | x16 | 2 | 1,1 | 3 | 1,1,1 | 1 | 128 Mbyte |

|

|

|

|

|

|

|

|

|

| 512 Mbit | x16 | 4 | 2,2 | 6 | 2,2,2 | 2 | 256 Mbyte |

|

|

|

|

|

|

|

|

|

| 1 Gbit | x8 | 4 | 2,2 | 5 | 2,2,1 | 1 | 512 Mbyte |

|

|

|

|

|

|

|

|

|

| 1 Gbit | x8 | 8 | Driver | 10 | Driver | 2 | 1 Gbyte |

|

|

|

|

|

|

|

|

|

| 1 Gbit | x16 | 2 | 1,1 | 3 | 1,1,1 | 1 | 256 Mbyte |

|

|

|

|

|

|

|

|

|

| 1 Gbit | x16 | 4 | 2,2 | 6 | 2,2,2 | 2 | 512 Mbyte |

|

|

|

|

|

|

|

|

|

Figure 29 shows the DDR memory interface of the IXP45X/IXP46X network processors using x16 devices with Error Correcting Code (ECC). Bank 0 is represented by DDR devices 1, 3, and 5. Bank 1 is represented by DDR devices 2, 4, and 6. Unused data inputs on the ECC devices (5 and 6) are pulled to ground through 10-KΩ resistors.

The VTT signal termination used for all signals, except clocks, is a series

The DDRI_RCVENOUT_N signal must be connected to the DDRI_RCVENIN_N signal with a trace which is propagation delay length matched to the average delay of the clock (DDRI_CK[2:0]) plus data (DDRI_DQ[31:0]). A series terminating resistor (Rs) should be used to control overshoot and undershoot, as shown in Figure 49 on page 105.

A resistance value in the 25- to

The DDRI_RCOMP signal must be terminated through a

Intel® IXP45X and Intel® IXP46X Product Line of Network Processors |

|

HDD | February 2007 |

78 | Document Number: 305261, Revision: 004 |