7.1.5Timing Relationships

The routing guidelines presented in the following subsections define the recommended routing topologies, trace width, spacing geometries, and typical routed lengths for each signal group. These parameters are recommended to achieve optimal signal integrity and timing.

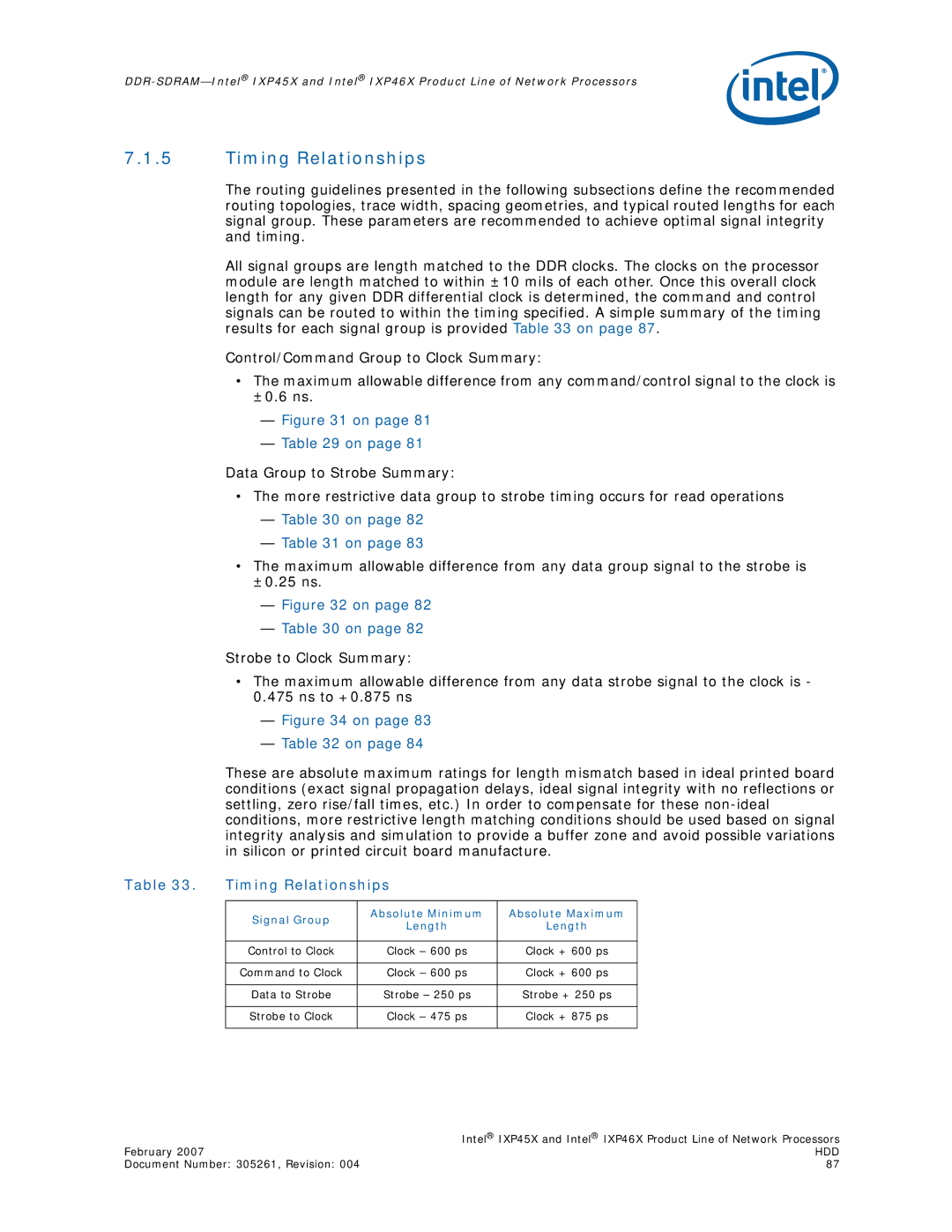

All signal groups are length matched to the DDR clocks. The clocks on the processor module are length matched to within ±10 mils of each other. Once this overall clock length for any given DDR differential clock is determined, the command and control signals can be routed to within the timing specified. A simple summary of the timing results for each signal group is provided Table 33 on page 87.

Control/Command Group to Clock Summary:

•The maximum allowable difference from any command/control signal to the clock is ±0.6 ns.

—Figure 31 on page 81

—Table 29 on page 81

Data Group to Strobe Summary:

•The more restrictive data group to strobe timing occurs for read operations

—Table 30 on page 82

—Table 31 on page 83

•The maximum allowable difference from any data group signal to the strobe is ±0.25 ns.

—Figure 32 on page 82

—Table 30 on page 82

Strobe to Clock Summary:

•The maximum allowable difference from any data strobe signal to the clock is - 0.475 ns to +0.875 ns

—Figure 34 on page 83

—Table 32 on page 84

These are absolute maximum ratings for length mismatch based in ideal printed board conditions (exact signal propagation delays, ideal signal integrity with no reflections or settling, zero rise/fall times, etc.) In order to compensate for these

Table 33. | Timing Relationships |

| |

|

|

|

|

| Signal Group | Absolute Minimum | Absolute Maximum |

| Length | Length | |

|

| ||

|

|

|

|

| Control to Clock | Clock – 600 ps | Clock + 600 ps |

|

|

|

|

| Command to Clock | Clock – 600 ps | Clock + 600 ps |

|

|

|

|

| Data to Strobe | Strobe – 250 ps | Strobe + 250 ps |

|

|

|

|

| Strobe to Clock | Clock – 475 ps | Clock + 875 ps |

|

|

|

|

| Intel® IXP45X and Intel® IXP46X Product Line of Network Processors |

February 2007 | HDD |

Document Number: 305261, Revision: 004 | 87 |