Philips Semiconductors | User’s Manual - Preliminary - | |

|

|

|

GENERAL DESCRIPTION | P89LPC906/907/908 | |

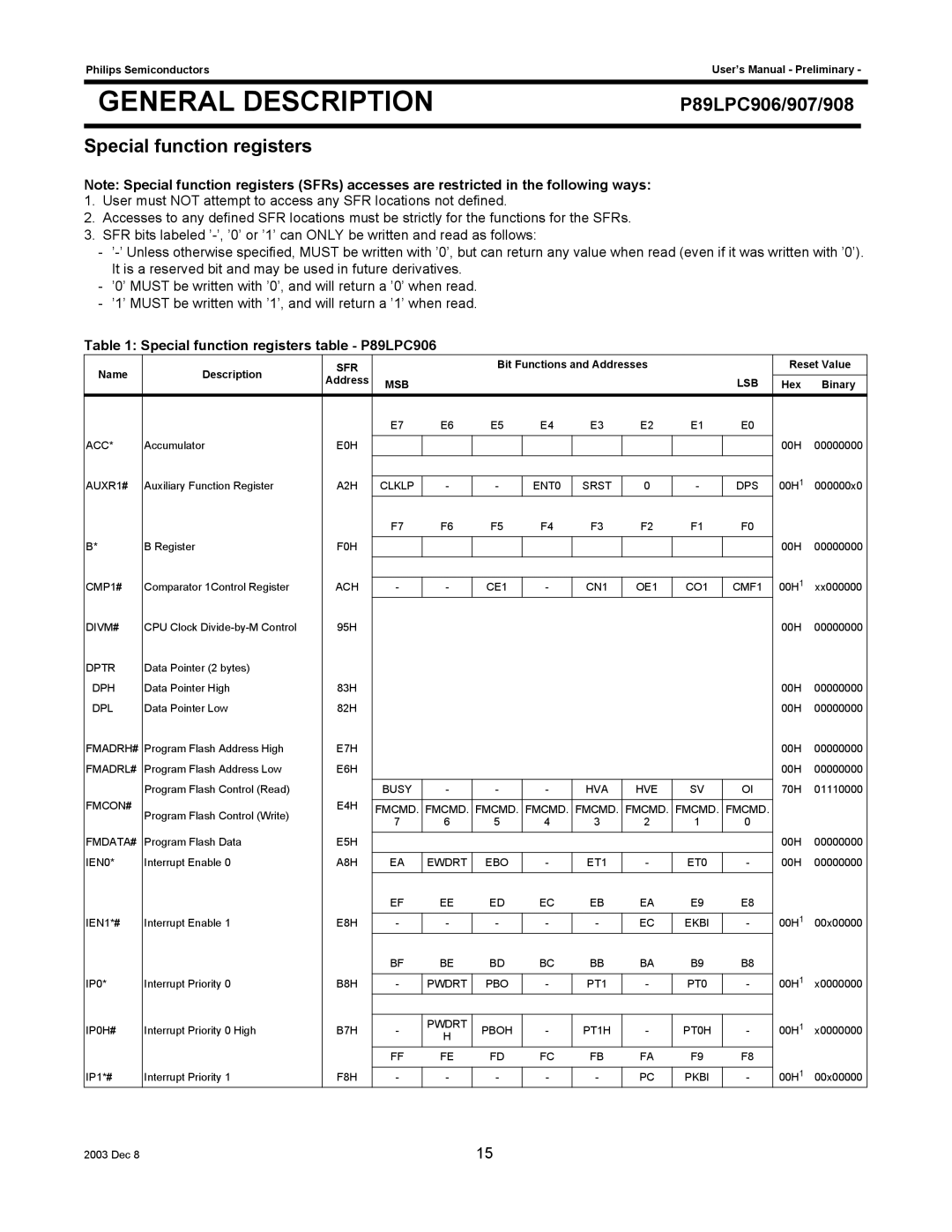

Special function registers |

|

|

Note: Special function registers (SFRs) accesses are restricted in the following ways:

1.User must NOT attempt to access any SFR locations not defined.

2.Accesses to any defined SFR locations must be strictly for the functions for the SFRs.

3.SFR bits labeled

-

-’0’ MUST be written with ’0’, and will return a ’0’ when read.

-’1’ MUST be written with ’1’, and will return a ’1’ when read.

Table 1: Special function registers table - P89LPC906

Name | Description | SFR |

|

| Bit Functions and Addresses |

|

| Reset Value | ||||

Address |

|

|

|

|

|

|

| LSB |

|

| ||

MSB |

|

|

|

|

|

| Hex | Binary | ||||

|

|

|

|

|

|

|

| |||||

|

|

| E7 | E6 | E5 | E4 | E3 | E2 | E1 | E0 |

|

|

ACC* | Accumulator | E0H |

|

|

|

|

|

|

|

| 00H | 00000000 |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| 00H1 | 000000x0 |

|

|

|

|

|

|

|

|

|

|

| ||

AUXR1# | Auxiliary Function Register | A2H | CLKLP | - | - | ENT0 | SRST | 0 | - | DPS | ||

|

|

| F7 | F6 | F5 | F4 | F3 | F2 | F1 | F0 |

|

|

B* | B Register | F0H |

|

|

|

|

|

|

|

| 00H | 00000000 |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| 00H1 | xx000000 |

|

|

|

|

|

|

|

|

|

|

| ||

CMP1# | Comparator 1Control Register | ACH | - | - | CE1 | - | CN1 | OE1 | CO1 | CMF1 | ||

DIVM# | CPU Clock | 95H |

|

|

|

|

|

|

|

| 00H | 00000000 |

DPTR | Data Pointer (2 bytes) |

|

|

|

|

|

|

|

|

|

|

|

DPH | Data Pointer High | 83H |

|

|

|

|

|

|

|

| 00H | 00000000 |

DPL | Data Pointer Low | 82H |

|

|

|

|

|

|

|

| 00H | 00000000 |

FMADRH# | Program Flash Address High | E7H |

|

|

|

|

|

|

|

| 00H | 00000000 |

FMADRL# | Program Flash Address Low | E6H |

|

|

|

|

|

|

|

| 00H | 00000000 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| Program Flash Control (Read) |

| BUSY | - | - | - | HVA | HVE | SV | OI | 70H | 01110000 |

FMCON# |

| E4H |

|

|

|

|

|

|

|

|

|

|

Program Flash Control (Write) | FMCMD. | FMCMD. | FMCMD. | FMCMD. | FMCMD. | FMCMD. | FMCMD. | FMCMD. |

|

| ||

|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

| |

|

|

|

|

| ||||||||

FMDATA# | Program Flash Data | E5H |

|

|

|

|

|

|

|

| 00H | 00000000 |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

IEN0* | Interrupt Enable 0 | A8H | EA | EWDRT | EBO | - | ET1 | - | ET0 | - | 00H | 00000000 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| EF | EE | ED | EC | EB | EA | E9 | E8 |

|

|

|

|

|

|

|

|

|

|

|

|

| 00H1 | 00x00000 |

IEN1*# | Interrupt Enable 1 | E8H | - | - | - | - | - | EC | EKBI | - | ||

|

|

| BF | BE | BD | BC | BB | BA | B9 | B8 |

|

|

|

|

|

|

|

|

|

|

|

|

| 00H1 | x0000000 |

IP0* | Interrupt Priority 0 | B8H | - | PWDRT | PBO | - | PT1 | - | PT0 | - | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

IP0H# | Interrupt Priority 0 High | B7H | - | PWDRT | PBOH | - | PT1H | - | PT0H | - | 00H1 | x0000000 |

|

|

|

| H |

|

|

|

|

|

|

|

|

|

|

| FF | FE | FD | FC | FB | FA | F9 | F8 |

|

|

|

|

|

|

|

|

|

|

|

|

| 00H1 | 00x00000 |

IP1*# | Interrupt Priority 1 | F8H | - | - | - | - | - | PC | PKBI | - | ||

2003 Dec 8 | 15 |