Philips Semiconductors |

|

|

|

|

|

| User’s Manual - Preliminary - | |

WATCHDOG TIMER |

|

|

| P89LPC906/907/908 | ||||

|

|

|

|

| WDL (C1H) |

|

| |

MOV WFEED1, #0A5H |

|

|

|

|

|

|

| |

MOV WFEED2, #05AH |

|

|

|

|

|

|

| |

Watchdog |

|

|

|

|

|

|

| |

Oscillator | ÷32 | PRESCALER |

|

|

|

| ||

|

| Counter |

|

| Interrupt | |||

CLK |

|

|

|

|

|

| ||

|

|

|

|

|

|

|

| |

|

|

|

| control register |

|

|

| SHADOW |

|

|

|

|

|

|

| REGISTER FOR | |

|

|

|

|

|

|

|

| WDCON |

|

| PRE2 | PRE1 | PRE0 | WDRUN | WDTOF | WDCLK | WDCON(A7H) |

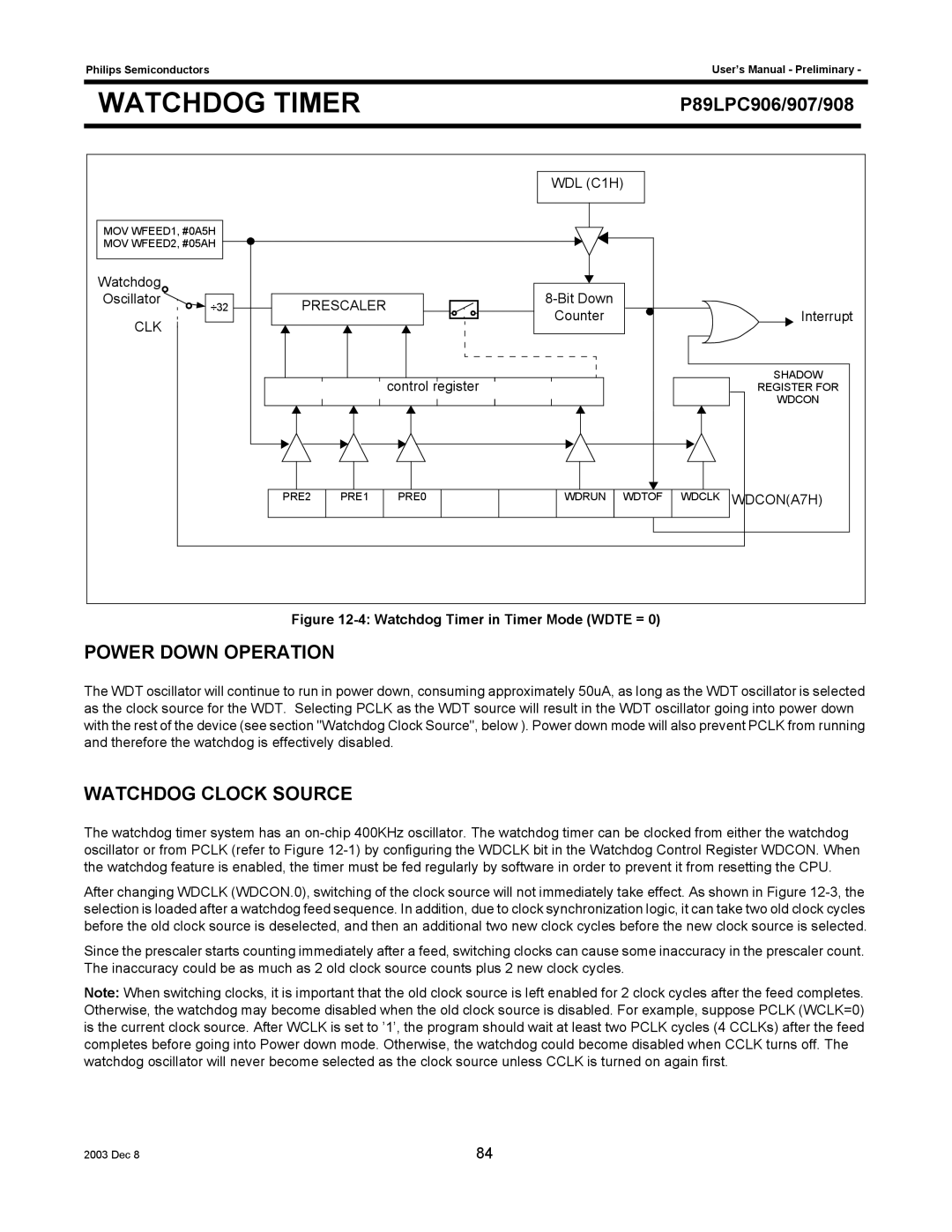

Figure 12-4: Watchdog Timer in Timer Mode (WDTE = 0)

POWER DOWN OPERATION

The WDT oscillator will continue to run in power down, consuming approximately 50uA, as long as the WDT oscillator is selected as the clock source for the WDT. Selecting PCLK as the WDT source will result in the WDT oscillator going into power down with the rest of the device (see section "Watchdog Clock Source", below ). Power down mode will also prevent PCLK from running and therefore the watchdog is effectively disabled.

WATCHDOG CLOCK SOURCE

The watchdog timer system has an

After changing WDCLK (WDCON.0), switching of the clock source will not immediately take effect. As shown in Figure

Since the prescaler starts counting immediately after a feed, switching clocks can cause some inaccuracy in the prescaler count. The inaccuracy could be as much as 2 old clock source counts plus 2 new clock cycles.

Note: When switching clocks, it is important that the old clock source is left enabled for 2 clock cycles after the feed completes. Otherwise, the watchdog may become disabled when the old clock source is disabled. For example, suppose PCLK (WCLK=0) is the current clock source. After WCLK is set to ’1’, the program should wait at least two PCLK cycles (4 CCLKs) after the feed completes before going into Power down mode. Otherwise, the watchdog could become disabled when CCLK turns off. The watchdog oscillator will never become selected as the clock source unless CCLK is turned on again first.

2003 Dec 8 | 84 |