Philips Semiconductors |

|

|

| User’s Manual - Preliminary - | ||

|

|

|

|

|

| |

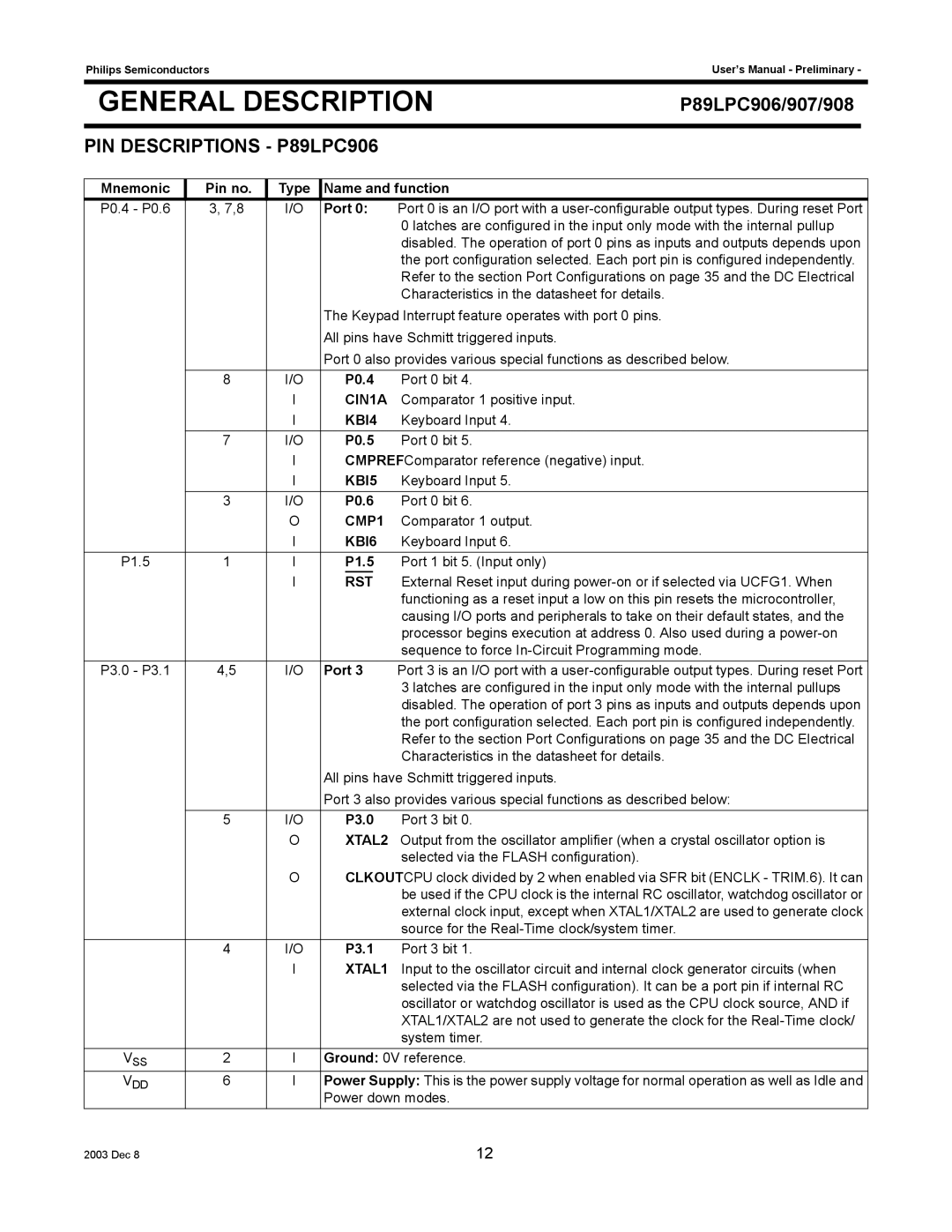

GENERAL DESCRIPTION | P89LPC906/907/908 | |||||

PIN DESCRIPTIONS - P89LPC906 |

|

|

| |||

|

|

|

|

|

| |

Mnemonic | Pin no. | Type | Name and function |

|

| |

P0.4 - P0.6 | 3, 7,8 | I/O | Port 0: | Port 0 is an I/O port with a | ||

|

|

|

| 0 latches are configured in the input only mode with the internal pullup | ||

|

|

|

| disabled. The operation of port 0 pins as inputs and outputs depends upon | ||

|

|

|

| the port configuration selected. Each port pin is configured independently. | ||

|

|

|

| Refer to the section Port Configurations on page 35 and the DC Electrical | ||

|

|

|

| Characteristics in the datasheet for details. |

|

|

|

|

| The Keypad Interrupt feature operates with port 0 pins. |

|

| |

|

|

| All pins have Schmitt triggered inputs. |

|

| |

|

|

| Port 0 also provides various special functions as described below. | |||

| 8 | I/O | P0.4 | Port 0 bit 4. |

|

|

|

| I | CIN1A | Comparator 1 positive input. |

|

|

|

| I | KBI4 | Keyboard Input 4. |

|

|

| 7 | I/O | P0.5 | Port 0 bit 5. |

|

|

|

| I | CMPREFComparator reference (negative) input. |

|

| |

|

| I | KBI5 | Keyboard Input 5. |

|

|

| 3 | I/O | P0.6 | Port 0 bit 6. |

|

|

|

| O | CMP1 | Comparator 1 output. |

|

|

|

| I | KBI6 | Keyboard Input 6. |

|

|

P1.5 | 1 | I | P1.5 | Port 1 bit 5. (Input only) |

|

|

|

| I | RST | External Reset input during | ||

|

|

|

| functioning as a reset input a low on this pin resets the microcontroller, | ||

|

|

|

| causing I/O ports and peripherals to take on their default states, and the | ||

|

|

|

| processor begins execution at address 0. Also used during a | ||

|

|

|

| sequence to force | ||

P3.0 - P3.1 | 4,5 | I/O | Port 3 | Port 3 is an I/O port with a | ||

|

|

|

| 3 latches are configured in the input only mode with the internal pullups | ||

|

|

|

| disabled. The operation of port 3 pins as inputs and outputs depends upon | ||

|

|

|

| the port configuration selected. Each port pin is configured independently. | ||

|

|

|

| Refer to the section Port Configurations on page 35 and the DC Electrical | ||

|

|

|

| Characteristics in the datasheet for details. |

|

|

|

|

| All pins have Schmitt triggered inputs. |

|

| |

|

|

| Port 3 also provides various special functions as described below: | |||

| 5 | I/O | P3.0 | Port 3 bit 0. |

|

|

|

| O | XTAL2 Output from the oscillator amplifier (when a crystal oscillator option is | |||

|

|

|

| selected via the FLASH configuration). |

|

|

|

| O | CLKOUTCPU clock divided by 2 when enabled via SFR bit (ENCLK - TRIM.6). It can | |||

|

|

|

| be used if the CPU clock is the internal RC oscillator, watchdog oscillator or | ||

|

|

|

| external clock input, except when XTAL1/XTAL2 are used to generate clock | ||

|

|

|

| source for the |

|

|

| 4 | I/O | P3.1 | Port 3 bit 1. |

|

|

|

| I | XTAL1 | Input to the oscillator circuit and internal clock generator circuits (when | ||

|

|

|

| selected via the FLASH configuration). It can be a port pin if internal RC | ||

|

|

|

| oscillator or watchdog oscillator is used as the CPU clock source, AND if | ||

|

|

|

| XTAL1/XTAL2 are not used to generate the clock for the | ||

|

|

|

| system timer. |

|

|

VSS | 2 | I | Ground: 0V reference. |

|

| |

VDD | 6 | I | Power Supply: This is the power supply voltage for normal operation as well as Idle and | |||

|

|

| Power down modes. |

|

| |

2003 Dec 8 | 12 |