Philips Semiconductors |

|

|

|

|

|

|

|

|

| User’s Manual - Preliminary - | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UART |

|

|

|

|

|

|

|

|

| P89LPC906/907/908 | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BRGCON |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Address: BDh |

| 7 |

| 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

| ||

Not bit addressable |

| - |

| - | - | - | - | - |

| SBRGS | BRGEN |

| ||

Reset Source(s): Any reset |

|

|

|

|

|

|

|

|

|

|

|

|

| |

Reset Value: xxxxxx00B |

|

|

|

|

|

|

|

|

|

|

|

|

| |

BIT | SYMBOL | FUNCTION |

|

|

|

|

|

|

|

|

|

| ||

- | Reserved for future use. Should not be set to 1 by user programs. |

|

|

| ||||||||||

BRGCON.1 | SBRGS | Select Baud Rate Generator as the source for baud rates to UART in modes 1 & 3 (see | ||||||||||||

|

| Table for details) |

|

|

|

|

|

|

|

|

|

| ||

BRGCON.0 | BRGEN | Baud Rate Generator Enable. Enables the baud rate generator. BRGR1 and BRGR0 can | ||||||||||||

|

| only be written when BRGEN =0. |

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

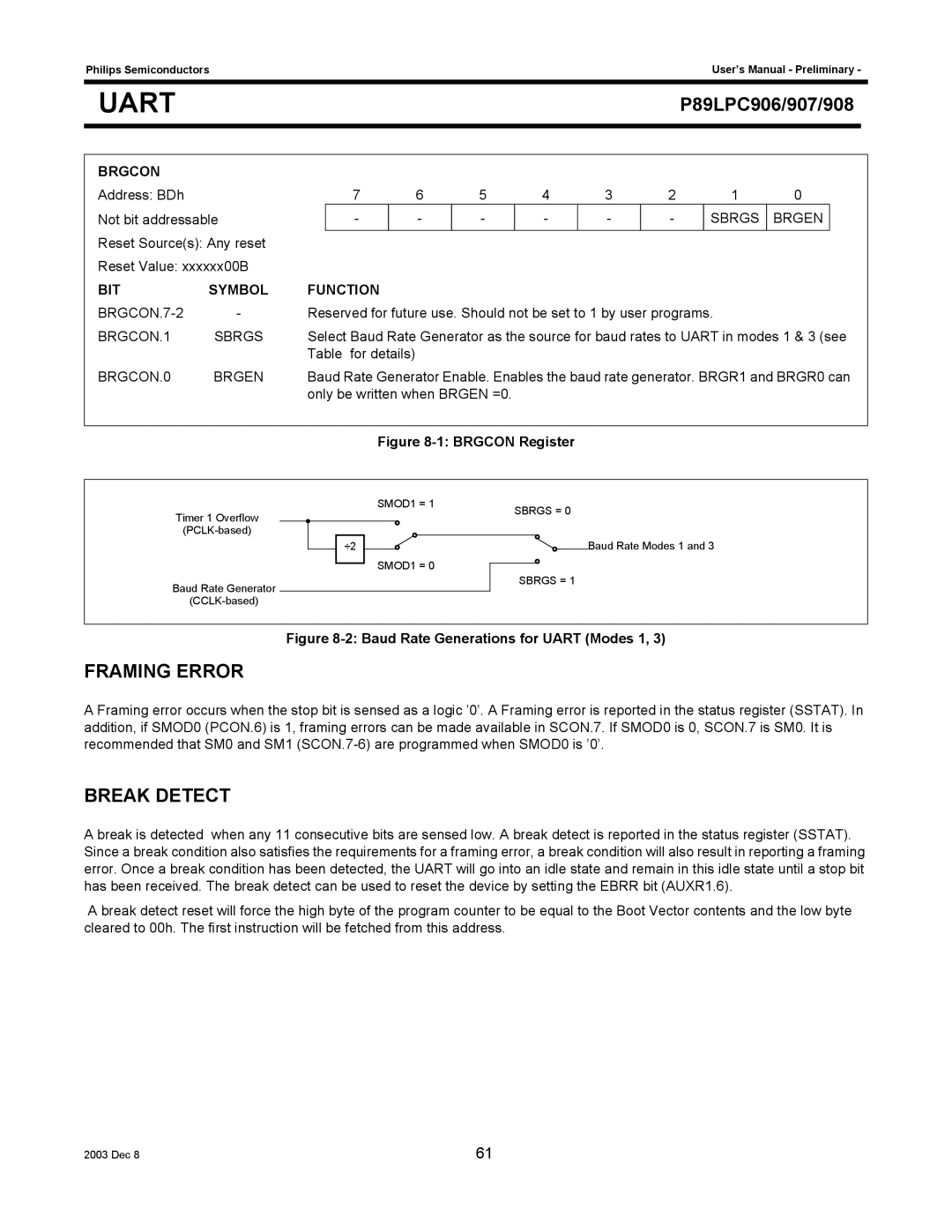

Figure 8-1: BRGCON Register

Timer 1 Overflow

Baud Rate Generator

SMOD1 = 1

÷2 ![]() SMOD1 = 0

SMOD1 = 0

SBRGS = 0

![]()

![]() Baud Rate Modes 1 and 3

Baud Rate Modes 1 and 3

SBRGS = 1

Figure 8-2: Baud Rate Generations for UART (Modes 1, 3)

FRAMING ERROR

A Framing error occurs when the stop bit is sensed as a logic ’0’. A Framing error is reported in the status register (SSTAT). In addition, if SMOD0 (PCON.6) is 1, framing errors can be made available in SCON.7. If SMOD0 is 0, SCON.7 is SM0. It is recommended that SM0 and SM1

BREAK DETECT

A break is detected when any 11 consecutive bits are sensed low. A break detect is reported in the status register (SSTAT). Since a break condition also satisfies the requirements for a framing error, a break condition will also result in reporting a framing error. Once a break condition has been detected, the UART will go into an idle state and remain in this idle state until a stop bit has been received. The break detect can be used to reset the device by setting the EBRR bit (AUXR1.6).

A break detect reset will force the high byte of the program counter to be equal to the Boot Vector contents and the low byte cleared to 00h. The first instruction will be fetched from this address.

2003 Dec 8 | 61 |