Philips Semiconductors | User’s Manual - Preliminary - | |

|

|

|

CLOCKS | P89LPC906/907/908 |

|

LOW POWER SELECT (P89LPC906)

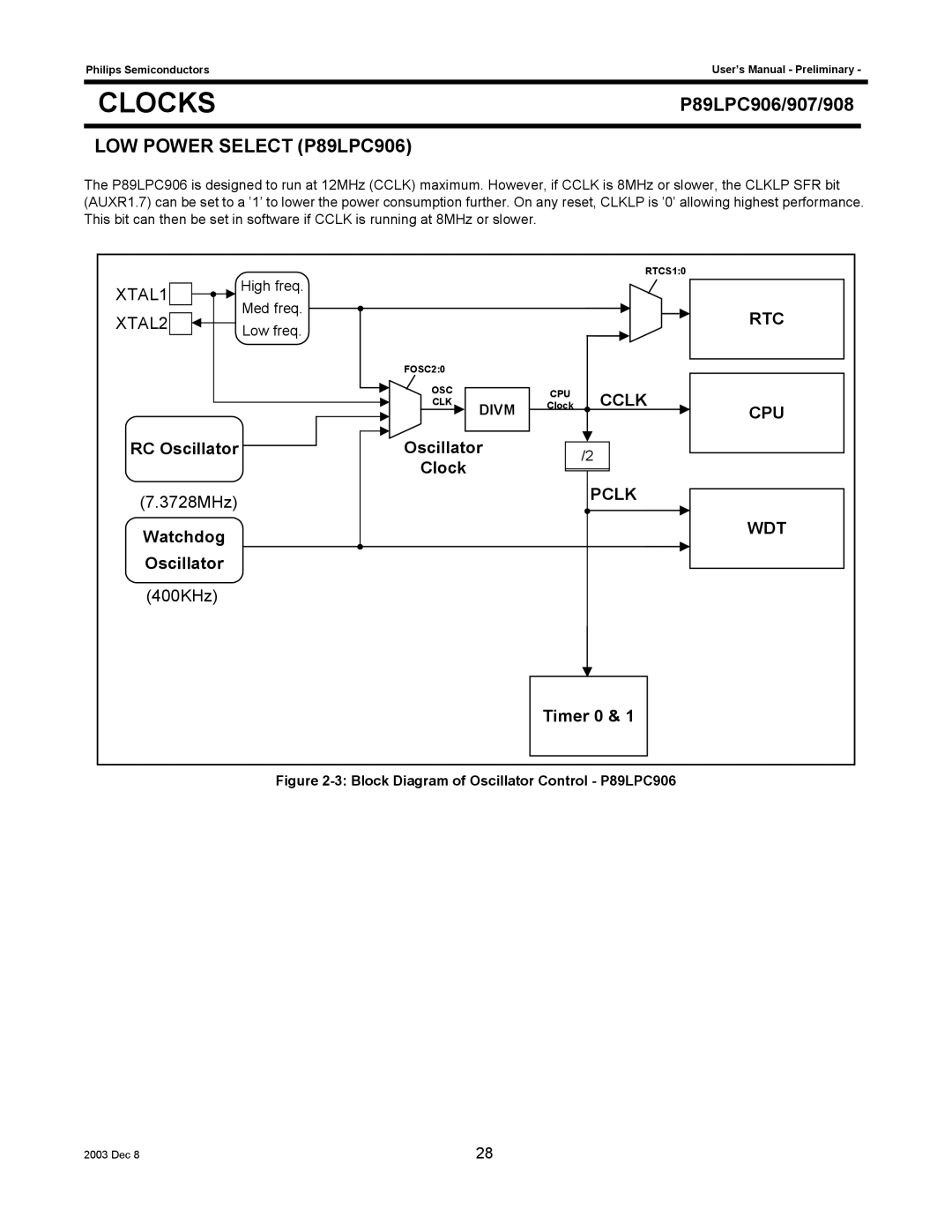

The P89LPC906 is designed to run at 12MHz (CCLK) maximum. However, if CCLK is 8MHz or slower, the CLKLP SFR bit (AUXR1.7) can be set to a ’1’ to lower the power consumption further. On any reset, CLKLP is ’0’ allowing highest performance. This bit can then be set in software if CCLK is running at 8MHz or slower.

| High freq. |

|

| RTCS1:0 |

|

XTAL1 |

|

|

|

| |

Med freq. |

|

|

|

| |

XTAL2 |

|

|

| RTC | |

Low freq. |

|

|

| ||

|

|

|

|

| |

| FOSC2:0 |

|

|

|

|

| OSC |

| CPU | CCLK |

|

| CLK |

|

| ||

| DIVM | Clock | CPU | ||

|

|

|

| ||

RC Oscillator | Oscillator |

| /2 |

| |

| Clock |

|

|

|

|

(7.3728MHz) |

|

|

| PCLK |

|

|

|

|

|

| |

Watchdog |

|

|

|

| WDT |

|

|

|

|

| |

Oscillator |

|

|

|

|

|

(400KHz) |

|

|

|

|

|

|

|

| Timer 0 & 1 |

| |

Figure 2-3: Block Diagram of Oscillator Control - P89LPC906

2003 Dec 8 | 28 |