Philips Semiconductors | User’s Manual - Preliminary - | |

|

|

|

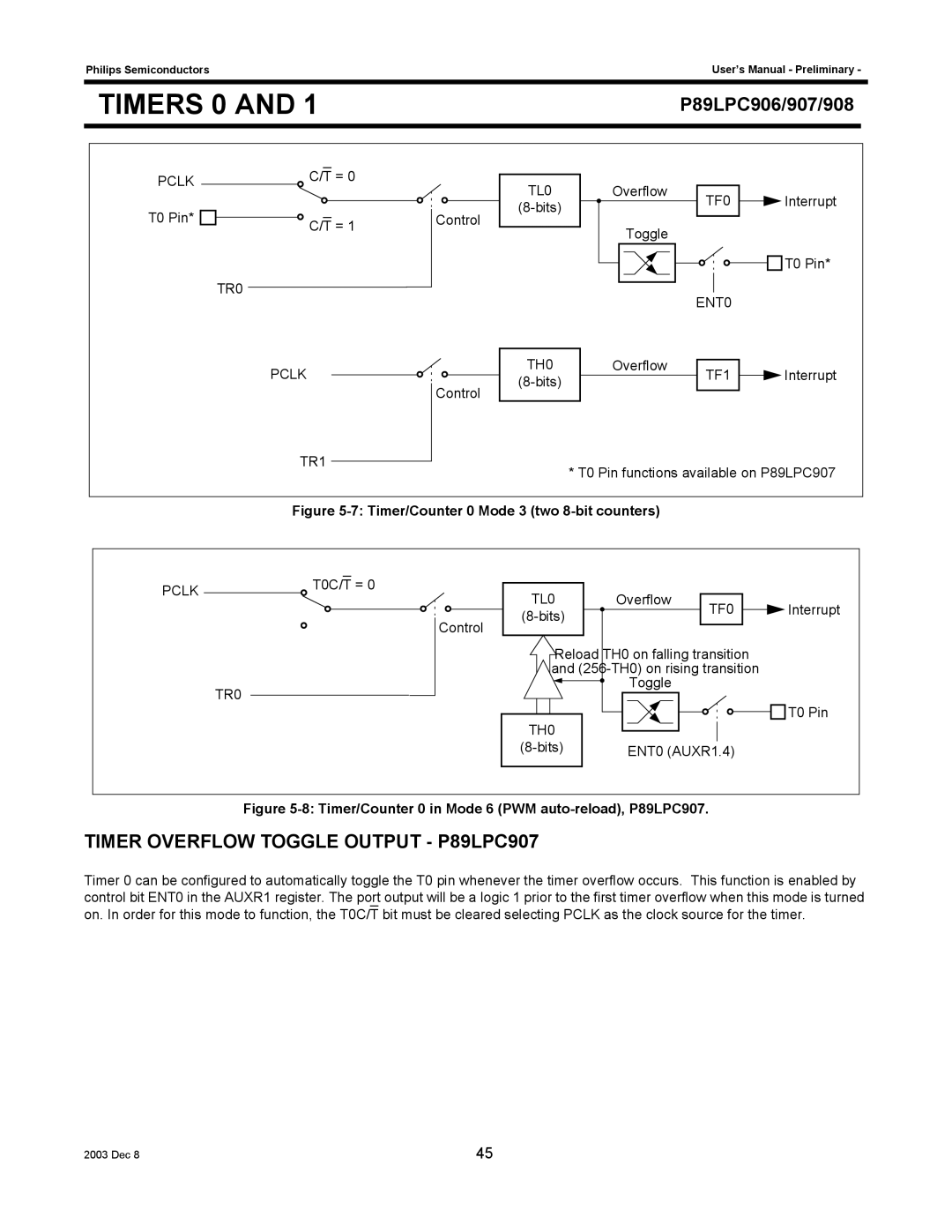

TIMERS 0 AND 1 | P89LPC906/907/908 |

|

PCLK | C/T = 0 |

| TL0 | Overflow |

|

|

|

|

|

| |||

|

|

| TF0 | Interrupt | ||

T0 Pin* |

|

|

| |||

C/T = 1 | Control |

|

|

| ||

| Toggle |

|

| |||

|

|

|

|

| ||

|

|

|

|

|

| |

|

|

|

|

|

| T0 Pin* |

| TR0 |

|

|

| ENT0 |

|

|

|

|

|

|

| |

| PCLK |

| TH0 | Overflow | TF1 | Interrupt |

| Control |

| ||||

|

|

|

|

| ||

|

|

|

|

|

| |

| TR1 |

|

| * T0 Pin functions available on P89LPC907 | ||

|

|

|

| |||

| Figure |

|

| |||

|

|

|

|

|

|

PCLK |

| T0C/T = 0 | |||

|

|

|

|

| |

|

|

|

|

|

|

TR0

Control

TL0 | Overflow |

|

|

|

TF0 |

| Interrupt | ||

|

| |||

|

| |||

|

|

|

|

![]()

![]() Reload TH0 on falling transition and

Reload TH0 on falling transition and ![]()

![]() Toggle

Toggle

![]()

![]() T0 Pin

T0 Pin

TH0 |

|

ENT0 (AUXR1.4) |

Figure 5-8: Timer/Counter 0 in Mode 6 (PWM auto-reload), P89LPC907.

TIMER OVERFLOW TOGGLE OUTPUT - P89LPC907

Timer 0 can be configured to automatically toggle the T0 pin whenever the timer overflow occurs. This function is enabled by control bit ENT0 in the AUXR1 register. The port output will be a logic 1 prior to the first timer overflow when this mode is turned on. In order for this mode to function, the T0C/T bit must be cleared selecting PCLK as the clock source for the timer.

2003 Dec 8 | 45 |