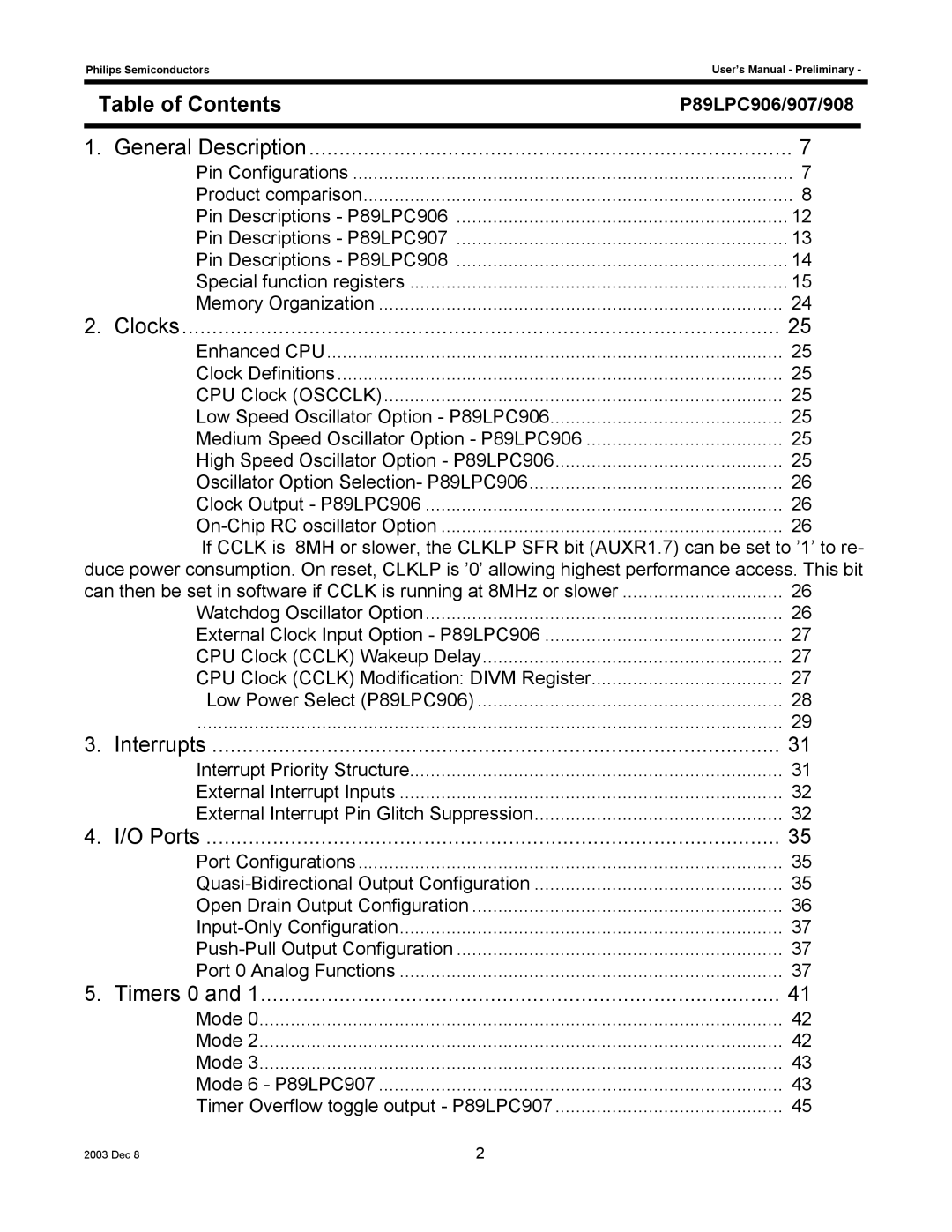

Philips Semiconductors | User’s Manual - Preliminary - | |

Table of Contents | P89LPC906/907/908 | |

1. | General Description | 7 |

| Pin Configurations | 7 |

| Product comparison | 8 |

| Pin Descriptions - P89LPC906 | 12 |

| Pin Descriptions - P89LPC907 | 13 |

| Pin Descriptions - P89LPC908 | 14 |

| Special function registers | 15 |

| Memory Organization | 24 |

2. | Clocks | 25 |

| Enhanced CPU | 25 |

| Clock Definitions | 25 |

| CPU Clock (OSCCLK) | 25 |

| Low Speed Oscillator Option - P89LPC906 | 25 |

| Medium Speed Oscillator Option - P89LPC906 | 25 |

| High Speed Oscillator Option - P89LPC906 | 25 |

| Oscillator Option Selection- P89LPC906 | 26 |

| Clock Output - P89LPC906 | 26 |

| 26 | |

| If CCLK is 8MH or slower, the CLKLP SFR bit (AUXR1.7) can be set to ’1’ to re- | |

duce power consumption. On reset, CLKLP is ’0’ allowing highest performance access. This bit | ||

can then be set in software if CCLK is running at 8MHz or slower | 26 | |

| Watchdog Oscillator Option | 26 |

| External Clock Input Option - P89LPC906 | 27 |

| CPU Clock (CCLK) Wakeup Delay | 27 |

| CPU Clock (CCLK) Modification: DIVM Register | 27 |

| Low Power Select (P89LPC906) | 28 |

| ................................................................................................................. | 29 |

3. | Interrupts | 31 |

| Interrupt Priority Structure | 31 |

| External Interrupt Inputs | 32 |

| External Interrupt Pin Glitch Suppression | 32 |

4. | I/O Ports | 35 |

| Port Configurations | 35 |

| 35 | |

| Open Drain Output Configuration | 36 |

| 37 | |

| 37 | |

| Port 0 Analog Functions | 37 |

5. Timers 0 and 1 | 41 | |

| Mode 0 | 42 |

| Mode 2 | 42 |

| Mode 3 | 43 |

| Mode 6 - P89LPC907 | 43 |

| Timer Overflow toggle output - P89LPC907 | 45 |

2003 Dec 8 | 2 |