Philips Semiconductors |

|

|

|

|

| User’s Manual - Preliminary - | ||

WATCHDOG TIMER |

|

|

| P89LPC906/907/908 | ||||

|

|

|

|

| WDL (C1H) |

|

| |

MOV WFEED1, #0A5H |

|

|

|

|

|

|

| |

MOV WFEED2, #05AH |

|

|

|

|

|

|

| |

Watchdog |

|

|

|

|

|

|

| |

Oscillator | ÷32 | PRESCALER |

|

|

| RESET | ||

PCLK |

|

|

|

| Counter |

| Watchdog reset can also be caused | |

|

|

|

|

|

|

| by an invalid feed sequence, or by | |

|

|

|

|

|

|

| writing to WDCON not immediately | |

|

|

|

|

|

|

| followed by a feed sequence | |

|

|

|

| control register |

|

|

| SHADOW |

|

|

|

|

|

|

| REGISTER FOR | |

|

|

|

|

|

|

|

| WDCON |

|

| PRE2 | PRE1 | PRE0 | WDRUN | WDTOF | WDCLK | WDCON(A7H) |

|

|

|

|

|

|

|

| |

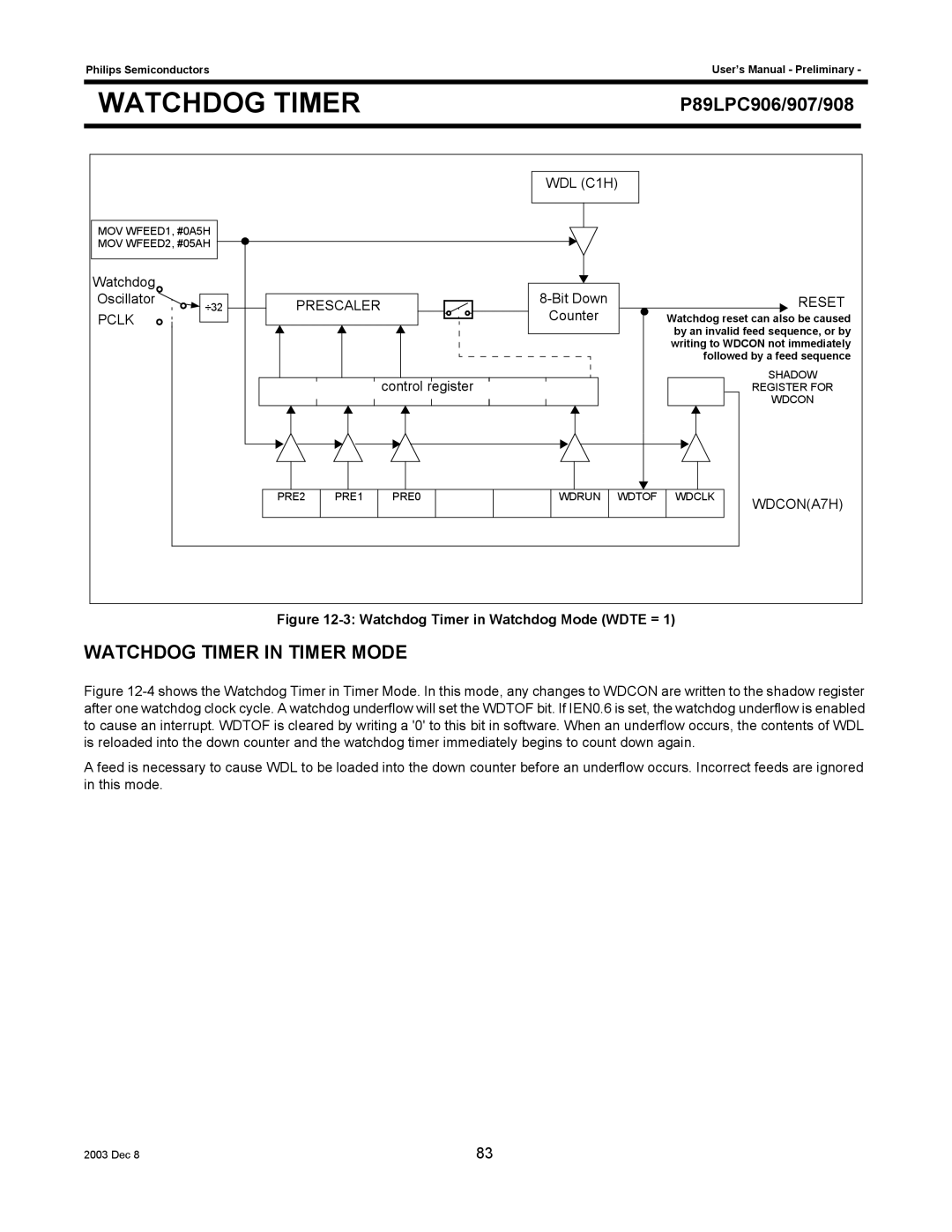

Figure 12-3: Watchdog Timer in Watchdog Mode (WDTE = 1)

WATCHDOG TIMER IN TIMER MODE

Figure 12-4 shows the Watchdog Timer in Timer Mode. In this mode, any changes to WDCON are written to the shadow register after one watchdog clock cycle. A watchdog underflow will set the WDTOF bit. If IEN0.6 is set, the watchdog underflow is enabled to cause an interrupt. WDTOF is cleared by writing a '0' to this bit in software. When an underflow occurs, the contents of WDL is reloaded into the down counter and the watchdog timer immediately begins to count down again.

A feed is necessary to cause WDL to be loaded into the down counter before an underflow occurs. Incorrect feeds are ignored in this mode.

2003 Dec 8 | 83 |