Philips Semiconductors | User’s Manual - Preliminary - | |

|

|

|

WATCHDOG TIMER | P89LPC906/907/908 | |

12. WATCHDOG TIMER |

|

|

The watchdog timer subsystem protects the system from incorrect code execution by causing a system reset when it underflows as a result of a failure of software to feed the timer prior to the timer reaching its terminal count. The watchdog timer can only be reset by a

WATCHDOG FUNCTION

The user has the ability using the WDCON and UCFG1 registers to control the run /stop condition of the WDT, the clock source for the WDT, the prescaler value, and whether the WDT is enabled to reset the device on underflow. In addition, there is a safety mechanism which forces the WDT to be enabled by values programmed into UCFG1 either through IAP or a commercial programmer.

The WDTE bit (UCFG1.7), if set, enables the WDT to reset the device on underflow. Following reset, the WDT will be running regardless of the state of the WDTE bit.

The WDRUN bit (WDCON.2) can be set to start the WDT and cleared to stop the WDT. Following reset this bit will be set and the WDT will be running. All writes to WDCON need to be followed by a feed sequence (see section "Feed Sequence" on page 80). Additional bits in WDCON allow the user to select the clocksource for the WDT and the prescaler.

When the timer is not enabled to reset the device on underflow, the WDT can be used in "timer mode" and be enabled to produce an interrupt (IEN0.6) if desired.

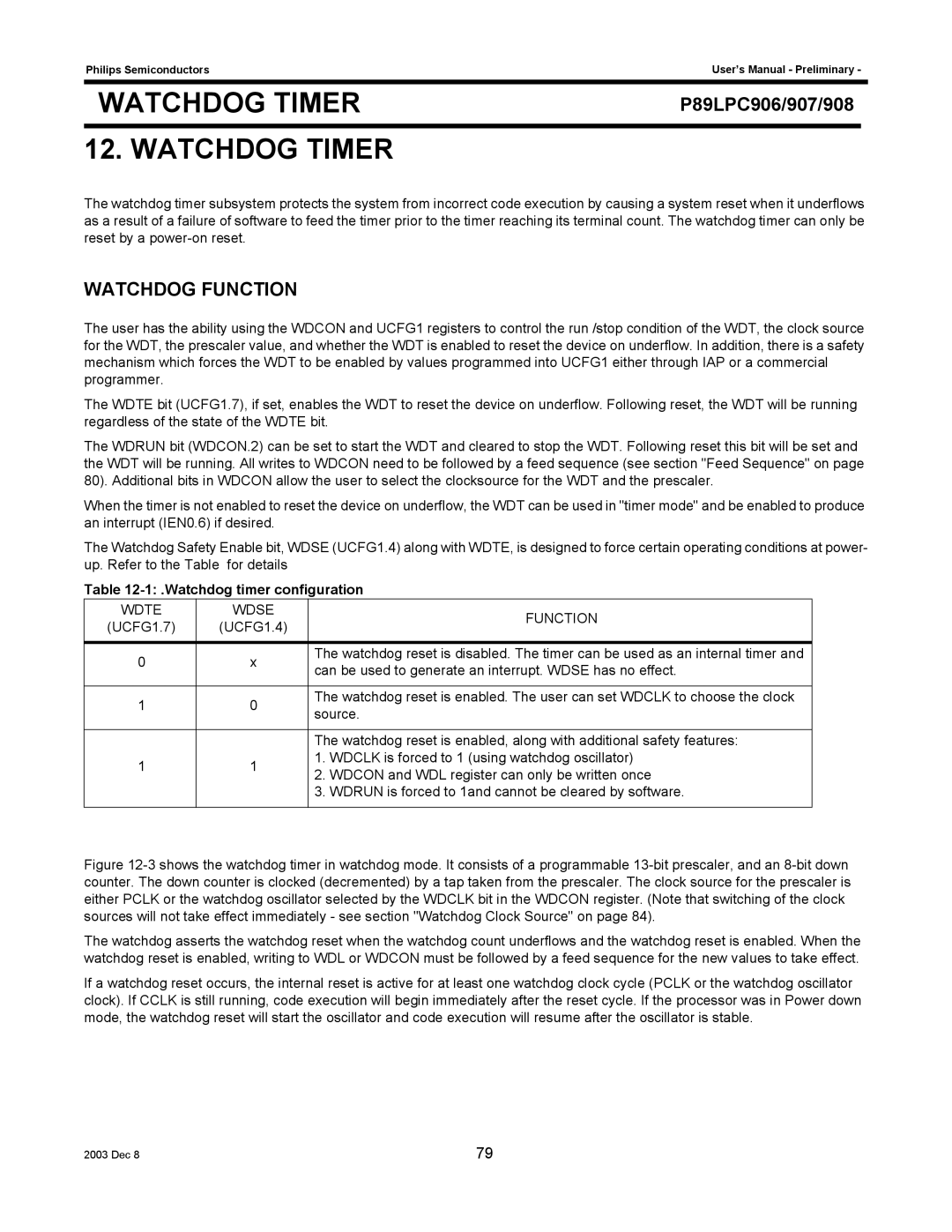

The Watchdog Safety Enable bit, WDSE (UCFG1.4) along with WDTE, is designed to force certain operating conditions at power- up. Refer to the Table for details

Table 12-1: .Watchdog timer configuration

WDTE | WDSE |

| FUNCTION | |

(UCFG1.7) | (UCFG1.4) |

| ||

|

| |||

|

|

| ||

0 | x | The watchdog reset is disabled. The timer can be used as an internal timer and | ||

can be used to generate an interrupt. WDSE has no effect. | ||||

|

| |||

|

|

| ||

1 | 0 | The watchdog reset is enabled. The user can set WDCLK to choose the clock | ||

source. | ||||

|

| |||

|

|

| ||

|

| The watchdog reset is enabled, along with additional safety features: | ||

1 | 1 | 1. | WDCLK is forced to 1 (using watchdog oscillator) | |

2. | WDCON and WDL register can only be written once | |||

|

| |||

|

| 3. | WDRUN is forced to 1and cannot be cleared by software. | |

|

|

|

| |

Figure 12-3 shows the watchdog timer in watchdog mode. It consists of a programmable 13-bit prescaler, and an 8-bit down counter. The down counter is clocked (decremented) by a tap taken from the prescaler. The clock source for the prescaler is either PCLK or the watchdog oscillator selected by the WDCLK bit in the WDCON register. (Note that switching of the clock sources will not take effect immediately - see section "Watchdog Clock Source" on page 84).

The watchdog asserts the watchdog reset when the watchdog count underflows and the watchdog reset is enabled. When the watchdog reset is enabled, writing to WDL or WDCON must be followed by a feed sequence for the new values to take effect.

If a watchdog reset occurs, the internal reset is active for at least one watchdog clock cycle (PCLK or the watchdog oscillator clock). If CCLK is still running, code execution will begin immediately after the reset cycle. If the processor was in Power down mode, the watchdog reset will start the oscillator and code execution will resume after the oscillator is stable.

2003 Dec 8 | 79 |