R

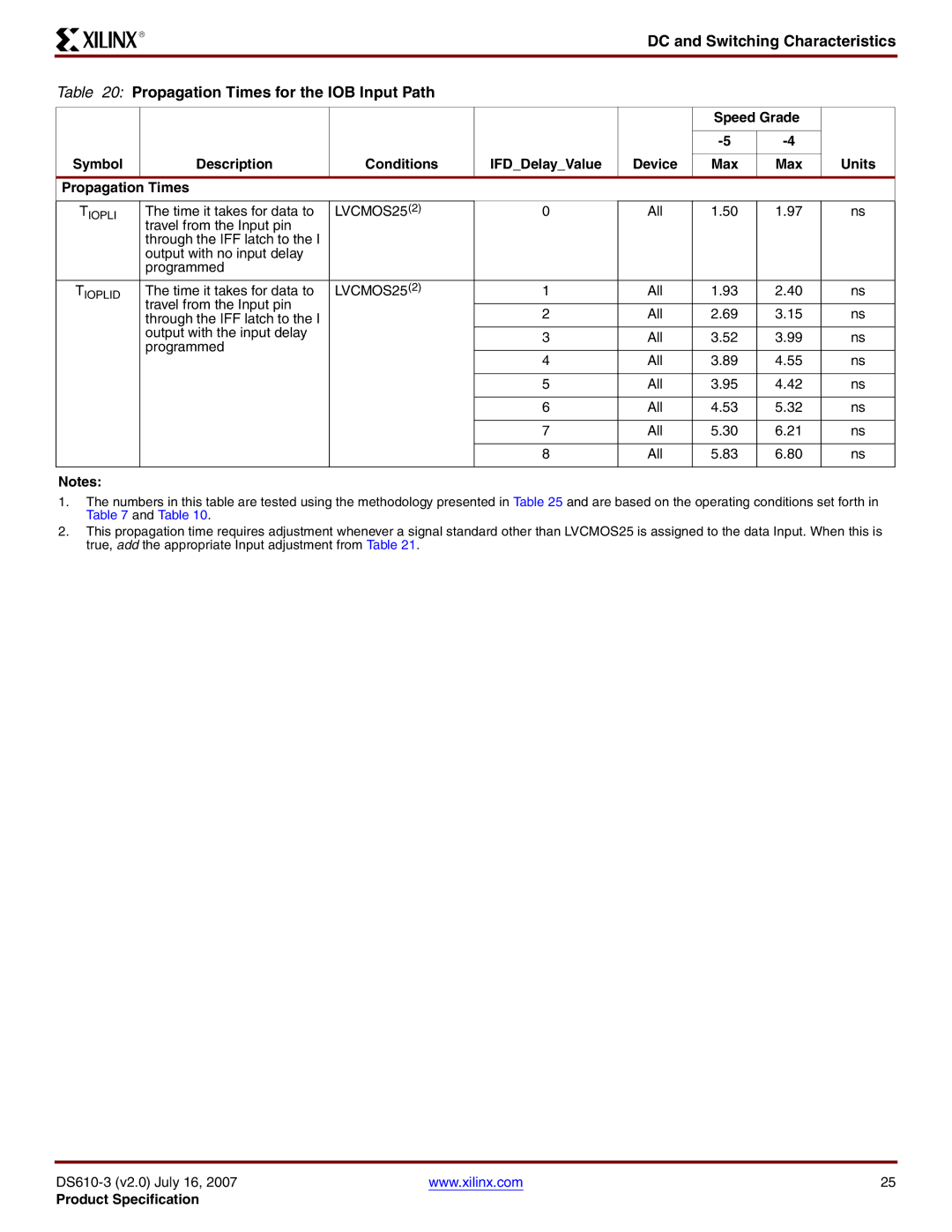

DC and Switching Characteristics

Table 20: Propagation Times for the IOB Input Path

|

|

|

|

| Speed Grade |

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

Symbol | Description | Conditions | IFD_Delay_Value | Device | Max | Max | Units |

Propagation Times |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

TIOPLI | The time it takes for data to | LVCMOS25(2) | 0 | All | 1.50 | 1.97 | ns |

| travel from the Input pin |

|

|

|

|

|

|

| through the IFF latch to the I |

|

|

|

|

|

|

| output with no input delay |

|

|

|

|

|

|

| programmed |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

T | The time it takes for data to | LVCMOS25(2) | 1 | All | 1.93 | 2.40 | ns |

IOPLID | travel from the Input pin |

|

|

|

|

|

|

|

| 2 | All | 2.69 | 3.15 | ns | |

| through the IFF latch to the I |

| |||||

| output with the input delay |

| 3 | All | 3.52 | 3.99 | ns |

| programmed |

| |||||

|

|

|

|

|

|

| |

|

| 4 | All | 3.89 | 4.55 | ns | |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| 5 | All | 3.95 | 4.42 | ns |

|

|

|

|

|

|

|

|

|

|

| 6 | All | 4.53 | 5.32 | ns |

|

|

|

|

|

|

|

|

|

|

| 7 | All | 5.30 | 6.21 | ns |

|

|

|

|

|

|

|

|

|

|

| 8 | All | 5.83 | 6.80 | ns |

|

|

|

|

|

|

|

|

Notes:

1.The numbers in this table are tested using the methodology presented in Table 25 and are based on the operating conditions set forth in Table 7 and Table 10.

2.This propagation time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. When this is true, add the appropriate Input adjustment from Table 21.

www.xilinx.com | 25 |

Product Specification