R

Product Specification | |

|

|

Introduction

The

The

Spartan-3A and Spartan-3A DSP FPGA Differences

The

Because of their exceptional DSP price/performance ratio,

The

Features

•Very low cost,

•250 MHz XtremeDSP DSP48A Slices

♦ Dedicated

♦Available pipeline stages for enhanced performance of at least 250 MHz in the standard

♦

♦Integration added for complex multiply or

♦Integrated

♦Optional cascaded Multiply or MAC

•Hierarchical SelectRAM™ memory architecture

♦Up to 2268 Kbits of fast block RAM with byte write enables for processor applications

♦Up to 373 Kbits of efficient distributed RAM

♦Registered outputs on the block RAM with operation of at least 280 MHz in the standard

•

•Suspend, Hibernate modes reduce system power

•

•

♦Up to 519 I/O pins or 227 differential signal pairs

♦LVCMOS, LVTTL, HSTL, and SSTL

♦3.3V, 2.5V, 1.8V, 1.5V, and 1.2V signaling

♦Selectable output drive, up to 24 mA per pin

♦QUIETIO standard reduces I/O switching noise

♦Full 3.3V ± 10% compatibility and hot swap compliance

♦622+ Mb/s data transfer rate per differential I/O

♦LVDS, RSDS,

♦Enhanced Double Data Rate (DDR) support

♦DDR/DDR2 SDRAM support up to 333 Mb/s

♦Fully compliant

•Abundant, flexible logic resources

♦Densities up to 53712 logic cells, including optional shift register

♦Efficient wide multiplexers, wide logic

♦Fast

♦IEEE 1149.1/1532 JTAG programming/debug port

•Eight Digital Clock Managers (DCMs)

♦Clock skew elimination (delay locked loop)

♦Frequency synthesis, multiplication, division

♦

♦Wide frequency range (5 MHz to over 320 MHz)

•Eight

•Configuration interface to

♦

♦x8 or x8/x16 parallel NOR Flash PROM

♦

♦Unique Device DNA identifier for design authentication

♦Load multiple bitstreams under FPGA control

•MicroBlaze™ and PicoBlaze™ embedded processor cores

•BGA and CSP packaging with

♦Common footprints support easy density migration

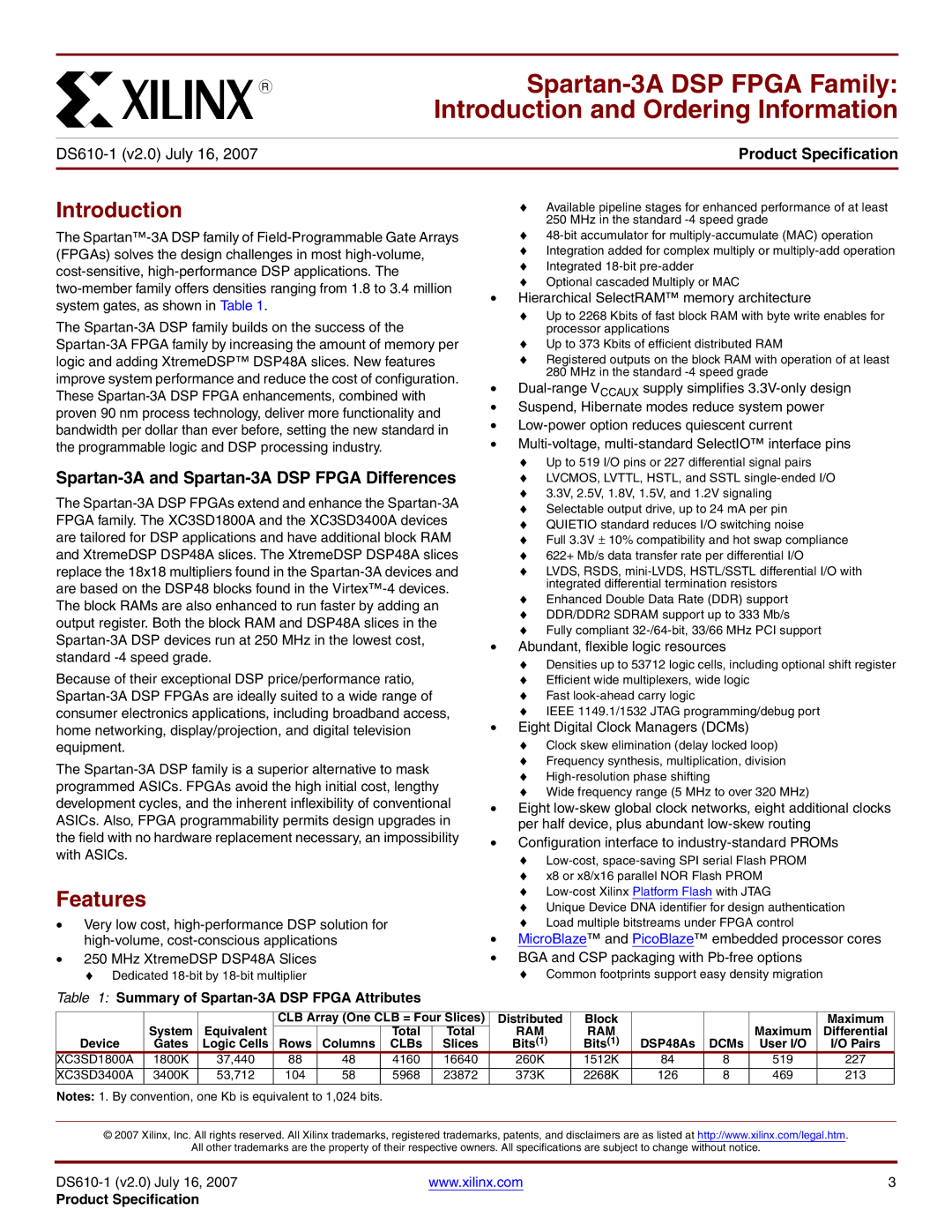

Table 1:

Device

|

| CLB Array (One CLB = Four Slices) | Distributed | |||

System | Equivalent |

|

| Total | Total | RAM |

Gates | Logic Cells | Rows | Columns | CLBs | Slices | Bits(1) |

Block

RAM

Bits(1)

|

|

| Maximum |

|

| Maximum | Differential |

DSP48As | DCMs | User I/O | I/O Pairs |

|

|

|

|

XC3SD1800A | 1800K | 37,440 | 88 | 48 | 4160 | 16640 | 260K | 1512K | 84 | 8 | 519 | 227 |

XC3SD3400A | 3400K | 53,712 | 104 | 58 | 5968 | 23872 | 373K | 2268K | 126 | 8 | 469 | 213 |

Notes: 1. By convention, one Kb is equivalent to 1,024 bits.

© 2007 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

All other trademarks are the property of their respective owners. All specifications are subject to change without notice.

www.xilinx.com | 3 |

Product Specification