R

DC and Switching Characteristics

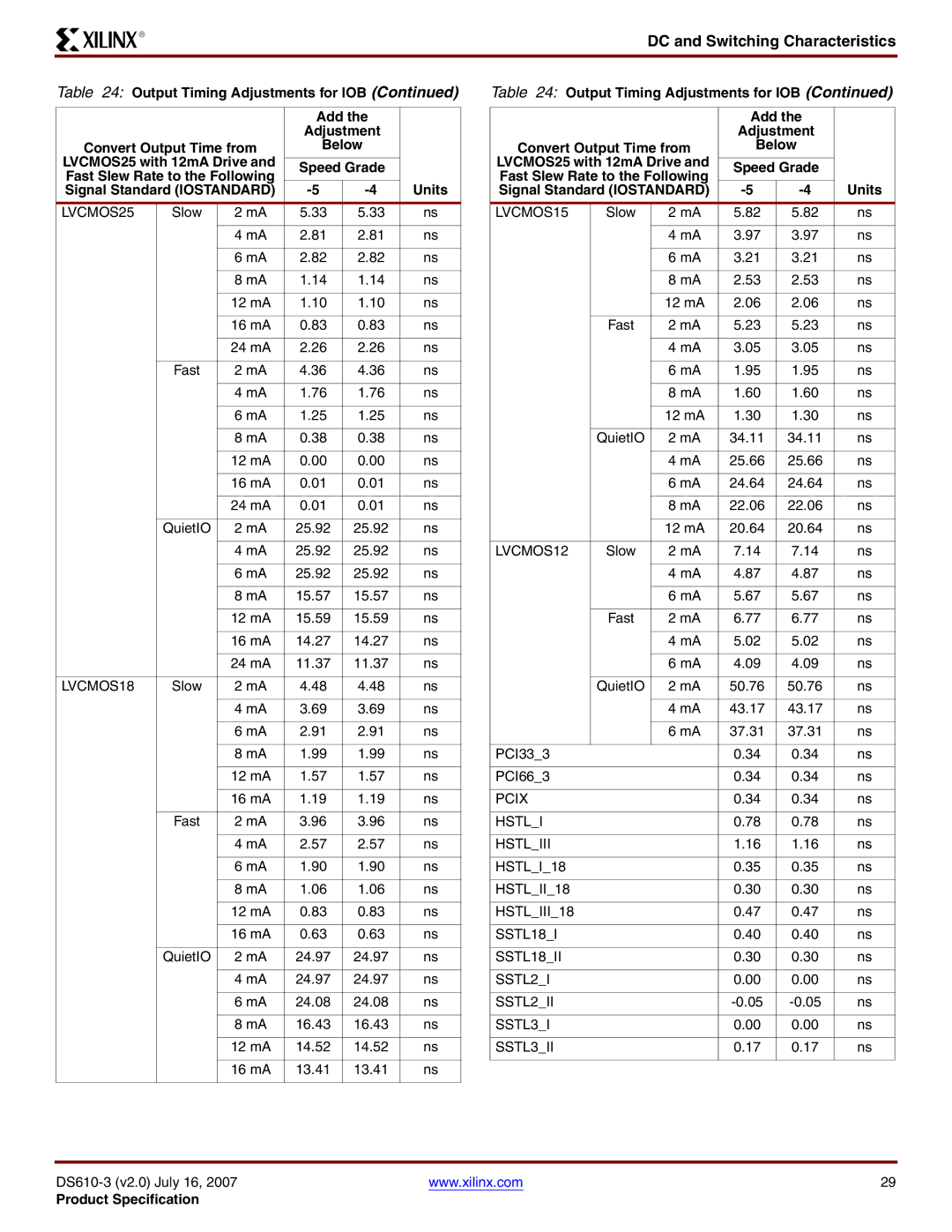

Table 24: Output Timing Adjustments for IOB (Continued)

|

|

| Add the |

| |

|

|

| Adjustment |

| |

Convert Output Time from | Below |

| |||

LVCMOS25 with 12mA Drive and |

|

|

| ||

Speed Grade |

| ||||

Fast Slew Rate to the Following |

| ||||

|

|

| |||

Signal Standard (IOSTANDARD) | Units | ||||

LVCMOS25 | Slow | 2 mA | 5.33 | 5.33 | ns |

|

|

|

|

|

|

|

| 4 mA | 2.81 | 2.81 | ns |

|

|

|

|

|

|

|

| 6 mA | 2.82 | 2.82 | ns |

|

|

|

|

|

|

|

| 8 mA | 1.14 | 1.14 | ns |

|

|

|

|

|

|

|

| 12 mA | 1.10 | 1.10 | ns |

|

|

|

|

|

|

|

| 16 mA | 0.83 | 0.83 | ns |

|

|

|

|

|

|

|

| 24 mA | 2.26 | 2.26 | ns |

|

|

|

|

|

|

| Fast | 2 mA | 4.36 | 4.36 | ns |

|

|

|

|

|

|

|

| 4 mA | 1.76 | 1.76 | ns |

|

|

|

|

|

|

|

| 6 mA | 1.25 | 1.25 | ns |

|

|

|

|

|

|

|

| 8 mA | 0.38 | 0.38 | ns |

|

|

|

|

|

|

|

| 12 mA | 0.00 | 0.00 | ns |

|

|

|

|

|

|

|

| 16 mA | 0.01 | 0.01 | ns |

|

|

|

|

|

|

|

| 24 mA | 0.01 | 0.01 | ns |

|

|

|

|

|

|

| QuietIO | 2 mA | 25.92 | 25.92 | ns |

|

|

|

|

|

|

|

| 4 mA | 25.92 | 25.92 | ns |

|

|

|

|

|

|

|

| 6 mA | 25.92 | 25.92 | ns |

|

|

|

|

|

|

|

| 8 mA | 15.57 | 15.57 | ns |

|

|

|

|

|

|

|

| 12 mA | 15.59 | 15.59 | ns |

|

|

|

|

|

|

|

| 16 mA | 14.27 | 14.27 | ns |

|

|

|

|

|

|

|

| 24 mA | 11.37 | 11.37 | ns |

|

|

|

|

|

|

LVCMOS18 | Slow | 2 mA | 4.48 | 4.48 | ns |

|

|

|

|

|

|

|

| 4 mA | 3.69 | 3.69 | ns |

|

|

|

|

|

|

|

| 6 mA | 2.91 | 2.91 | ns |

|

|

|

|

|

|

|

| 8 mA | 1.99 | 1.99 | ns |

|

|

|

|

|

|

|

| 12 mA | 1.57 | 1.57 | ns |

|

|

|

|

|

|

|

| 16 mA | 1.19 | 1.19 | ns |

|

|

|

|

|

|

| Fast | 2 mA | 3.96 | 3.96 | ns |

|

|

|

|

|

|

|

| 4 mA | 2.57 | 2.57 | ns |

|

|

|

|

|

|

|

| 6 mA | 1.90 | 1.90 | ns |

|

|

|

|

|

|

|

| 8 mA | 1.06 | 1.06 | ns |

|

|

|

|

|

|

|

| 12 mA | 0.83 | 0.83 | ns |

|

|

|

|

|

|

|

| 16 mA | 0.63 | 0.63 | ns |

|

|

|

|

|

|

| QuietIO | 2 mA | 24.97 | 24.97 | ns |

|

|

|

|

|

|

|

| 4 mA | 24.97 | 24.97 | ns |

|

|

|

|

|

|

|

| 6 mA | 24.08 | 24.08 | ns |

|

|

|

|

|

|

|

| 8 mA | 16.43 | 16.43 | ns |

|

|

|

|

|

|

|

| 12 mA | 14.52 | 14.52 | ns |

|

|

|

|

|

|

|

| 16 mA | 13.41 | 13.41 | ns |

|

|

|

|

|

|

Table 24: Output Timing Adjustments for IOB (Continued)

|

|

| Add the |

| |

|

|

| Adjustment |

| |

Convert Output Time from | Below |

| |||

LVCMOS25 with 12mA Drive and |

|

|

| ||

Speed Grade |

| ||||

Fast Slew Rate to the Following |

| ||||

|

|

| |||

Signal Standard (IOSTANDARD) | Units | ||||

LVCMOS15 | Slow | 2 mA | 5.82 | 5.82 | ns |

|

|

|

|

|

|

|

| 4 mA | 3.97 | 3.97 | ns |

|

|

|

|

|

|

|

| 6 mA | 3.21 | 3.21 | ns |

|

|

|

|

|

|

|

| 8 mA | 2.53 | 2.53 | ns |

|

|

|

|

|

|

|

| 12 mA | 2.06 | 2.06 | ns |

|

|

|

|

|

|

| Fast | 2 mA | 5.23 | 5.23 | ns |

|

|

|

|

|

|

|

| 4 mA | 3.05 | 3.05 | ns |

|

|

|

|

|

|

|

| 6 mA | 1.95 | 1.95 | ns |

|

|

|

|

|

|

|

| 8 mA | 1.60 | 1.60 | ns |

|

|

|

|

|

|

|

| 12 mA | 1.30 | 1.30 | ns |

|

|

|

|

|

|

| QuietIO | 2 mA | 34.11 | 34.11 | ns |

|

|

|

|

|

|

|

| 4 mA | 25.66 | 25.66 | ns |

|

|

|

|

|

|

|

| 6 mA | 24.64 | 24.64 | ns |

|

|

|

|

|

|

|

| 8 mA | 22.06 | 22.06 | ns |

|

|

|

|

|

|

|

| 12 mA | 20.64 | 20.64 | ns |

|

|

|

|

|

|

LVCMOS12 | Slow | 2 mA | 7.14 | 7.14 | ns |

|

|

|

|

|

|

|

| 4 mA | 4.87 | 4.87 | ns |

|

|

|

|

|

|

|

| 6 mA | 5.67 | 5.67 | ns |

|

|

|

|

|

|

| Fast | 2 mA | 6.77 | 6.77 | ns |

|

|

|

|

|

|

|

| 4 mA | 5.02 | 5.02 | ns |

|

|

|

|

|

|

|

| 6 mA | 4.09 | 4.09 | ns |

|

|

|

|

|

|

| QuietIO | 2 mA | 50.76 | 50.76 | ns |

|

|

|

|

|

|

|

| 4 mA | 43.17 | 43.17 | ns |

|

|

|

|

|

|

|

| 6 mA | 37.31 | 37.31 | ns |

|

|

|

|

|

|

PCI33_3 |

|

| 0.34 | 0.34 | ns |

|

|

|

|

|

|

PCI66_3 |

|

| 0.34 | 0.34 | ns |

|

|

|

|

|

|

PCIX |

|

| 0.34 | 0.34 | ns |

|

|

|

|

|

|

HSTL_I |

|

| 0.78 | 0.78 | ns |

|

|

|

|

|

|

HSTL_III |

|

| 1.16 | 1.16 | ns |

|

|

|

|

|

|

HSTL_I_18 |

|

| 0.35 | 0.35 | ns |

|

|

|

|

|

|

HSTL_II_18 |

|

| 0.30 | 0.30 | ns |

|

|

|

|

|

|

HSTL_III_18 |

|

| 0.47 | 0.47 | ns |

|

|

|

|

|

|

SSTL18_I |

|

| 0.40 | 0.40 | ns |

|

|

|

|

|

|

SSTL18_II |

|

| 0.30 | 0.30 | ns |

|

|

|

|

|

|

SSTL2_I |

|

| 0.00 | 0.00 | ns |

|

|

|

|

|

|

SSTL2_II |

|

| ns | ||

|

|

|

|

|

|

SSTL3_I |

|

| 0.00 | 0.00 | ns |

|

|

|

|

|

|

SSTL3_II |

|

| 0.17 | 0.17 | ns |

|

|

|

|

|

|

www.xilinx.com | 29 |

Product Specification