DC and Switching Characteristics

R

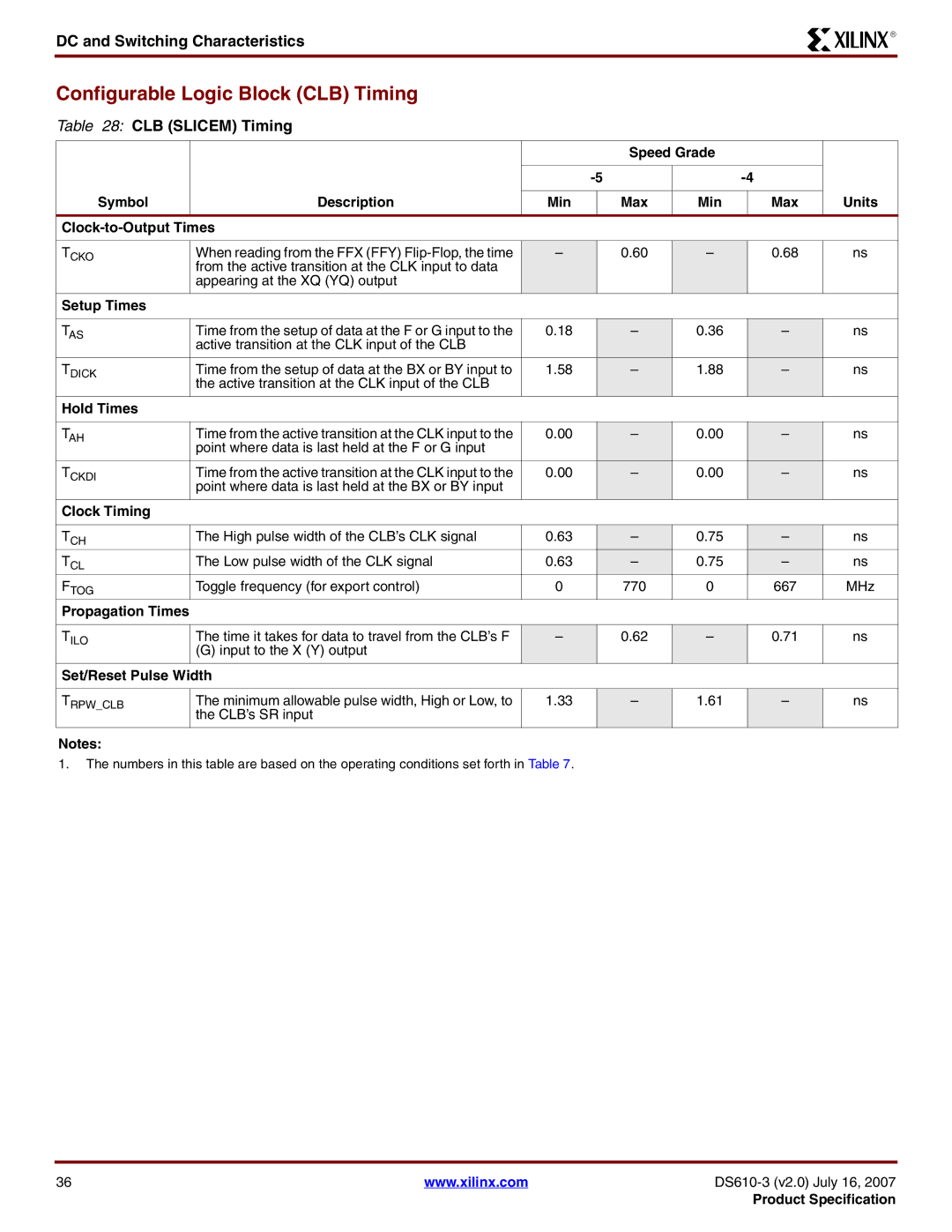

Configurable Logic Block (CLB) Timing

Table 28: CLB (SLICEM) Timing

|

|

|

| Speed Grade |

|

|

| |

|

|

|

|

|

|

|

| |

|

|

|

|

| ||||

|

|

|

|

|

|

|

| |

Symbol | Description | Min |

| Max | Min |

| Max | Units |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

TCKO | When reading from the FFX (FFY) | – |

| 0.60 | – |

| 0.68 | ns |

| from the active transition at the CLK input to data |

|

|

|

|

|

|

|

| appearing at the XQ (YQ) output |

|

|

|

|

|

|

|

Setup Times |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TAS | Time from the setup of data at the F or G input to the | 0.18 |

| – | 0.36 |

| – | ns |

| active transition at the CLK input of the CLB |

|

|

|

|

|

|

|

TDICK | Time from the setup of data at the BX or BY input to | 1.58 |

| – | 1.88 |

| – | ns |

| the active transition at the CLK input of the CLB |

|

|

|

|

|

|

|

Hold Times |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TAH | Time from the active transition at the CLK input to the | 0.00 |

| – | 0.00 |

| – | ns |

| point where data is last held at the F or G input |

|

|

|

|

|

|

|

TCKDI | Time from the active transition at the CLK input to the | 0.00 |

| – | 0.00 |

| – | ns |

| point where data is last held at the BX or BY input |

|

|

|

|

|

|

|

Clock Timing |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TCH | The High pulse width of the CLB’s CLK signal | 0.63 |

| – | 0.75 |

| – | ns |

TCL | The Low pulse width of the CLK signal | 0.63 |

| – | 0.75 |

| – | ns |

FTOG | Toggle frequency (for export control) | 0 |

| 770 | 0 |

| 667 | MHz |

Propagation Times |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TILO | The time it takes for data to travel from the CLB’s F | – |

| 0.62 | – |

| 0.71 | ns |

| (G) input to the X (Y) output |

|

|

|

|

|

|

|

Set/Reset Pulse Width |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

TRPW_CLB | The minimum allowable pulse width, High or Low, to | 1.33 |

| – | 1.61 |

| – | ns |

| the CLB’s SR input |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Notes:

1.The numbers in this table are based on the operating conditions set forth in Table 7.

36 | www.xilinx.com | |

|

| Product Specification |