Pinout Descriptions

R

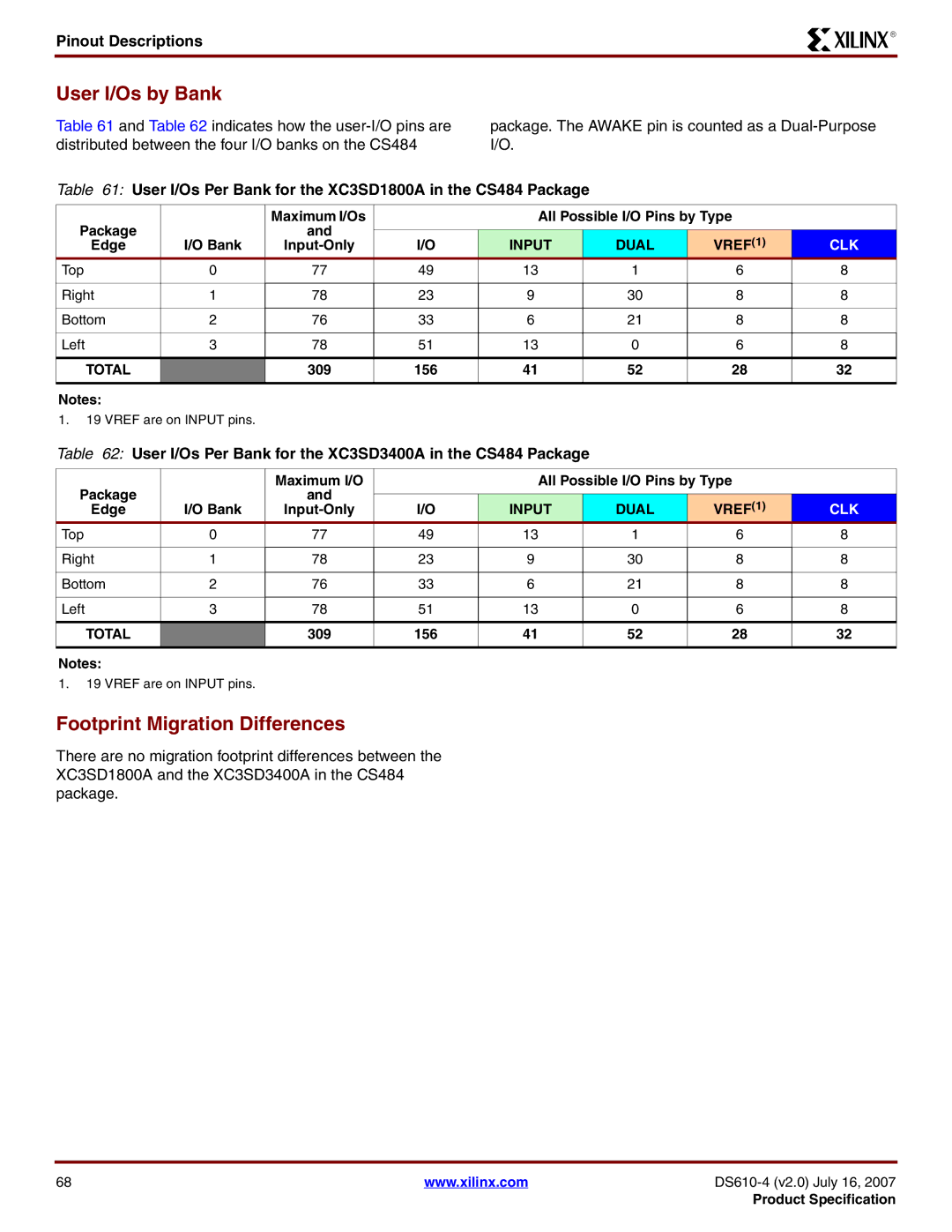

User I/Os by Bank

Table 61 and Table 62 indicates how the

package. The AWAKE pin is counted as a

Table 61: User I/Os Per Bank for the XC3SD1800A in the CS484 Package

Package |

| Maximum I/Os |

| All Possible I/O Pins by Type |

| |||

| and |

|

|

|

|

| ||

I/O Bank | I/O | INPUT | DUAL | VREF(1) | CLK | |||

Edge |

| |||||||

Top | 0 | 77 | 49 | 13 | 1 | 6 | 8 | |

|

|

|

|

|

|

|

| |

Right | 1 | 78 | 23 | 9 | 30 | 8 | 8 | |

|

|

|

|

|

|

|

| |

Bottom | 2 | 76 | 33 | 6 | 21 | 8 | 8 | |

|

|

|

|

|

|

|

| |

Left | 3 | 78 | 51 | 13 | 0 | 6 | 8 | |

|

|

|

|

|

|

|

| |

TOTAL |

| 309 | 156 | 41 | 52 | 28 | 32 | |

|

|

|

|

|

|

|

| |

Notes:

1.19 VREF are on INPUT pins.

Table 62: User I/Os Per Bank for the XC3SD3400A in the CS484 Package

Package |

| Maximum I/O |

| All Possible I/O Pins by Type |

| |||

| and |

|

|

|

|

| ||

I/O Bank | I/O | INPUT | DUAL | VREF(1) | CLK | |||

Edge |

| |||||||

Top | 0 | 77 | 49 | 13 | 1 | 6 | 8 | |

|

|

|

|

|

|

|

| |

Right | 1 | 78 | 23 | 9 | 30 | 8 | 8 | |

|

|

|

|

|

|

|

| |

Bottom | 2 | 76 | 33 | 6 | 21 | 8 | 8 | |

|

|

|

|

|

|

|

| |

Left | 3 | 78 | 51 | 13 | 0 | 6 | 8 | |

|

|

|

|

|

|

|

| |

TOTAL |

| 309 | 156 | 41 | 52 | 28 | 32 | |

|

|

|

|

|

|

|

| |

Notes:

1.19 VREF are on INPUT pins.

Footprint Migration Differences

There are no migration footprint differences between the XC3SD1800A and the XC3SD3400A in the CS484 package.

68 | www.xilinx.com | |

|

| Product Specification |