Pinout Descriptions

CS484: 484-Ball Chip-Scale Ball Grid Array

R

The

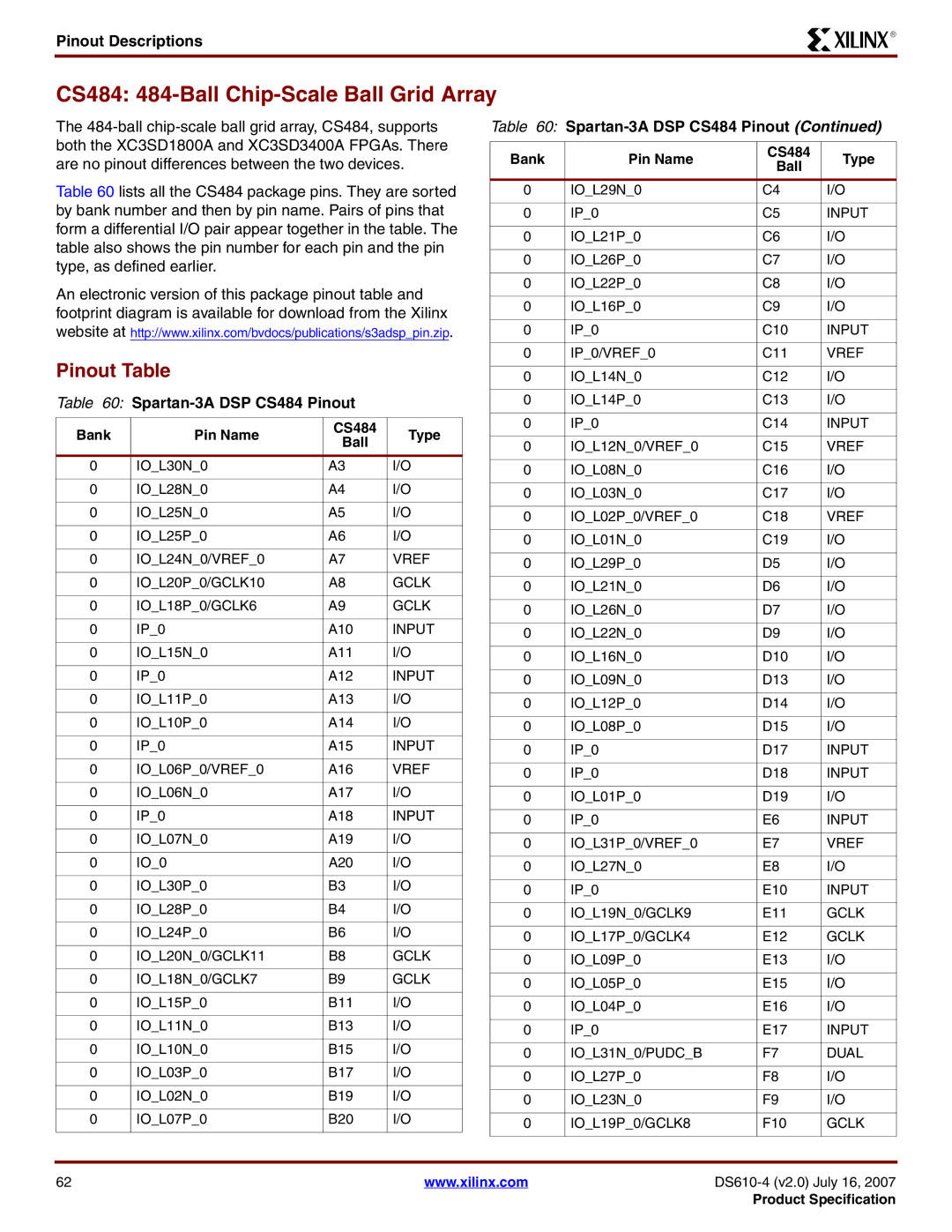

Table 60 lists all the CS484 package pins. They are sorted by bank number and then by pin name. Pairs of pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx website at http://www.xilinx.com/bvdocs/publications/s3adsp_pin.zip.

Pinout Table

Table 60: Spartan-3A DSP CS484 Pinout

Bank | Pin Name | CS484 | Type | |

Ball | ||||

|

|

| ||

0 | IO_L30N_0 | A3 | I/O | |

|

|

|

| |

0 | IO_L28N_0 | A4 | I/O | |

|

|

|

| |

0 | IO_L25N_0 | A5 | I/O | |

|

|

|

| |

0 | IO_L25P_0 | A6 | I/O | |

|

|

|

| |

0 | IO_L24N_0/VREF_0 | A7 | VREF | |

|

|

|

| |

0 | IO_L20P_0/GCLK10 | A8 | GCLK | |

|

|

|

| |

0 | IO_L18P_0/GCLK6 | A9 | GCLK | |

|

|

|

| |

0 | IP_0 | A10 | INPUT | |

|

|

|

| |

0 | IO_L15N_0 | A11 | I/O | |

|

|

|

| |

0 | IP_0 | A12 | INPUT | |

|

|

|

| |

0 | IO_L11P_0 | A13 | I/O | |

|

|

|

| |

0 | IO_L10P_0 | A14 | I/O | |

|

|

|

| |

0 | IP_0 | A15 | INPUT | |

|

|

|

| |

0 | IO_L06P_0/VREF_0 | A16 | VREF | |

|

|

|

| |

0 | IO_L06N_0 | A17 | I/O | |

|

|

|

| |

0 | IP_0 | A18 | INPUT | |

|

|

|

| |

0 | IO_L07N_0 | A19 | I/O | |

|

|

|

| |

0 | IO_0 | A20 | I/O | |

|

|

|

| |

0 | IO_L30P_0 | B3 | I/O | |

|

|

|

| |

0 | IO_L28P_0 | B4 | I/O | |

|

|

|

| |

0 | IO_L24P_0 | B6 | I/O | |

|

|

|

| |

0 | IO_L20N_0/GCLK11 | B8 | GCLK | |

|

|

|

| |

0 | IO_L18N_0/GCLK7 | B9 | GCLK | |

|

|

|

| |

0 | IO_L15P_0 | B11 | I/O | |

|

|

|

| |

0 | IO_L11N_0 | B13 | I/O | |

|

|

|

| |

0 | IO_L10N_0 | B15 | I/O | |

|

|

|

| |

0 | IO_L03P_0 | B17 | I/O | |

|

|

|

| |

0 | IO_L02N_0 | B19 | I/O | |

|

|

|

| |

0 | IO_L07P_0 | B20 | I/O | |

|

|

|

|

Table 60:

Bank | Pin Name | CS484 | Type | |

Ball | ||||

|

|

| ||

0 | IO_L29N_0 | C4 | I/O | |

|

|

|

| |

0 | IP_0 | C5 | INPUT | |

|

|

|

| |

0 | IO_L21P_0 | C6 | I/O | |

|

|

|

| |

0 | IO_L26P_0 | C7 | I/O | |

|

|

|

| |

0 | IO_L22P_0 | C8 | I/O | |

|

|

|

| |

0 | IO_L16P_0 | C9 | I/O | |

|

|

|

| |

0 | IP_0 | C10 | INPUT | |

|

|

|

| |

0 | IP_0/VREF_0 | C11 | VREF | |

|

|

|

| |

0 | IO_L14N_0 | C12 | I/O | |

|

|

|

| |

0 | IO_L14P_0 | C13 | I/O | |

|

|

|

| |

0 | IP_0 | C14 | INPUT | |

|

|

|

| |

0 | IO_L12N_0/VREF_0 | C15 | VREF | |

|

|

|

| |

0 | IO_L08N_0 | C16 | I/O | |

|

|

|

| |

0 | IO_L03N_0 | C17 | I/O | |

|

|

|

| |

0 | IO_L02P_0/VREF_0 | C18 | VREF | |

|

|

|

| |

0 | IO_L01N_0 | C19 | I/O | |

|

|

|

| |

0 | IO_L29P_0 | D5 | I/O | |

|

|

|

| |

0 | IO_L21N_0 | D6 | I/O | |

|

|

|

| |

0 | IO_L26N_0 | D7 | I/O | |

|

|

|

| |

0 | IO_L22N_0 | D9 | I/O | |

|

|

|

| |

0 | IO_L16N_0 | D10 | I/O | |

|

|

|

| |

0 | IO_L09N_0 | D13 | I/O | |

|

|

|

| |

0 | IO_L12P_0 | D14 | I/O | |

|

|

|

| |

0 | IO_L08P_0 | D15 | I/O | |

|

|

|

| |

0 | IP_0 | D17 | INPUT | |

|

|

|

| |

0 | IP_0 | D18 | INPUT | |

|

|

|

| |

0 | IO_L01P_0 | D19 | I/O | |

|

|

|

| |

0 | IP_0 | E6 | INPUT | |

|

|

|

| |

0 | IO_L31P_0/VREF_0 | E7 | VREF | |

|

|

|

| |

0 | IO_L27N_0 | E8 | I/O | |

|

|

|

| |

0 | IP_0 | E10 | INPUT | |

|

|

|

| |

0 | IO_L19N_0/GCLK9 | E11 | GCLK | |

|

|

|

| |

0 | IO_L17P_0/GCLK4 | E12 | GCLK | |

|

|

|

| |

0 | IO_L09P_0 | E13 | I/O | |

|

|

|

| |

0 | IO_L05P_0 | E15 | I/O | |

|

|

|

| |

0 | IO_L04P_0 | E16 | I/O | |

|

|

|

| |

0 | IP_0 | E17 | INPUT | |

|

|

|

| |

0 | IO_L31N_0/PUDC_B | F7 | DUAL | |

|

|

|

| |

0 | IO_L27P_0 | F8 | I/O | |

|

|

|

| |

0 | IO_L23N_0 | F9 | I/O | |

|

|

|

| |

0 | IO_L19P_0/GCLK8 | F10 | GCLK | |

|

|

|

|

62 | www.xilinx.com | |

|

| Product Specification |