Corporate Headquarters

Copyright 2001, Cisco Systems, Inc All rights reserved

General Information

Document Information

Mailing Information

Business Reply Mail

N T E N T S

Cell Bus

Module Requirements with Bulk Distribution and Redundancy

Wiring a Mixed Ground System with Redundant Supplies

Other Ports

Card and Service Configuration

Configuring Logical Interfaces for the Feeder

Features

FRSM-2CT3 Framer

Technical Specifications

ATM UNI

Xiv

G U R E S

Figure B-1

B L E S

Table A-1

Table A-33

Release 1.1.31, Part Number 78-11215-03 Rev. B0, May

Audience

Organization

This document is organized into the following chapters

Documentation Description

Related Documentation

Cisco WAN Manager, Release 10, Related Documentation

Xxiv

Conventions

World Wide Web

Obtaining Documentation

Documentation CD-ROM

Ordering Documentation

Obtaining Technical Assistance

To access Cisco.com, go to the following website

Documentation Feedback

Cisco.com

Contacting TAC by Using the Cisco TAC Website

Technical Assistance Center

Contacting TAC by Telephone

Xxviii

A P T E R

Introducing the MGX

MGX 8230 with Door Attached

MGX 8230 System Overview

Universal Edge Architecture

Applications of the MGX

MGX 8230 Enclosure and Power

Slot Numbering and Placement

Standards-Based Conversion to ATM

PXM

Single Height and Double Height Slots

Optional AC Power Supply

MGX 8230 Power System

AC Power Supply Module, Rear View

DC-Powered MGX

Cooling System

MGX 8230 DC Power Entry Module

MGX 8230 Architecture

MGX 8230 Fan Tray Assembly

PXM-UI

Cell Bus

Cell Bus Distribution

MGX 8230 Management

Introduction to Core Card Sets and Service Modules

Processor Switching Module PXM1

Summary of MGX 8230 Cards and Modules

User Interface Back Cards

MGX-BNC-2T3

MGX-BNC-2E3

Service Resource Module SRM

Frame Relay Service Modules Frsm

ATM UNI Service Modules Ausm

Circuit Emulation Service Modules Cesm

Voice Service Modules Vism

Route Processor Module RPM

Redundancy

Redundancy for Service Modules

Hot Standby

1N Redundancy

Introducing the MGX Summary of MGX 8230 Cards and Modules

Release 1.1.31, Part Number 78-11215-03 Rev. B0, May

Processor Switching Module

Module and Service Descriptions

PXM1 Illustration and LED Description

PXM1 Features

PXM1-UI standard

PXM1 User Interface Back Cards

Making External Clock Connections

Maintenance, Control and LAN ports

PXM-UI-S3 optional

Stratum 4 clocking

PXM1 User Interface Back Cards

PXM1 Back Cards

User Interface Back Card PXM-UI-S3 Stratum 3 Clocking

Alarm Output Connection

OC-12 Long-Reach Back Card SMFLR-1-622/B

SMFLR-1-622 Back Card

OC-12 Intermediate-Reach Back Card SMFIR-1-622/B

SMFIR-1-622 Back Card

OC-3 Four-Port Back Card SMF-155/B

SMF-155 Back Card

Two-port T3 Back Card BNC-2T3

BNC-2T3 Back Card

Two-port E3 Back Card BNC-2E3

BNC-2E3 Back Card

Bit Error Rate Testing

Service Resource Module

1N Service Module Redundancy

Bulk Distribution Mode

SRM Illustration and LED Indicators

Installation Requirements for the MGX-SRM-3T3/C

Module Requirements with Bulk Distribution and Redundancy

Type of LED Color Meaning

MGX-SRM-3T3/C Card Set

Ausm Features

ATM UNI Service Module Ausm

Quality of Service QoS Management

Inverse Multiplexing

All Cards

Physical Layer Features

T1 Cards

E1 Cards

10 AUSM/B-8T1 or AUSM/B-8E1 Front Card

Ausm Front Card Illustration and LED Description

Type of LED Color Description

Back Cards for the AUSM/B

11 RJ-48 and SMB Back Cards for the MGX-AUSM-8T1E1/B

Features Common to All FRSMs

Frame Relay Service Modules

Data-Link Layer features

Frame Relay features

Frame Forwarding Features

ATM Funi features

Connection Types on the Frsm

Redundancy for Frame Service Modules

Frame Relay-to-ATM Network Interworking

Congestion Indication for NIW Connections

Congestion Indication

Frame Relay-to-ATM Service Interworking

PVC Status Management

Efci is always set to

Cell Loss Priority

Frame Forwarding

Command and Response Mapping

ATM Frame-to-User Network Interface

Translation and Transparent Modes

Frsm for T1 features

Types of Frame Service Modules

FRSMs for T1 and E1 Lines

There are three types of FRSMs

LED Indicators

Frsm for E1 features

ACT LED

Stby LED

Card Illustrations

14 MGX-FRSM-8T1

15 RJ-48 and SMB Back Cards for the MGX-FRSM-8T1/E1

FRSMs for T3 and E3 lines

Features

6and -7describe the FRSM-2T3E3 LED faceplate indicators

FRSM-2T3E3 LED Indicators

Card Combinations

Illustrations

16 MGX-FRSM-2CT3

17 MGX-FRSM-2T3E3

18 BNC-2T3

19 BNC-2E3

FRSM-HS1/B X.21 and V.35 Interfaces

FRSMs for Serial Connections

FRSM-HS2 Hssi Interfaces

For the MGX-FRSM-HS2 front card, see -20 on

MGX-FRSM-HS1/B Cabling

Mode Type of Cable Clock Source Mode of Far End

Cable Type

DCE

Type of Cable Far End Connector Part Number

Dtest DTE

DTE-DCE

20 MGX-FRSM-HS2

21 MGX-FRSM-HS1/B Front Card Faceplate

22 SCSI2-2HSSI

23 12IN1 S4 Back Card Faceplate

Circuit Emulation Service Modules

Cesm T1 and E1 Features

Cesm for T1 and E1 lines

1N Redundancy for the Cesm T1/E1

LED Indicators for the Eight-Port Cesm

Cesm T1/E1 Illustrations

AX-SMB-8E1-LM

Fail LED

24 Front Cards for the Eight-Port Cesm

25 RJ-48 and SMB Back Cards for the MGX-CESM-8T1E1

CESM-T3/E3 Features

Cesm for T3 and E3 lines

T3 Interfaces

E3 Interfaces

MGX-CESM-T3/E3 front card is shown in -26 on

Cesm T3/E3 Illustrations

27 BNC-2T3 Back Card for the CESM-T3/E3

28 BNC-2E3 Back Card for the CESM-T3/E3

Voice Service The Vism

Summary of Features Supported with Vism

Vism Documentation

T3 Interfaces via SRM Bulk Distribution

Card Combinations

Vism Redundancy

Vism Card Illustrations and LED Description

29 Vism Front Cards

30 Vism Back Cards

RPM Documentation

Route Processor Module RPM

Release 1.1.31, Part Number 78-11215-03 Rev. B0, May

Parts Checklist

Site Preparation

Environment Operating environment should be as follows

Site Preparation

Regulatory Compliance and Safety Information

Maintaining Safety with Electricity

Safety Recommendations

Site Preparation Maintaining Safety with Electricity

Product Disposal Warning

Site Preparation Maintaining Safety with Electricity

Lightning Activity Warning

Jewelry Removal Warning

Power Supply Warning

Power Supply Disconnection Warning

Power Disconnection Warning

Grounded Equipment Warning

Installation Warning

Class 1 Laser Product Warning

Laser Beam Warning

Seismic Anchoring for a Cisco Rack

Seismic Considerations

Stability Plate Dimensions

Installing a Cisco Cabinet Over the Stability Plate

AC Power Circuit Breakers

Power and Grounding

DC Power Circuit Breakers

Electrical Power for AC-Powered Nodes

Bonding and Grounding

Wiring a Mixed Ground System with Redundant Supplies

Connection Description

DC Current Distance in Feet

Co-Locating Cisco Units in the Same Rack

Using the Electrostatic Wrist Strap

Making the Frame Bonding Ground Connection

Gauge Ohms per 1000 Feet

Making Cisco Cabinet Ground Connections

Frame Bonding Connection in Cisco-Supplied Rack

Release 1.1.31, Part Number 78-11215-03 Rev. B0, May

Mechanical Lift Guidelines

Chapter Summary

Installing a Stand-Alone MGX

If the switch is a stand-alone unit, proceed directly to

Rack Mounting an MGX

Prepare for Rack Installation

Bracket Placement

Rack Positioning

Mounting Kits

17273

Install the MGX 8230 Using a Mechanical Lift Recommended

Rack Mounting Procedures for 19-Inch Racks Mechanical Lift

Rack Mounting Procedures for 23-Inch Racks Mechanical Lift

Prepare for Installation

Install the MGX 8230 Without a Mechanical Lift Optional

Remove the Front Cards

To remove a front card

Rack Mount the MGX 8230 chassis

Remove the Back Cards

Inch rack mounting

Follow these steps to mount an MGX 8230 in a 19-inch rack

Front View of MGX 8230 with 23-Inch Mid-Mounting Brackets

Re-install the back cards

Re-install the front cards

Rear View of MGX 8230 with Two DC PEMs

Connecting Power for DC Systems

Rear View of MGX 8230 with 1 DC PEM

Polarities at MGX 8230 PEM Pluggable Terminal Block

DC PEM

11 Optional 1200 Watt AC Power Supply Module, Rear View

Connecting Power for AC Systems

Making the Connections to the AC Power Supply Modules

23825

13 Rear View of MGX 8230 with One AC Power Supply Module

Install the Cable Manager

14 Cable Management System on Rack-Mount MGX

Power up the MGX

Configuring the MGX 8230 as an BPX Feeder

Release 1.1.31, Part Number 78-11215-03 Rev. B0, May

Word bay refers to the upper or lower half of the enclosure

Summary of Shelf-Level Tasks

Ethernet port Maintenance port

User Interface Access Ports

Control Port

Ethernet Port

MGX 8230 MGX to BPX Feeder

Maintenance Port

Initial MGX 8230 Bring-Up

Other Ports

Inet on ethernet e 188.29.37.14ffffff00

Bringing Up an MGX 8230 PXM With No Run-time Firmware

Bin

Configuring Node-Level Parameters

Resource Partitioning

Enter the following

Nodename.1.slot.cardtype.a

Procedure

Cnfpasswd username

Adduser userId accessLevel

Downloading Firmware to a Service Module

$tftp IP address

Then

Configuring the OC-3 Uplink

MGX 8230 CLI Configuration of a Feeder

Addport portnum linenum pctbw minvpi maxvpi

Commands are cnfport, dspports, and delport

Cnfifastrk slot.port trunk

Establishing the BPX 8600-to-BPX 8600 Series Segment

Selecting an MGX

CiscoView Configuration of a Feeder

Activating a Physical Line for the Uplink

Specifying the Feeder Application

Configuring Logical Interfaces for the Feeder

Partitioning Resources on the Broadband Interface

Configuring the Line as a Feeder Trunk

Modifying the Resource Partitioning

Connections on a Feeder

Sequence of Configuration Tasks

Rules for Adding Connections

Rules for Adding a DAX Connection

Rules for Adding Three-Segment Connections

Frame Relay Connection Through an MGX 8230/BPX Network

Clock Sources

Configuring Synchronization for the Shelf

Configuration Example

Clock Source Configuration

Clock Source Types

Clock types are primary, secondary, and tertiary

For an internal clock source

Configuring PXM1 Card-Level Parameters, Lines, and Ports

Cnfextclk ClockType Impedance

Cnfcdrscprtn numberPARconns numberPNNIconns numberTAGconns

Cnfatmln linenum type

Automatic Protection Switching on the PXM1

APS Configuration

APS Requirements

Adding Connections on a PXM1 in a Stand-Alone Node

Cnfcon connID routepriority maxcost restricttrunktype CAC

ATM Forum TM spec PCR Flow

PolType =3

VBR.3

PolType =4

PolType =5

Summary of Ausm Features

ATM Universal Service Module Ausm

Cnfportq portnum qnum qalgo qdepth clphigh clplow efcithres

Configure the Card, Lines, and Ports

=CBR =VBR =ABR =UBR

Configure Inverse Multiplexing

Adding and Configuring Connections on the AUSM/B

Addimagrp groupnum porttype listoflinks minNumLink

Port number is in the range

Release 1.1.31, Part Number 78-11215-03 Rev. B0, May

Cnfchanfst port.vpi.vci enable fgcraenable ibs pcr mcr icr

Release 1.1.31, Part Number 78-11215-03 Rev. B0, May

If necessary, change the queue depths by using cnfchanq

Variable Description Value range Default value

BPX 8600-to-BPX 8600 Segment

Frame Service Module Features

Summary of Frame Service Module Features

MGX-FRSM-2T3E3 Features

MGX-FRSM-2CT3 Features

MGX-FRSM-HS1/B Features

MGX-FRSM-HS2 Features

Eight-Port Frsm Features

Configuring Frame Relay Service

Configuring the Frsm Cards, Lines, and Ports

Cnfln linenum linetype linerate

Correspond to Line Rates in Kbps

Addport portnum linenum ds0speed beginslot numslot porttype

Addport portnum linenum porttype

Cnfport portnum lmisig asyn elmi T391 T392 N391 N392 N393

Addport portnum porttype

Adding a Frame Relay Connection

Release 1.1.31, Part Number 78-11215-03 Rev. B0, May

Service Type Default EgressQueue PXM1 Service Type

Cnfchanmap channum chanType FECN/EFCI DE to CLP CLP to DE

CIR

Establishing the BPX 8600-to-BPX 8600 Series Segment

Test Commands for the FRSMs

Bit Error Rate Testing on an Unchannelized T3 or E3 Frsm

Support for Alarm Reporting

Circuit Emulation Service Module for T3 and E3

Features

Cell Delay Treatment

Error and Alarm Response

Configuring Service on a T3 or E3 Cesm

Alarm Down Error Type Stream Up Stream Comments

AIS-OAM

Adding and Modifying Connections

Configuring the Card, Lines, and Ports

Cnfcon portnum Cdvt CellLossIntegPeriod bufsize

Addcon portnum mastership remoteConnId

Bit Error Rate Testing on a T3 or E3 Cesm

Eight-Port Circuit Emulation Service Modules

Unstructured Data Transfer

Structured Data Transfer

Cell Delay Treatment

Error and Alarm Response

Redundancy Support for the Eight-Port Cesm

Cnfln linenum linecode linelen clksrc E1-signalling

Configuring Service on an Eight-Port Cesm

Receive LOF Receive AIS Blue AIS AIS link

AIS over the T1 link or alternating 1s

Addport portnum linenum beginslot numslot porttype

Configuring Bulk Distribution and Redundancy

Execute addred

Release 1.1.31, Part Number 78-11215-03 Rev. B0, May

Configuring Card and Line Parameters

Bulk Distribution for T1 Service

T1Slot T1 slot number, in the range

NumberOfT1s Number of T1s, in the range

Redundancy Support by the MGX-SRM-3T3/C

Configuring Redundancy Through the Redundancy Bus

RedType Is a number that specifies the type of redundancy

Configuring Redundancy Through the Distribution Bus

Bit Error Rate Testing Through an MGX-SRM-3T3

Test Medium Medium Type Loopback

Test Medium Medium Type Device to Loop Bert Pattern

Port Any None All patterns Line Metallic

Port Any Remote loopback Line Metallic or remote

Line Far end, remote, or Metallic

Pattern Test Options

Line None All patterns

Line Remote or metallic

Automatic Switchover

Online Diagnostics test

Alarms

Loopback Test Options

Oldiags debuglevel switchenable

Commands to Operate the Online Diagnostics

Log Files

Oldiags-help or oldiags help

DS3 Loopback Test

Configure Loopback on the Entire DS3 Line

Loopback Tests

Oldsplog logname

Configure Loopback on All DS1s in a DS3 Line

Receive a Loopback Request

To verify that DS3 interface can be put into loopback

Configure Transmit Feac Code

Configure DS3 for Sending Looped or Normal Data

Configure DS3 to Send Line Loopback

Configure DS3 for Sending Loopback Deactivation Request

Configure Receive Validation Feac Code

Configuring Feac Validation Criteria to be FEACCodes4Of5

Dspln should show LineXmtFEACCode as SendResetCode

Configure Feac Validation Criteria to be FEACCodes8Of10

Disable Feac Codes

Negative Tests

Configure DS3 Loopback Codes from the Standby PXM1 Card

Card and Service Configuration DS3 Loopback Test

Frsm HS1/B Specifications

Technical Specifications

Value

Category Description

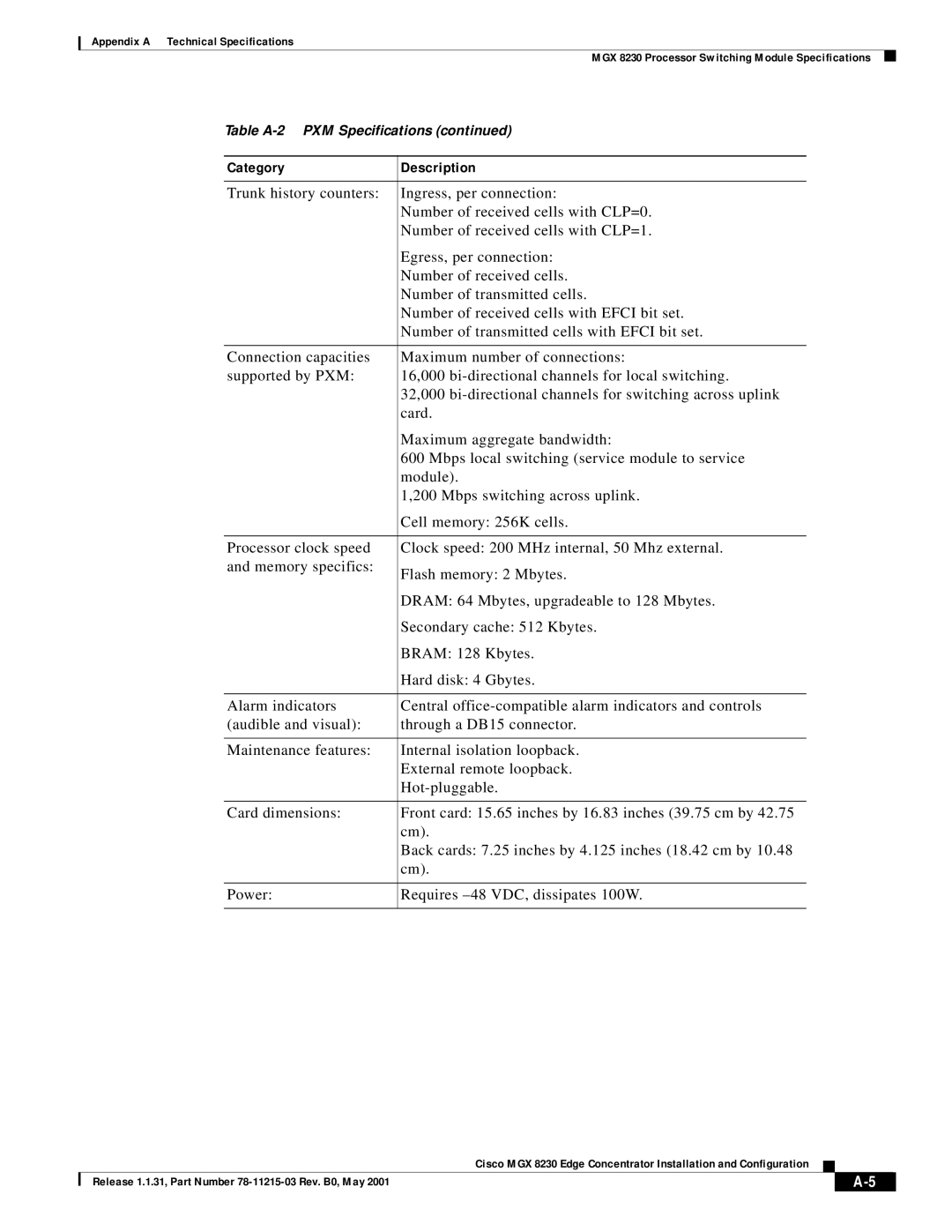

MGX 8230 Processor Switching Module Specifications

LED

Category Description

AUSM/B-8T1E1 Interface Characteristics

ESD

IEC

LCV, LES, LSES, CV, ES, MGX 8230, SEFS, AISS, UAS

LOS, OOF, AIS, RAI

LM-SMB-8E1

CBR, VBR, VBR+

Counter Type Description

ATMizer Channel Counters

Other Counters

Feature Significance or Value

FRSM-2CT3 Specifications

Interface Standard

B3ZS

FRSM-2CT3 Line Alarms

FRSM-2T3E3 Specifications

FRSM-2CT3 Framer

Interoperability Implementation Agreement v

T3 line characteristics appear in Table A-13

FRSM-2T3E3 T3 Line

T3 Framer Level

FRSM-2T3E3 Line Alarms

FRSM-HS2 Specifications

Statistics and Counter Specifications

FRSM-2T3E3 E3 Line

SCSI-2

Number of Hssi Lines Two Connector Type

Counter

Service Statistic

ATM Cell Statistic

Troubleshooting Statistic

Diagnostic Statistic

Interfaces

ECN current queue depth, per channel

FRSM-8T1 Specification

FR/ATM PVC Interworking Implementation Agreement FRF.5

Table A-26 List of Counters

FRSM-8E1 Specification

Table A-28 Frame Relay Service With E1 Lines

Transmit frames s

Diagnostics per port Last unknown Dlci that arrived

Changes

FR/ATM PVC Interworking Implementation Agreement FERF.5

Table A-30 List of Counters

B8ZS

Circuit Emulation Service Module for T1 Operation

Category

Circuit Emulation Service Module for E1 Operation

Transmit Clocking Normal clock or Srts generated Line Coding

Electromagnetic Compatibility

Physical and Electrical Characteristics for Cards

Conformance

Nebs

EMC

Circuit Emulations Service

Frame Relay

ATM Forum CES

Environmental

Safety

T3 Trunk Cabling

Connector Description

Cable Parameter Description

Rx BNC Receive T3 from trunk Tx BNC Transmit T3 to trunk

Frame Relay Cabling

T1 Cabling

Pin No Description

SMB Connector

E1 Cabling

Rx BNC Receive E1 from trunk Tx BNC Transmit E1 to trunk

12IN1-S4 V.35/X.21 Back Card

Signal Name Source

Hssi Port Connectors

Signal Name

Pin No Name Signal Function Polarity Signal Source

DC Power Cabling

AC Power Cabling

Maintenance and Control Ports

Control and Clock Cabling

External Clock Input Cabling

External Alarm Cabling

T1 Clock Cabling

Pin No Name Description

Pin No Alarm Description

Release 1.1.31, Part Number 78-11215-03 Rev. B0, May

More general Class of Service Buffer or CosB

Monarch chip set

StrataView Plus

GL-2

StrataCom IGX switch

GL-3

Strictly correct

APS

AAL5

Ausm

AUSM/B

Cesm

Frsm cards Circuit Emulation Service Module

CIR

AX-CESM-8E1 AX-CESM-8T1

MGX-HS2/B Front cards

Frsm

MGX-FRSM-2E3T3

MGX-AUSM/B-8T1

MGX-AUSM/B-8E1

MGX-FRSM-2CT3

MGX-HS2/B

PXM

PAR

PXM1-UI

PXM-UI

SRM-3T3

Sonet