Central Processing Unit:

Central Processing Unit: Exception Handling

Exception Handling

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

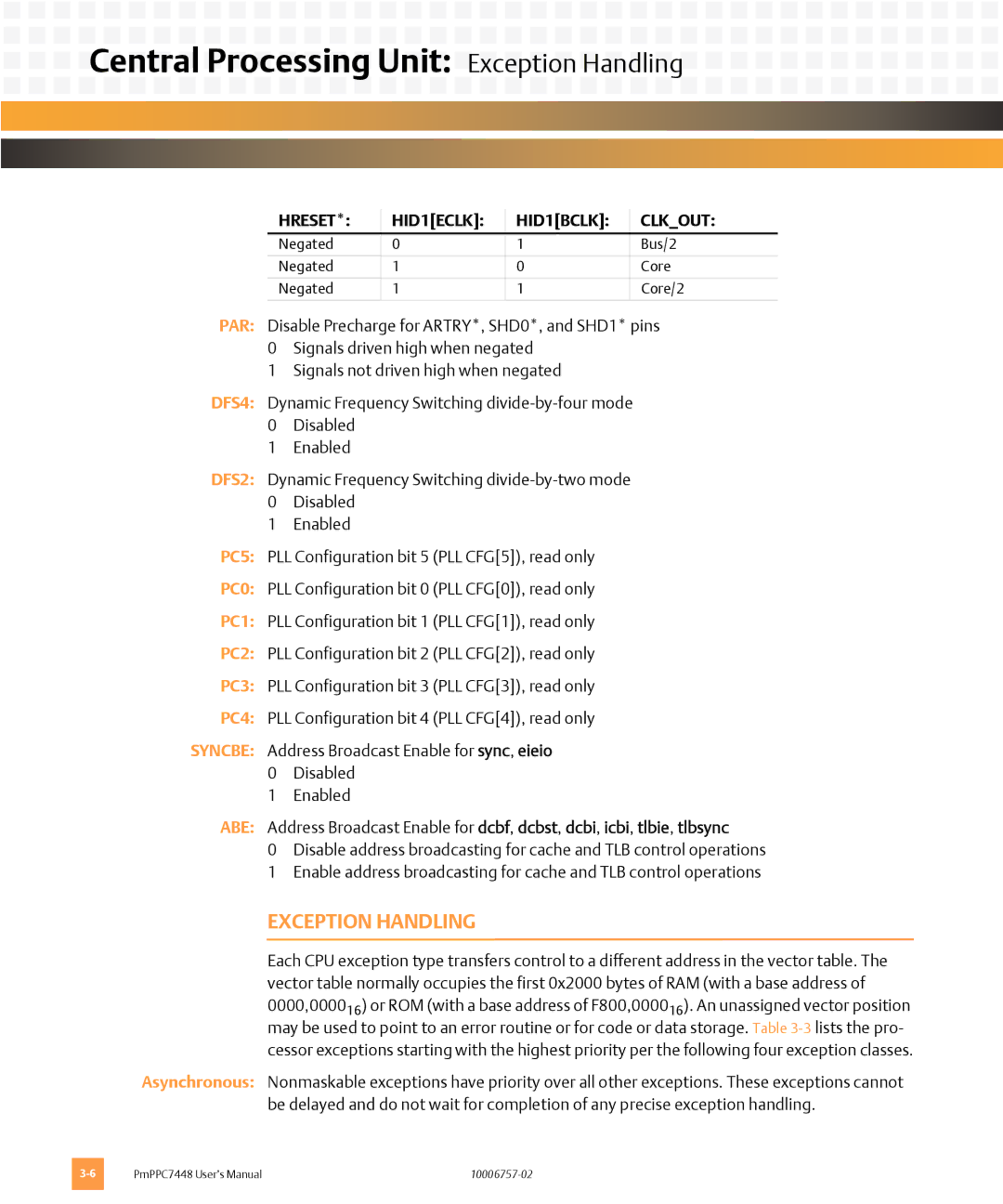

| HRESET*: |

| HID1[ECLK]: |

| HID1[BCLK]: |

| CLK_OUT: |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Negated |

| 0 |

|

|

|

|

|

|

|

|

| 1 |

|

|

|

|

|

|

|

|

| Bus/2 |

|

| |||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

| Negated |

| 1 |

|

|

|

|

|

|

|

|

| 0 |

|

|

|

|

|

|

|

|

| Core |

| ||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

| Negated |

| 1 |

|

|

|

|

|

|

|

|

| 1 |

|

|

|

|

|

|

|

|

| Core/2 |

| ||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PAR: Disable Precharge for ARTRY*, SHD0*, and SHD1* pins

0Signals driven high when negated

1Signals not driven high when negated

DFS4: Dynamic Frequency Switching

0Disabled

1Enabled

DFS2: Dynamic Frequency Switching

0Disabled

1Enabled

PC5: PLL Configuration bit 5 (PLL CFG[5]), read only

PC0: PLL Configuration bit 0 (PLL CFG[0]), read only

PC1: PLL Configuration bit 1 (PLL CFG[1]), read only

PC2: PLL Configuration bit 2 (PLL CFG[2]), read only

PC3: PLL Configuration bit 3 (PLL CFG[3]), read only

PC4: PLL Configuration bit 4 (PLL CFG[4]), read only

SYNCBE: Address Broadcast Enable for sync, eieio

0Disabled

1Enabled

ABE: Address Broadcast Enable for dcbf, dcbst, dcbi, icbi, tlbie, tlbsync

0Disable address broadcasting for cache and TLB control operations

1Enable address broadcasting for cache and TLB control operations

EXCEPTION HANDLING

Each CPU exception type transfers control to a different address in the vector table. The vector table normally occupies the first 0x2000 bytes of RAM (with a base address of 0000,000016) or ROM (with a base address of F800,000016). An unassigned vector position may be used to point to an error routine or for code or data storage. Table

Asynchronous: Nonmaskable exceptions have priority over all other exceptions. These exceptions cannot be delayed and do not wait for completion of any precise exception handling.

PmPPC7448 User’s Manual |