Central Processing Unit:

Central Processing Unit: Exception Handling

Exception Handling

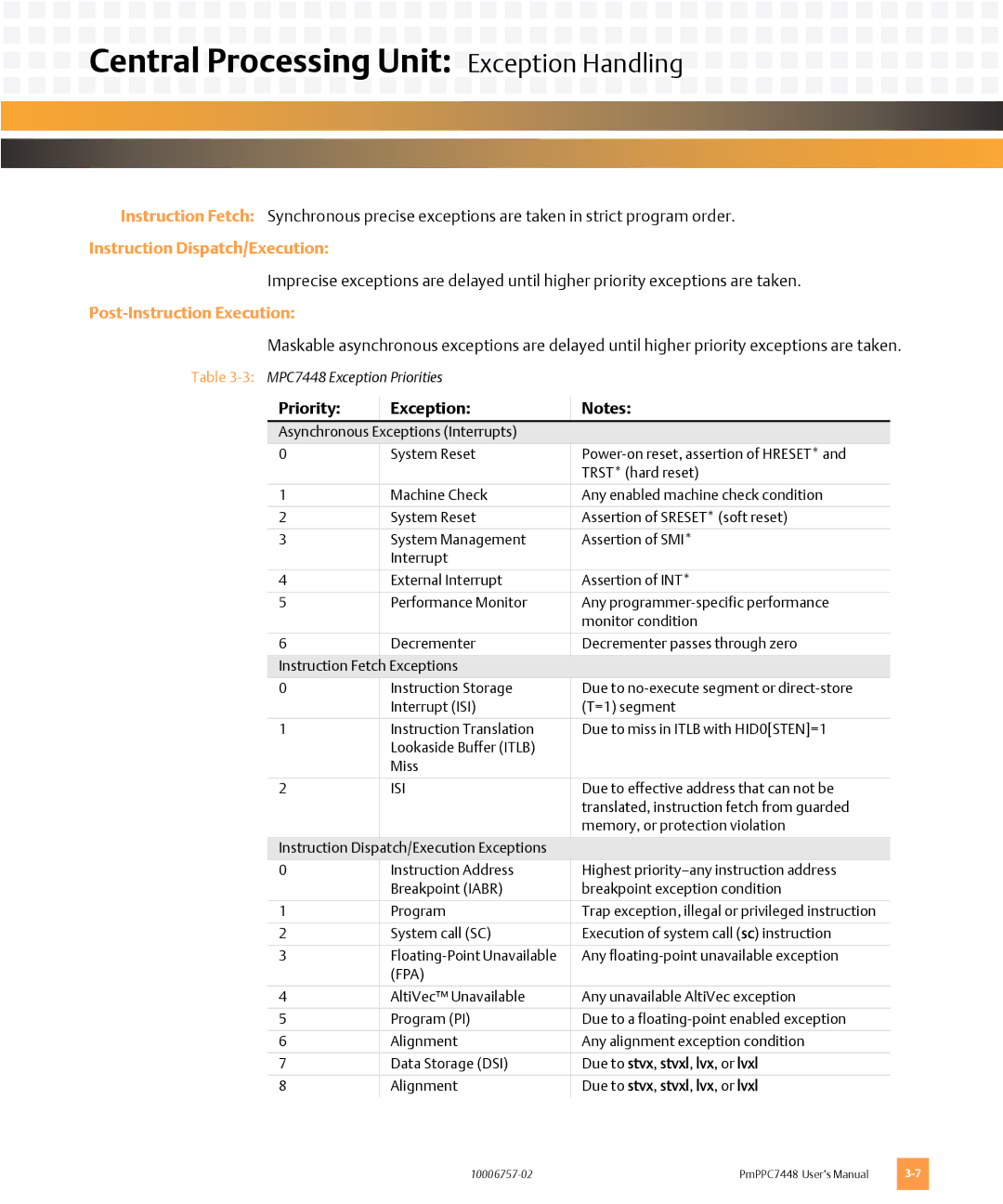

Instruction Fetch: Synchronous precise exceptions are taken in strict program order.

Instruction Dispatch/Execution:

Imprecise exceptions are delayed until higher priority exceptions are taken.

Post-Instruction Execution:

Maskable asynchronous exceptions are delayed until higher priority exceptions are taken.

Table

Priority: | Exception: | Notes: |

Asynchronous Exceptions (Interrupts) |

| |

0 | System Reset | |

|

| TRST* (hard reset) |

|

|

|

1 | Machine Check | Any enabled machine check condition |

|

|

|

2 | System Reset | Assertion of SRESET* (soft reset) |

|

|

|

3 | System Management | Assertion of SMI* |

| Interrupt |

|

|

|

|

4 | External Interrupt | Assertion of INT* |

|

|

|

5 | Performance Monitor | Any |

|

| monitor condition |

|

|

|

6 | Decrementer | Decrementer passes through zero |

|

|

|

Instruction Fetch Exceptions |

| |

0 | Instruction Storage | Due to |

| Interrupt (ISI) | (T=1) segment |

|

|

|

1 | Instruction Translation | Due to miss in ITLB with HID0[STEN]=1 |

| Lookaside Buffer (ITLB) |

|

| Miss |

|

|

|

|

2 | ISI | Due to effective address that can not be |

|

| translated, instruction fetch from guarded |

|

| memory, or protection violation |

|

|

|

Instruction Dispatch/Execution Exceptions |

| |

0 | Instruction Address | Highest |

| Breakpoint (IABR) | breakpoint exception condition |

|

|

|

1 | Program | Trap exception, illegal or privileged instruction |

|

|

|

2 | System call (SC) | Execution of system call (sc) instruction |

|

|

|

3 | Any | |

| (FPA) |

|

|

|

|

4 | AltiVec™ Unavailable | Any unavailable AltiVec exception |

|

|

|

5 | Program (PI) | Due to a |

|

|

|

6 | Alignment | Any alignment exception condition |

|

|

|

7 | Data Storage (DSI) | Due to stvx, stvxl, lvx, or lvxl |

|

|

|

8 | Alignment | Due to stvx, stvxl, lvx, or lvxl |

|

|

|

PmPPC7448 User’s Manual |