![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() Section 7

Section 7![]()

CPLD

CPLD

This chapter lists the registers implemented by the complex programmable logic device (CPLD).

RESET REGISTERS

The reset signals are routed to and distributed by the CPLD. To support this functionality, the CPLD includes two registers; one indicates the reason for the last reset, and the other forces one of several types of reset.

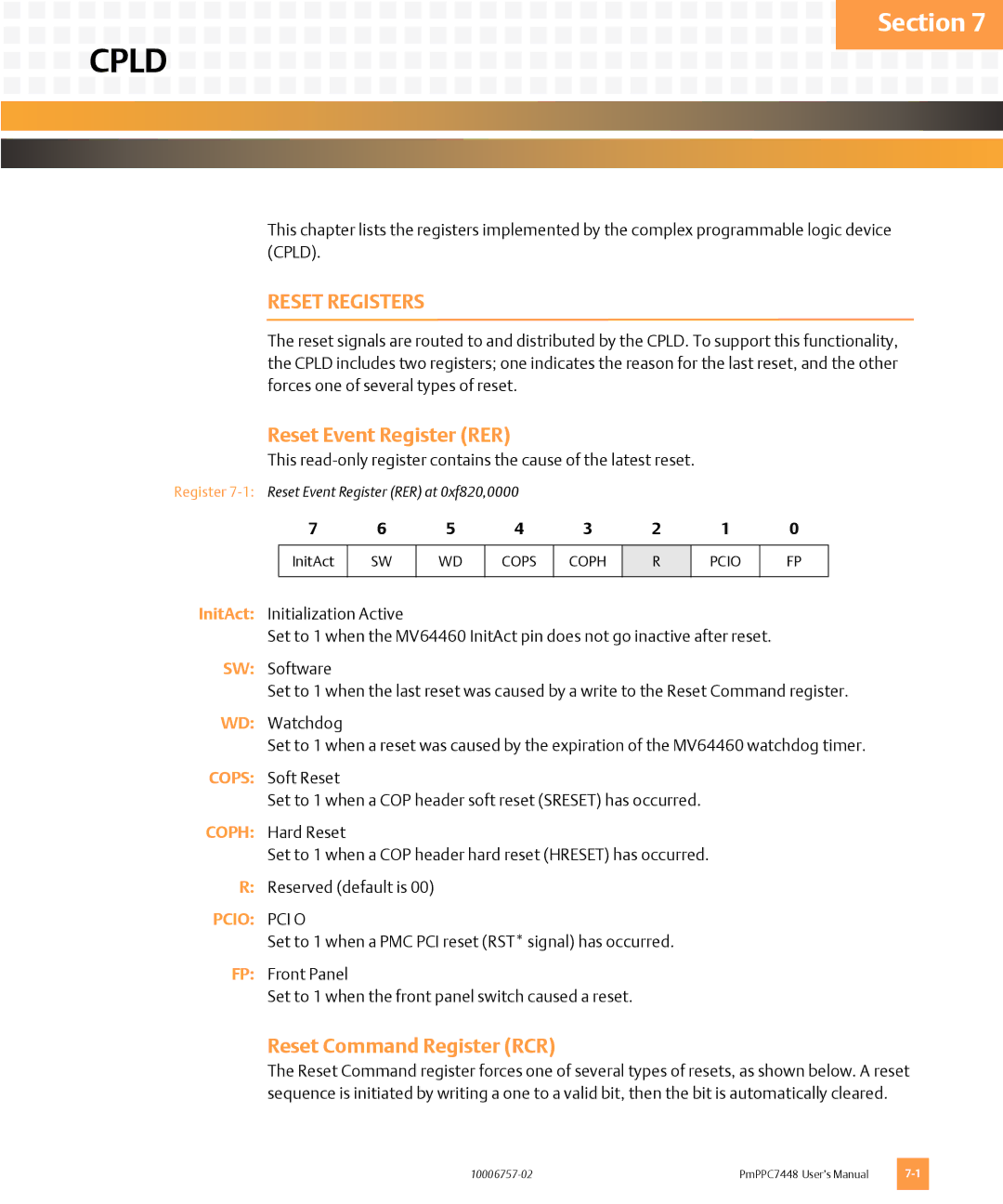

Reset Event Register (RER)

This

Register

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

InitAct

SW

WD

COPS

COPH

R

PCIO

FP

InitAct: Initialization Active

Set to 1 when the MV64460 InitAct pin does not go inactive after reset.

SW: Software

Set to 1 when the last reset was caused by a write to the Reset Command register.

WD: Watchdog

Set to 1 when a reset was caused by the expiration of the MV64460 watchdog timer.

COPS: Soft Reset

Set to 1 when a COP header soft reset (SRESET) has occurred.

COPH: Hard Reset

Set to 1 when a COP header hard reset (HRESET) has occurred.

R:Reserved (default is 00)

PCIO: PCI O

Set to 1 when a PMC PCI reset (RST* signal) has occurred.

FP: Front Panel

Set to 1 when the front panel switch caused a reset.

Reset Command Register (RCR)

The Reset Command register forces one of several types of resets, as shown below. A reset sequence is initiated by writing a one to a valid bit, then the bit is automatically cleared.

PmPPC7448 User’s Manual |