System Controller: PCI Bus Control Signals

System Controller: PCI Bus Control Signals

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

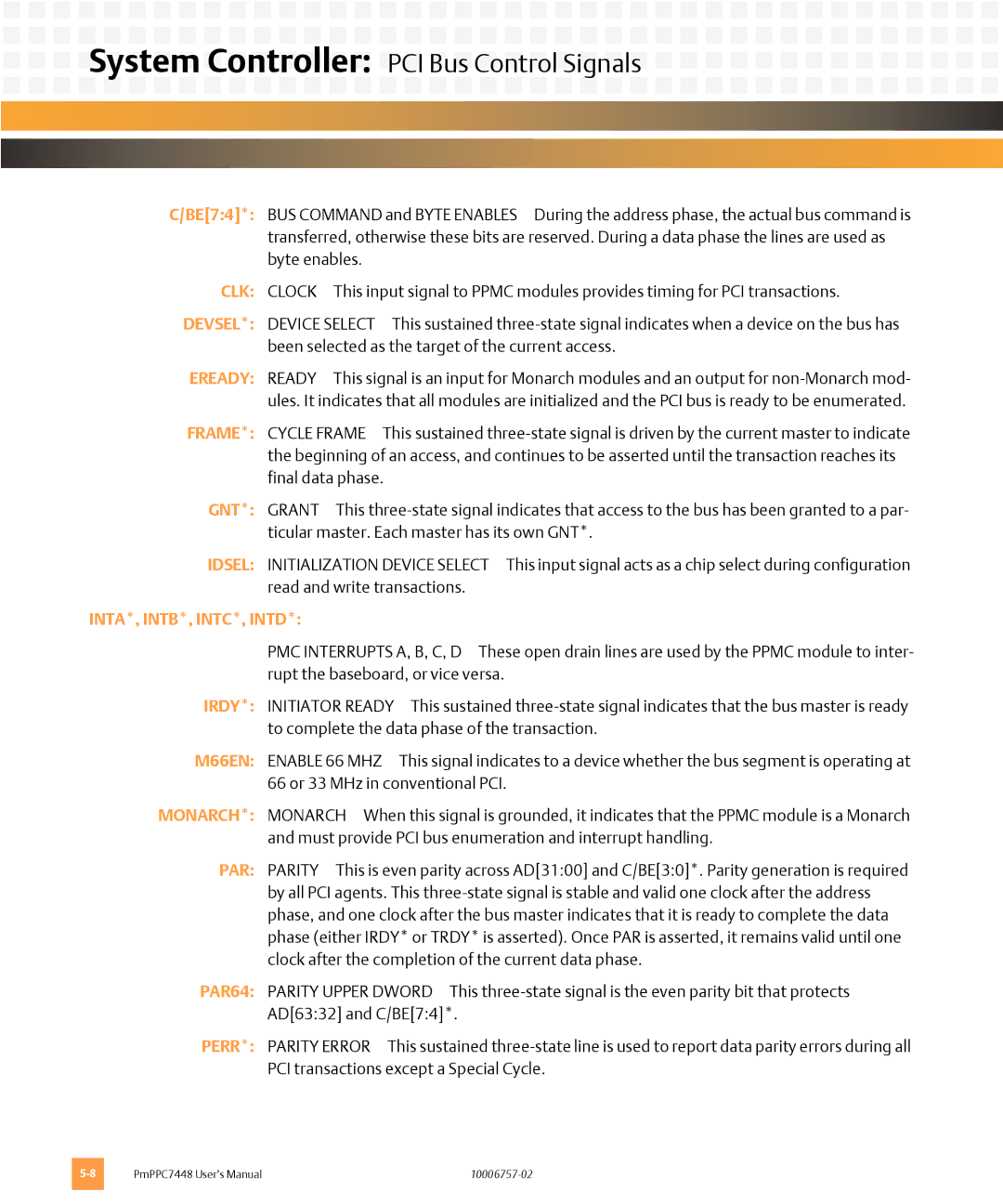

C/BE[7:4]*: | BUS COMMAND and BYTE ENABLES During the address phase, the actual bus command is |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

| transferred, otherwise these bits are reserved. During a data phase the lines are used as |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

| byte enables. |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

| CLK: | CLOCK This input signal to PPMC modules provides timing for PCI transactions. |

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||

DEVSEL*: DEVICE SELECT | This sustained | |

been selected as the target of the current access. | ||

EREADY: READY | This signal is an input for Monarch modules and an output for | |

ules. It indicates that all modules are initialized and the PCI bus is ready to be enumerated. | ||

FRAME*: CYCLE FRAME | This sustained | |

the beginning of an access, and continues to be asserted until the transaction reaches its | ||

final data phase. | ||

GNT*: GRANT | This | |

ticular master. Each master has its own GNT*.

IDSEL: INITIALIZATION DEVICE SELECT This input signal acts as a chip select during configuration read and write transactions.

INTA*, INTB*, INTC*, INTD*:

PMC INTERRUPTS A, B, C, D These open drain lines are used by the PPMC module to inter- rupt the baseboard, or vice versa.

IRDY*: INITIATOR READY This sustained

M66EN: ENABLE 66 MHZ This signal indicates to a device whether the bus segment is operating at 66 or 33 MHz in conventional PCI.

MONARCH*: MONARCH When this signal is grounded, it indicates that the PPMC module is a Monarch and must provide PCI bus enumeration and interrupt handling.

PAR: PARITY This is even parity across AD[31:00] and C/BE[3:0]*. Parity generation is required by all PCI agents. This

PAR64: PARITY UPPER DWORD This

AD[63:32] and C/BE[7:4]*.

PERR*: PARITY ERROR This sustained

PCI transactions except a Special Cycle.

PmPPC7448 User’s Manual |