System Controller: PCI Interface

System Controller: PCI Interface

PCI Configuration Space

The PCI slave supports Type 00 configuration space header as defined in the PCI specifica- tion. The MV64460 is a

PCI Subsystem Device and Vendor ID Assignment

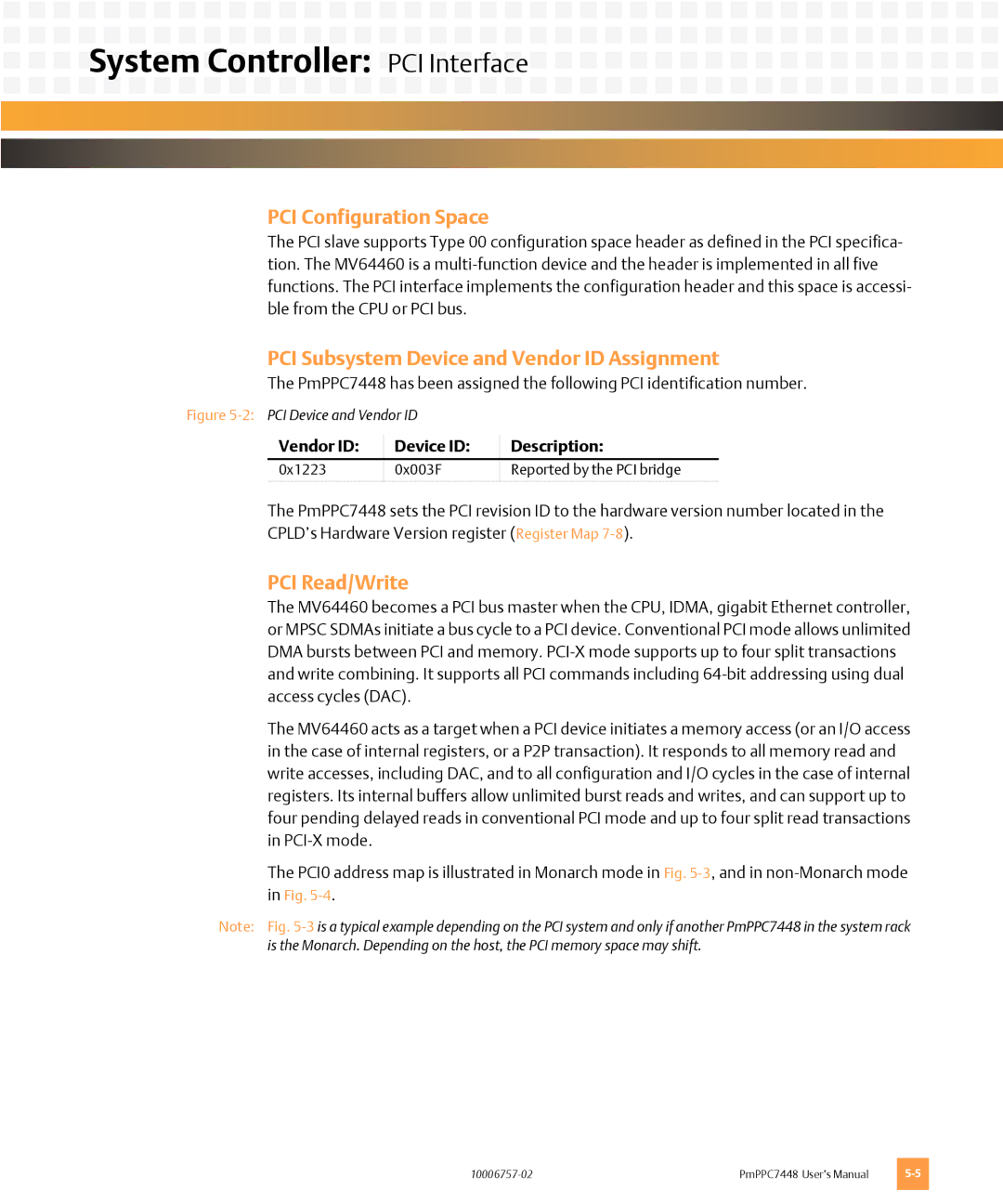

The PmPPC7448 has been assigned the following PCI identification number.

Figure 5-2: PCI Device and Vendor ID

Vendor ID: | Device ID: | Description: |

0x1223 | 0x003F | Reported by the PCI bridge |

|

|

|

The PmPPC7448 sets the PCI revision ID to the hardware version number located in the

CPLD’s Hardware Version register (Register Map

PCI Read/Write

The MV64460 becomes a PCI bus master when the CPU, IDMA, gigabit Ethernet controller, or MPSC SDMAs initiate a bus cycle to a PCI device. Conventional PCI mode allows unlimited DMA bursts between PCI and memory.

The MV64460 acts as a target when a PCI device initiates a memory access (or an I/O access in the case of internal registers, or a P2P transaction). It responds to all memory read and write accesses, including DAC, and to all configuration and I/O cycles in the case of internal registers. Its internal buffers allow unlimited burst reads and writes, and can support up to four pending delayed reads in conventional PCI mode and up to four split read transactions in

The PCI0 address map is illustrated in Monarch mode in Fig.

Note: Fig.

PmPPC7448 User’s Manual |