Central Processing Unit:

Central Processing Unit: Processor Initialization

Processor Initialization

BHT: Branch History Table Enable

0Disabled

1Allows use of dynamic prediction

NOPDST:

0Instructions enabled

1Instructions are

NOPTI:

0Instructions enabled

1Instructions are

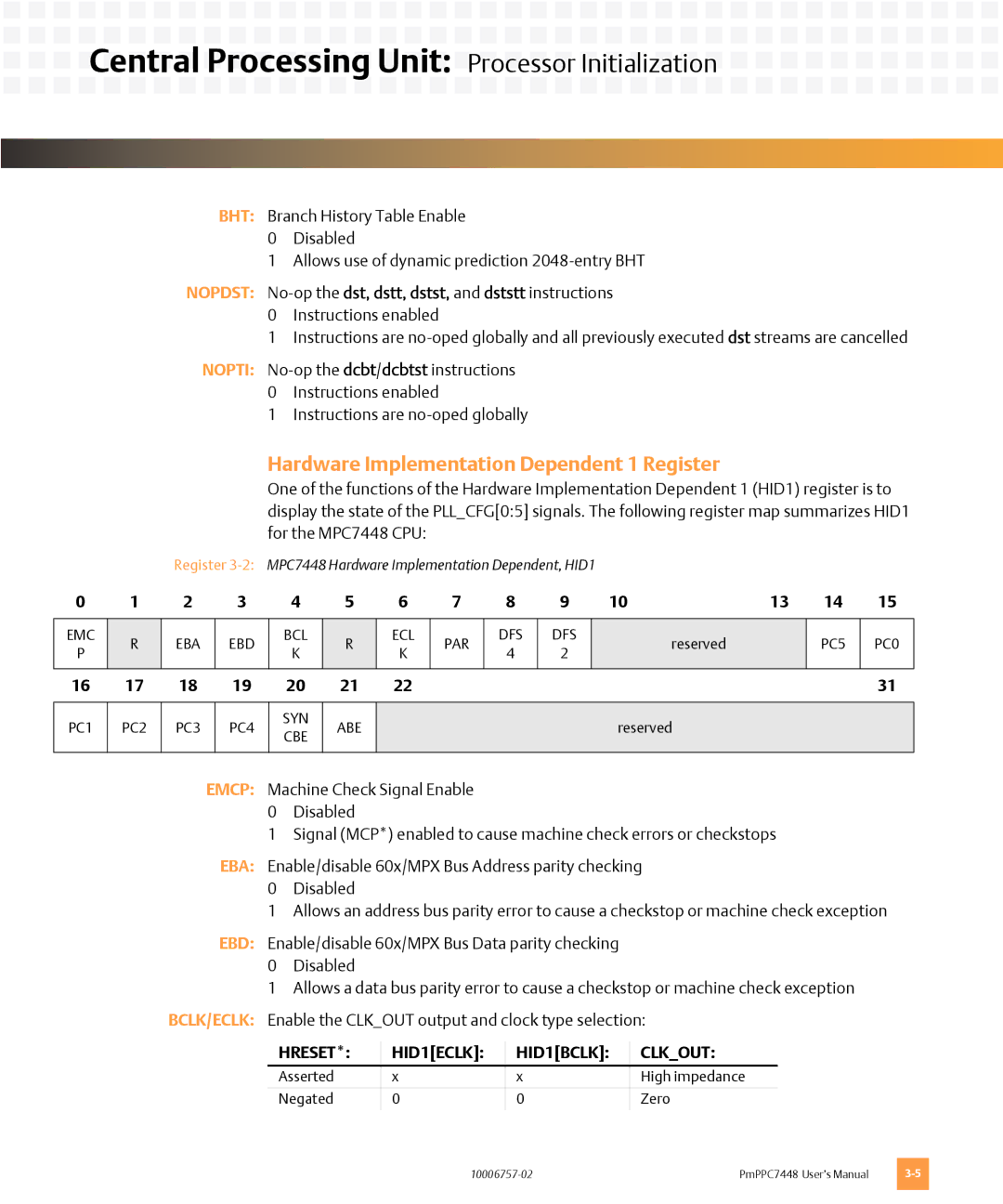

Hardware Implementation Dependent 1 Register

One of the functions of the Hardware Implementation Dependent 1 (HID1) register is to display the state of the PLL_CFG[0:5] signals. The following register map summarizes HID1 for the MPC7448 CPU:

Register

0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 13 | 14 | 15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EMC | R | EBA | EBD | BCL | R | ECL | PAR | DFS | DFS | reserved |

| PC5 | PC0 |

P | K | K | 4 | 2 |

| ||||||||

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16 | 17 | 18 | 19 | 20 | 21 | 22 |

|

|

|

|

|

| 31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PC1 | PC2 | PC3 | PC4 | SYN | ABE |

|

|

|

| reserved |

|

|

|

CBE |

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EMCP: Machine Check Signal Enable

0Disabled

1Signal (MCP*) enabled to cause machine check errors or checkstops

EBA: Enable/disable 60x/MPX Bus Address parity checking

0Disabled

1Allows an address bus parity error to cause a checkstop or machine check exception

EBD: Enable/disable 60x/MPX Bus Data parity checking

0Disabled

1Allows a data bus parity error to cause a checkstop or machine check exception

BCLK/ECLK: Enable the CLK_OUT output and clock type selection:

HRESET*: | HID1[ECLK]: | HID1[BCLK]: | CLK_OUT: |

Asserted | x | x | High impedance |

|

|

|

|

Negated | 0 | 0 | Zero |

|

|

|

|

PmPPC7448 User’s Manual |