Central Processing Unit: Processor Reset |

|

|

| ||||

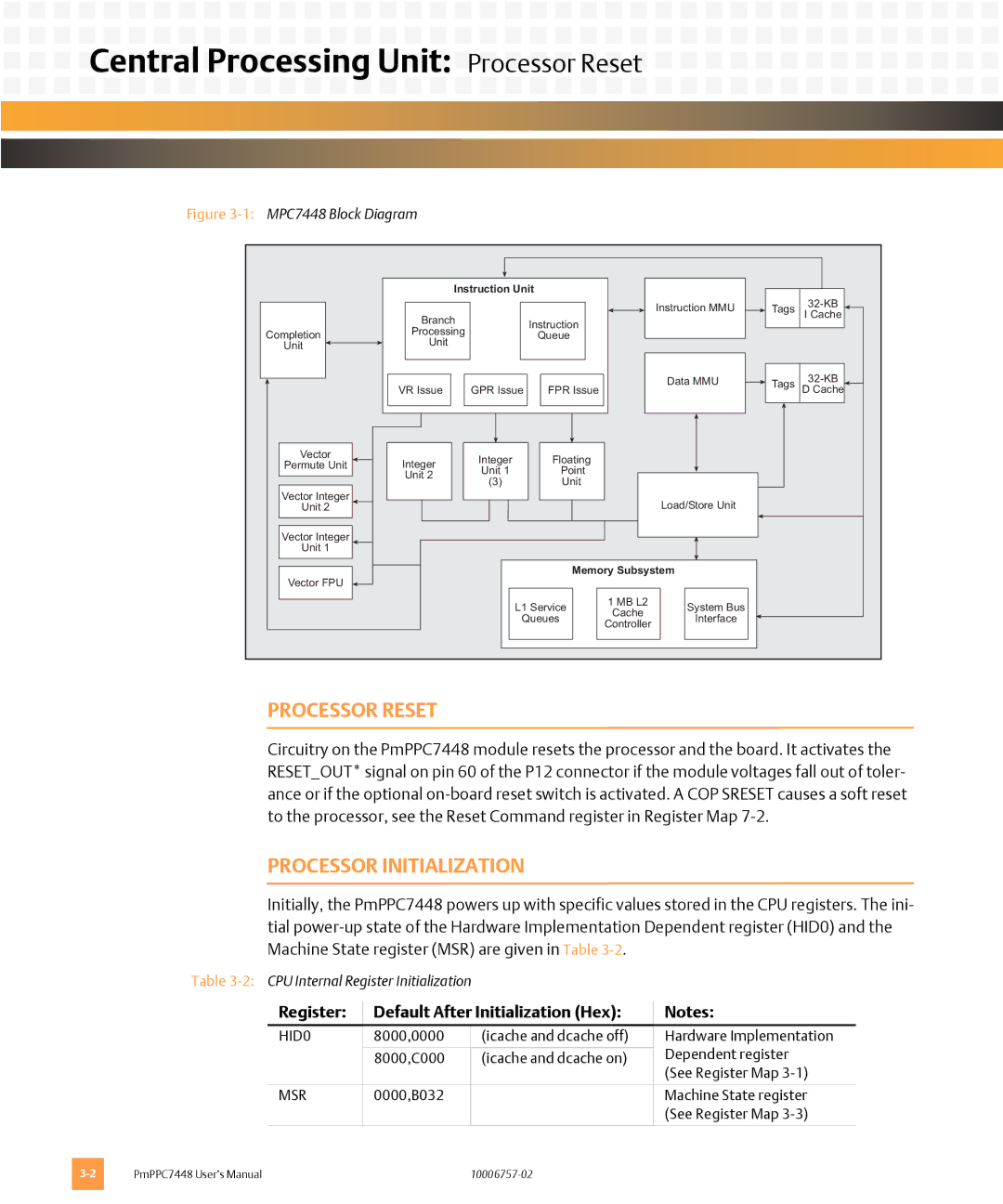

Figure |

|

|

|

|

|

| |

| Instruction Unit |

|

|

|

| ||

|

|

|

|

| Instruction MMU | Tags | |

| Branch |

| Instruction |

| I Cache | ||

|

|

|

|

|

| ||

Completion | Processing |

|

|

|

|

| |

| Queue |

|

|

|

| ||

Unit |

|

|

|

|

| ||

Unit |

|

|

|

|

|

| |

|

|

|

|

|

|

| |

| VR Issue | GPR Issue | FPR Issue |

| Data MMU | Tags | |

|

|

| D Cache | ||||

Vector | Integer | Integer | Floating |

|

|

|

|

Permute Unit |

|

|

|

| |||

Unit 1 | Point |

|

|

|

| ||

| Unit 2 |

|

|

|

| ||

| (3) | Unit |

|

|

|

| |

|

|

|

|

|

| ||

Vector Integer |

|

|

|

| Load/Store Unit |

|

|

Unit 2 |

|

|

|

|

|

| |

Vector Integer |

|

|

|

|

|

|

|

Unit 1 |

|

|

|

|

|

|

|

Vector FPU |

|

| Memory Subsystem |

|

| ||

|

|

|

|

|

|

| |

|

| L1 Service | 1 MB L2 | System Bus |

|

| |

|

| Cache |

|

| |||

|

| Queues | Interface |

|

| ||

|

| Controller |

|

| |||

|

|

|

|

|

|

| |

PROCESSOR RESET

Circuitry on the PmPPC7448 module resets the processor and the board. It activates the RESET_OUT* signal on pin 60 of the P12 connector if the module voltages fall out of toler- ance or if the optional

PROCESSOR INITIALIZATION

Initially, the PmPPC7448 powers up with specific values stored in the CPU registers. The ini- tial

Table

Register: | Default After Initialization (Hex): | Notes: | |

HID0 | 8000,0000 | (icache and dcache off) | Hardware Implementation |

|

|

| Dependent register |

| 8000,C000 | (icache and dcache on) | |

|

|

| (See Register Map |

MSR | 0000,B032 |

| Machine State register |

|

|

| (See Register Map |

|

|

|

|

PmPPC7448 User’s Manual |