Development Mezzanine Card:

Development Mezzanine Card: PmPPC7448 to DMC JTAG

PmPPC7448 to DMC JTAG

PMPPC7448 TO DMC JTAG

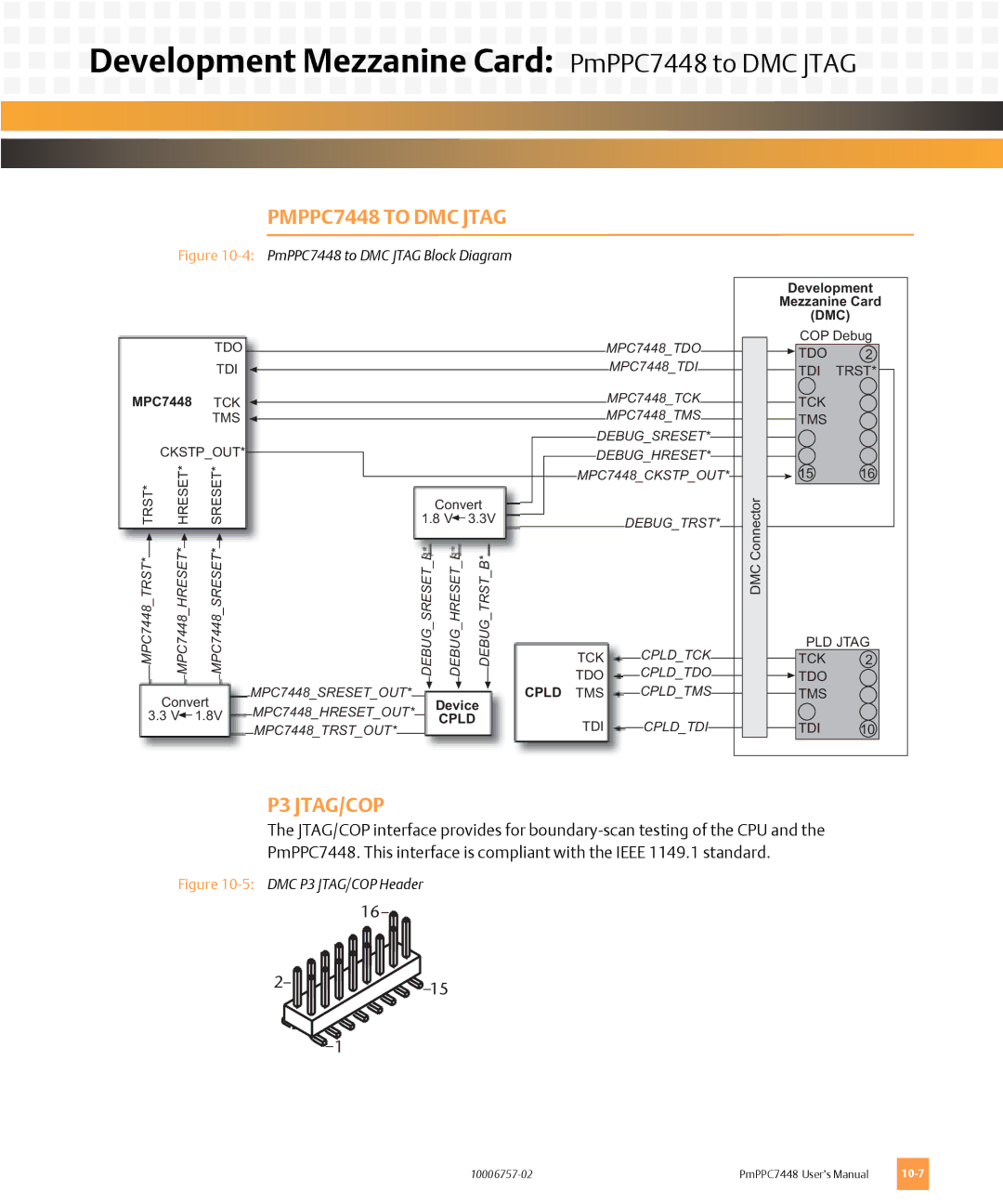

Figure 10-4: PmPPC7448 to DMC JTAG Block Diagram

|

|

|

| TDO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MPC7448_TDO |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

| TDI |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MPC7448_TDI |

| ||||

MPC7448 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MPC7448_TCK |

| ||||||||

TCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MPC7448_TMS |

| |||||||||

|

|

|

| TMS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| DEBUG_SRESET* |

| ||||||

|

| CKSTP_OUT* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

TRST* |

|

|

|

| 1.8 V | 3.3V |

|

| DEBUG_HRESET* |

| |||||||||||||||

|

|

|

|

|

| ||||||||||||||||||||

HRESET* | SRESET* |

|

|

|

|

| MPC7448_CKSTP_OUT* |

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| Convert |

|

|

|

|

| DEBUG_TRST* |

| ||||

|

| MPC7448HRESET* |

|

|

|

|

|

|

|

|

|

|

| DEBUGHRESET B* |

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

MPC7448 TRST* |

|

| MPC7448SRESET* |

|

|

|

|

|

| DEBUGSRESET B* |

|

| DEBUG TRST B* |

|

|

|

|

| TDO |

| CPLD_TDO |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| TCK |

| CPLD_TCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| MPC7448_SRESET_OUT* |

|

|

|

|

|

|

|

| CPLD | TMS |

| CPLD_TMS |

| ||||

|

| Convert | MPC7448_HRESET_OUT* |

|

|

| Device |

|

|

|

| ||||||||||||||

3.3 V |

| 1.8V |

|

|

|

|

| CPLD | TDI |

| CPLD_TDI |

| |||||||||||||

|

|

| MPC7448_TRST_OUT* |

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DMC Connector

Development

Mezzanine Card

(DMC)

COP Debug ![]() TDO 2 TDI TRST*

TDO 2 TDI TRST*

TCK

TMS

15 | 16 |

PLD JTAG

TCK 2 ![]() TDO

TDO

TMS

TDI 10

P3 JTAG/COP

The JTAG/COP interface provides for

Figure 10-5: DMC P3 JTAG/COP Header

16![]()

![]()

2![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() 15

15 ![]()

![]()

![]() 1

1

PmPPC7448 User’s Manual |