![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() Section 5

Section 5![]()

System Controller

System Controller

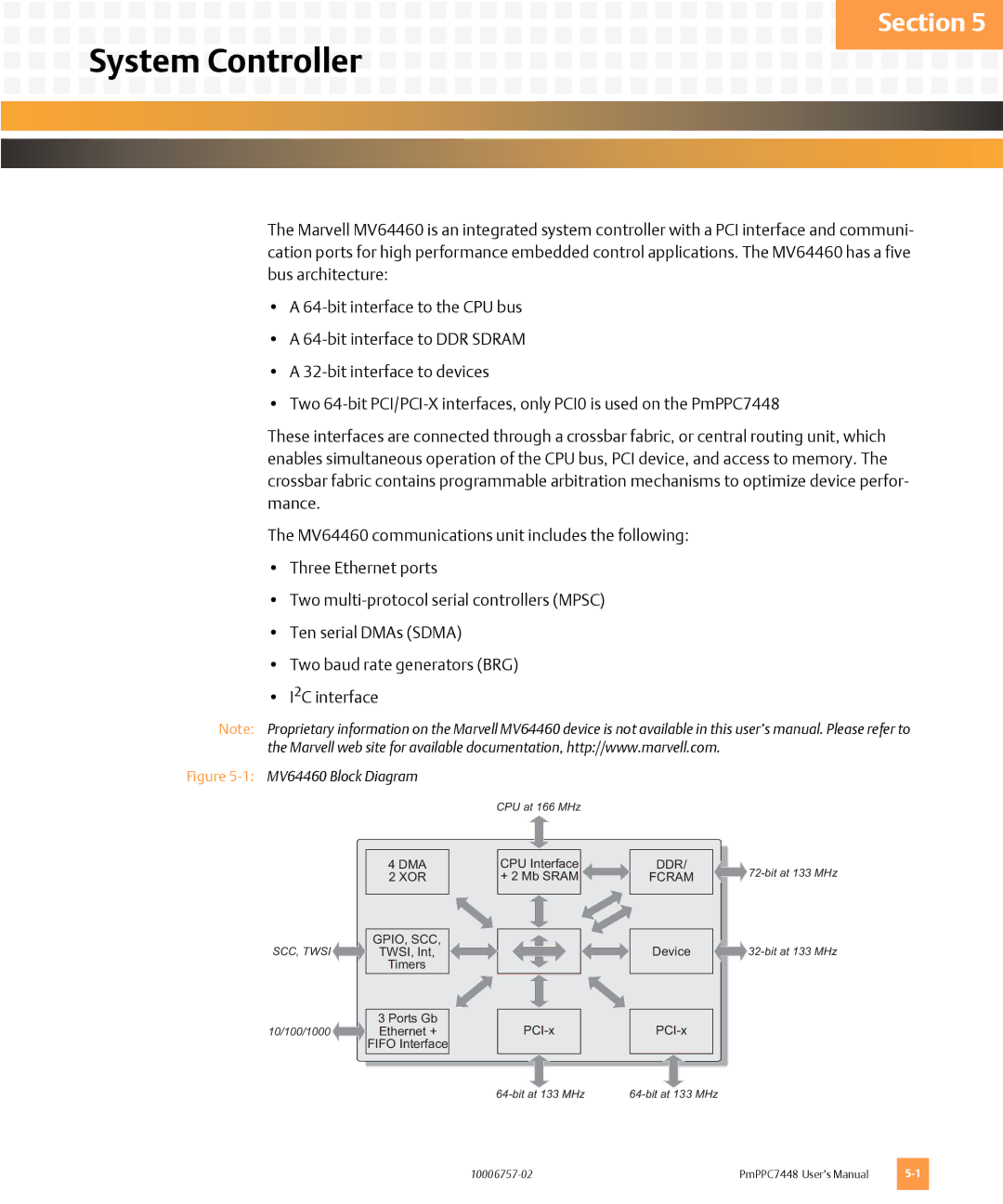

The Marvell MV64460 is an integrated system controller with a PCI interface and communi- cation ports for high performance embedded control applications. The MV64460 has a five bus architecture:

•A

•A

•A

•Two

These interfaces are connected through a crossbar fabric, or central routing unit, which enables simultaneous operation of the CPU bus, PCI device, and access to memory. The crossbar fabric contains programmable arbitration mechanisms to optimize device perfor- mance.

The MV64460 communications unit includes the following:

•Three Ethernet ports

•Two

•Ten serial DMAs (SDMA)

•Two baud rate generators (BRG)

•I2C interface

Note: Proprietary information on the Marvell MV64460 device is not available in this user’s manual. Please refer to the Marvell web site for available documentation, http://www.marvell.com.

Figure 5-1: MV64460 Block Diagram

| 4 DMA |

| 2 XOR |

|

|

|

|

| GPIO, SCC, |

SCC, TWSI | TWSI, Int, |

| Timers |

|

|

| 3 Ports Gb |

10/100/1000 | Ethernet + |

| FIFO Interface |

CPU at 166 MHz

CPU Interface + 2 Mb SRAM

DDR/ | ||

FCRAM | ||

| ||

|

|

Device | |

|

|

PmPPC7448 User’s Manual |