Central Processing Unit:

Central Processing Unit: Cache Memory

Cache Memory

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

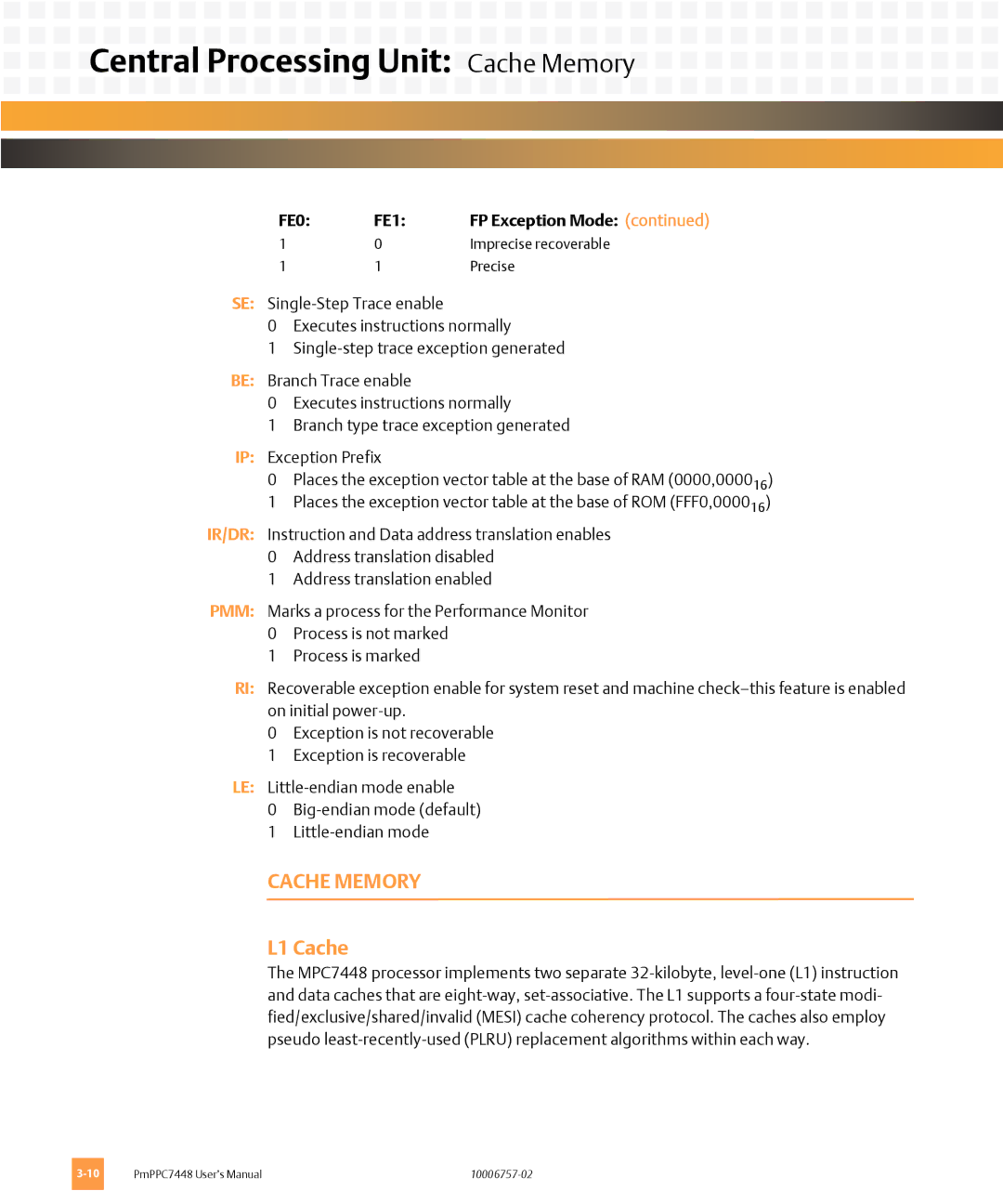

FE0: |

| FE1: | FP Exception Mode: (continued) |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

1 |

|

|

|

|

| 0 |

|

|

|

|

| Imprecise recoverable |

| |||||||||||||||||||||||||||||||||||||||||

1 |

|

|

|

|

| 1 |

|

|

|

|

| Precise |

| |||||||||||||||||||||||||||||||||||||||||

SE:

0Executes instructions normally

1

BE: Branch Trace enable

0Executes instructions normally

1Branch type trace exception generated

IP: Exception Prefix

0Places the exception vector table at the base of RAM (0000,000016)

1Places the exception vector table at the base of ROM (FFF0,000016)

IR/DR: Instruction and Data address translation enables

0Address translation disabled

1Address translation enabled

PMM: Marks a process for the Performance Monitor

0Process is not marked

1Process is marked

RI: Recoverable exception enable for system reset and machine

0Exception is not recoverable

1Exception is recoverable

LE:

0

1

CACHE MEMORY

L1 Cache

The MPC7448 processor implements two separate

PmPPC7448 User’s Manual |