Central Processing Unit:

Central Processing Unit: Exception Processing

Exception Processing

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

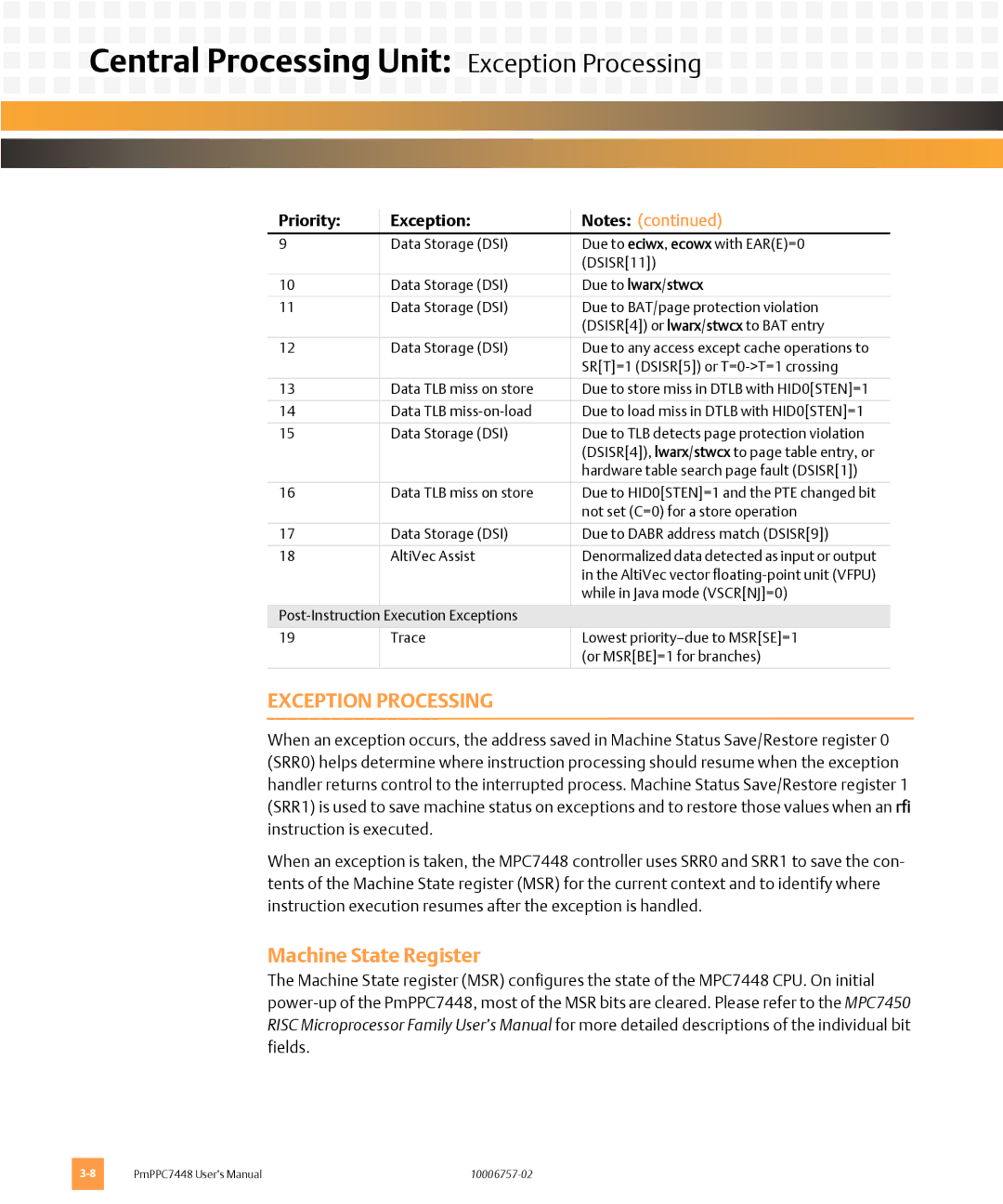

| Priority: |

| Exception: |

|

| Notes: (continued) |

| |||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 9 |

|

|

|

|

|

|

|

| Data Storage (DSI) |

|

| Due to eciwx, ecowx with EAR(E)=0 |

|

| |||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| (DSISR[11]) |

| ||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

| 10 |

|

|

|

|

|

|

|

| Data Storage (DSI) |

|

| Due to lwarx/stwcx |

| ||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

| 11 |

|

|

|

|

|

|

|

| Data Storage (DSI) |

|

| Due to BAT/page protection violation |

| ||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| (DSISR[4]) or lwarx/stwcx to BAT entry |

| ||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

| 12 |

|

|

|

|

|

|

|

| Data Storage (DSI) |

|

| Due to any access except cache operations to |

| ||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| SR[T]=1 (DSISR[5]) or |

| ||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

| 13 |

|

|

|

|

|

|

|

| Data TLB miss on store |

|

| Due to store miss in DTLB with HID0[STEN]=1 |

| ||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

| 14 |

|

|

|

|

|

|

|

| Data TLB |

|

| Due to load miss in DTLB with HID0[STEN]=1 |

| ||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

| 15 |

|

|

|

|

|

|

|

| Data Storage (DSI) |

|

| Due to TLB detects page protection violation |

| ||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| (DSISR[4]), lwarx/stwcx to page table entry, or |

| ||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| hardware table search page fault (DSISR[1]) |

| ||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

| 16 |

|

|

|

|

|

|

|

| Data TLB miss on store |

|

| Due to HID0[STEN]=1 and the PTE changed bit |

| ||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| not set (C=0) for a store operation |

| ||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

| 17 |

|

|

|

|

|

|

|

| Data Storage (DSI) |

|

| Due to DABR address match (DSISR[9]) |

| ||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

| 18 |

|

|

|

|

|

|

|

| AltiVec Assist |

|

| Denormalized data detected as input or output |

| ||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| in the AltiVec vector |

| ||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| while in Java mode (VSCR[NJ]=0) |

| ||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||

| 19 |

|

|

|

|

|

|

|

| Trace |

|

| Lowest |

|

| |||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| (or MSR[BE]=1 for branches) |

| ||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EXCEPTION PROCESSING

When an exception occurs, the address saved in Machine Status Save/Restore register 0 (SRR0) helps determine where instruction processing should resume when the exception handler returns control to the interrupted process. Machine Status Save/Restore register 1 (SRR1) is used to save machine status on exceptions and to restore those values when an rfi instruction is executed.

When an exception is taken, the MPC7448 controller uses SRR0 and SRR1 to save the con- tents of the Machine State register (MSR) for the current context and to identify where instruction execution resumes after the exception is handled.

Machine State Register

The Machine State register (MSR) configures the state of the MPC7448 CPU. On initial

PmPPC7448 User’s Manual |