Central Processing Unit:

Central Processing Unit: Cache Memory

Cache Memory

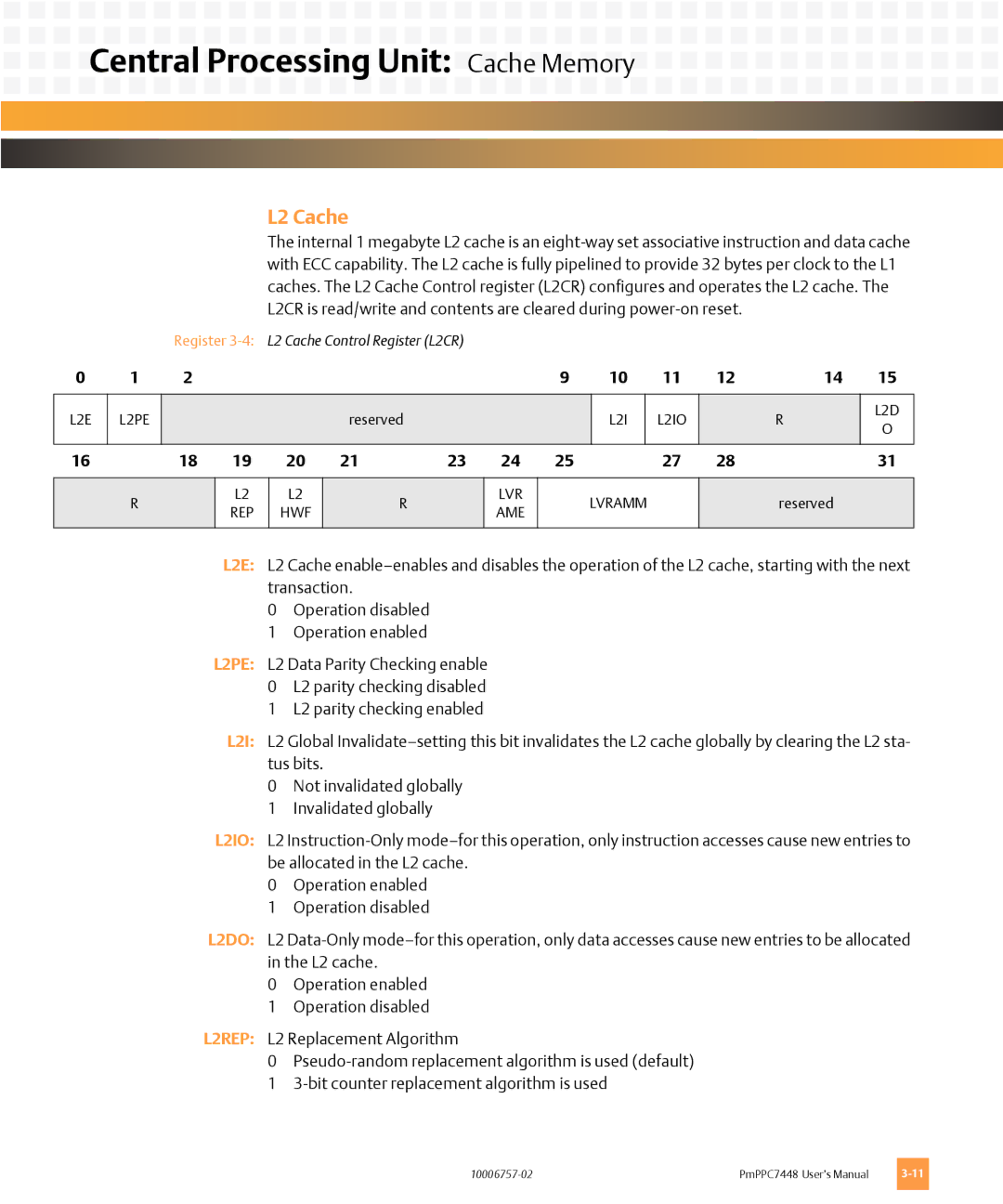

L2 Cache

The internal 1 megabyte L2 cache is an

Register

0 | 1 | 2 |

|

|

|

|

| 9 | 10 |

| 11 | 12 | 14 | 15 | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L2E | L2PE |

|

|

| reserved |

|

|

|

| L2I |

| L2IO |

| R | L2D |

|

|

|

|

|

|

|

|

| O | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16 |

| 18 | 19 | 20 | 21 | 23 | 24 | 25 |

|

|

| 27 | 28 |

| 31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| R |

| L2 | L2 | R |

| LVR |

| LVRAMM |

|

| reserved |

| ||

|

| REP | HWF |

| AME |

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L2E: L2 Cache

0Operation disabled

1Operation enabled

L2PE: L2 Data Parity Checking enable

0L2 parity checking disabled

1L2 parity checking enabled

L2I: L2 Global

0Not invalidated globally

1Invalidated globally

L2IO: L2

0Operation enabled

1Operation disabled

L2DO: L2

0Operation enabled

1Operation disabled

L2REP: L2 Replacement Algorithm

0

1

PmPPC7448 User’s Manual |