EPM 9650/9800 Meters

Page

EPM 9650/9800 Meters Modbus Protocol & Register Map

Limitation of Warranty

Customer Service and Support

Product Warranty

Statement of Calibration

Table of Contents

Page

Page

Page

Communication Data Formats

Page

Modbus Register Map Notes

Logs, Port Control and Updating Programmable Settings

EPM Programmable Settings Blocks

EPM Log Formats

Register Block Titles with Descriptions

Page

Xii

Appendix a Glossary

Xiv

Slave Address and Broadcast Request

Introduction

Communication Packets

Function Code Description Hex Dec

Function Codes

Function Codes

Function Code 03-Read Holding Registers

Function Code 6 Example Master Packet Slave Packet

Function Code 06-Preset Single Register

Function Code 10-Preset Multiple Registers

Data Starting Address

CRC Error Checksum Algorithm

Function Code 10 Example Master Packet Slave Packet

Exception Response Error Codes

Dead Time

Function Code Description

Modbus Extensions

Modbus Extensions

Repeat Count RTU Framing Ascii Framing

Function Code 23H Read Holding Registers Multiple Times

Function Code

Function Code 42H Encapsulated DNP for LAN/WAN

Function Code 23H Example Response

Link Status

Error Code

Address

Client IP

Request PDU

Response PDU Field Name Hex DNP Field

Response PDU

Page

Chapter EPM Modbus Register Map

Page

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

VAH

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

02771 232 Limit States, Value Comparisons 02772 16-31

VAH

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

Time of Use Current Month Label Block

DNP

DNP

DNP

F12 KYZ Output Accumulation Block

Analog Input Modules Data States

F19

F57

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

Reset Active TOU Time Stamp

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

Digital Output Snapshot Log Header

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

DNP

Custom DNP Definition Block for Analog Input Object

47369-47424 Point 1 Point

DNP

DNP

DNP

DNP

DNP

DNP

DNP

Customizable Modbus Map Settings Block

DNP LAN/WAN

DNP

DNP

DNP

DNP

DNP

DNP

DNP

Fixed Length String

Enumeration

DNP

Bytes

Type F1 Null Terminated Ascii String

Type F2 Fixed Length Ascii String

Register String

Date

Type F3 Time Stamp

Unit

Day of Week

Type F4 Day of Week

Type F5 Secondary 1 Cycle RMS Voltage or Current

Secondary

Byte unsigned integer Hex

Byte unsigned integer Decimal

Type F6 High Speed Input Delta and Current State

VAR secondary

Byte signed integer Hex

Most significant bit Byte integer Decimal

Most significant bit Compliment

Address Value 0390H Decimal

Type F8 Power Factor

Quadrant Value Hex Dec

Address Value 0C10H Decimal

Angle

Type F9 Angle

Most significant bit

Type F10 Percentage

Nibbles Digit Unit VAh

Type F11 Energy Counter Packed BCD / Secondary

Type F12 Energy Counter Binary / Secondary

Byte unsigned integer

Type F13 Phase Sequence

Type F14 Average Status

Value Hex

Interpretation

Type F15 Limit States

Bits Points Limit Passed

Bits

Type F16 Low Speed Input States

Byte

Input

Type F17 External Digital Input States

Accumulated Transitions

Type F18 External Input Accumulations

Type F19 Energy Counter Packed BCD / Primary

Type F20 Energy Counter Binary / Primary

Nibbles Digit Unit

Type F21 Year

Type F22 TOU Profile per Day

Day Leap Year

Type F23 TOU Profile Status

Day

Address35107 Value0001H Decimal1

Nibbles

Type F24 TOU Daily Profile Register Assignment

Value Hex Register

Period

Decimal Month

Type F26 TOU Calendar DST Enable / Average Selection

Type F25 TOU Profile Monthly End Day

Selection

Decimal Purpose

Type F27 TOU Upload Calendar Window Sequence / Status

Average

Address36609 Value0DH Decimal13 Meaning Window

Type F28 TOU Upload Calendar Window ID

Type F29 TOU Upload Calendar Window Data

Type F32 TOU Calendar Header Status / Year Status

Type F30 TOU Upload Calendar Window Checksum

Type F31 TOU Calendar Selection

Celsius

Type F33 Temperature

Most significant bit Decimal

Bits Limit Logic T/F

Type F35 Relay Delays

Type F34 Limit and Relay Logic States

Bits Limit State NO/NC

Type F37 Relays Pending Update

Type F36 Desired Relay States

Bits Point

Update?

Type F38 Shadowed Relay States

Type F39 Confirmed Polled Relay States

Type F40 Valid Flags for Confirmed Relay States

Type F41 Locked Relays, Relays

Locked?

Type F42 Locked Relay States

Bits Point Relay

Addr

Type F43 Miscellaneous Flags

Bit Point

Type F44 Digital Input Module Data Status

Bits Point Digital Input

Bits Point Analog Input Module Status

Type F45 Analog Input Modules Data Status

Reg Bit Point

Type F4 Low Byte of Modbus Register Signed

Type F46 High Byte of Modbus Register Signed

Type F47 High Byte of Modbus Register Unsigned

Type F49 Low Byte of Modbus Register Unsigned

Type F52 Four-Byte Signed

Type F50 Two-Byte Signed

Type F51 Two-Byte Unsigned

Type F53 Four-Byte Unsigned

Type F54 Eight-Byte Signed

Type F55 Eight-Byte Unsigned

Type F58 12-bit RTU Sanity Register

Type F56 Flicker Countdowns

Type F57 Accumulation in the Interval

0400H

Type F59 12-bit RTU Current, Voltage, W, VAR

Addr 53250

Addr 53256

Digit Unit KWh primary

Type F60 Energy Counter

Type F61 12-bit RTU Frequency

0810H

Most Significan Bit

Type F62 Scaled Pulse Accumulation, Aggregation or Average

Byte Signed Integer

Addr Hex

Byte Hex

Type F63 Log Index

Type F64 Scaled Energy

Type F65 Scaled Energy Setting

Bit Meaning

Type 66 TOU Upload Calendar Window Locked to Port

Type 67 K-Factor

Factor

Chapter Modbus Register Map Notes

Modbus Register Map Notes

Page

Downloading Logs Overview

Byte Range

Page

Steps for Downloading a Log

Downloading Time Stamps with Examples

Address Description Example Value

Page

Downloading Records with Examples

Page

Downloading Logs with Auto Index and Modbus Extensions

Auto Increment Log Window 0x09A3F

Download using Auto Increment Window Sequence

Auto Increment Window Index 0x099FF

Port Locking Overview

Reception

Sequence for Port Locking

Transmission

Port Unlocking Sequence

Updating Programmable Settings Overview

Sequence for Updating Programmable Settings

Clear on New Period / Freeze Period Selection

Modifications to Time of Use

Register Meaning

Value

Weekly Freeze Day of Week / Freeze Hour

Modbus Register Dual Port Address Name Decimal Hex

Manual Adjustment Interface

Calibration Interface

Page

Direct Adjustment Interface

As Stored LSB

Decimal Scaled

Change by Multiply by

Decimal Scaled Meaning

Change by Modified by

Chapter EPM Log Formats

Log Formats Overview

Historical Log 1 Record Size

Profile Information is in the Programmable Settings Block

Historical Log 1 Format

Historical Log 1 Data Pointers

Format Range Description

Profile Information is in the Programming Settings Block

Historical Log 2 Format

Historical Log 2 Record Size

Historical Log 2 Data Pointers

Limit Trigger Log Format

Limit Snapshot Log Format

Format Range Description

Waveform Trigger Log Format

VAN, VBN, VCN, IA, IB, IC, IAUX, VAB, VBC, VCA

High Speed Digital Input States

Above Limits

VAN VBN VCN Vaux IA IB IC Iaux

Example for EPM 9650 with 300V hardware

Formula to use for EPM 9650s with 300V hardware is

Example for EPM 9650 with regular hardware or EPM

Waveform Samples Log Format

Page

HS RMS

Page

Current Sample Examples Actual 1st Byte 2nd Byte Straight

Current Sample Examples Actual 1st Byte Straight 2nd Byte

Current Sample Examples Actual Ist Byte Straight 2nd Byte

High Speed Digital Input States

Power Quality Cbema Log Format

VAN VBN VCN Vaux IA IB IC Iaux VAB VBC VCA

11 High Speed Digital Input States

Digital Input Log Format

Byte Format Range

13 States of the Internal Digital Inputs

Format Range

Digital Input Snapshot Log Format

Digital Input Snapshot Data Pointers

Page

Digital Output Log Format

16 Relay Valid Bits

18 Relay Logic Gate Ouputs

Page

Digital Output Snapshot Log Format

Digital Output Snapshot Data Pointers

Byte Format Range Description

Flicker Log Format

System Event Log Format

Power Record

Password Record

Change Time

Change Programmable Settings

Change Firmware

Test Mode

Log Download

Feature Reset

Communication Settings Block Specifications

Communication Settings Block

Limit Settings Block

Structure for a combination is

Structure for the Direction and Combination byte is

Data Pointer 4-Byte Structure

Historical Log Settings Block

Pollable information would consist

Format Description

Set Points

Waveform/CBEMA Settings Block

Waveform & PQ enable

Sample Rate

External Digital Output Module Settings Block

High Speed Inputs Settings Block

External Digital Input Module Settings Block

External KYZ Output Module Settings Block

External Analog Input Module Settings Block

External Analog Output Module Settings Block

KYZ Output Relay Byte Energy Assignments

11 CT & PT Ratio Settings Block

Hookup and Time Settings Block

Average Settings Block

Exception Profile Block

Port 2 Baud Rate Values

Device Label Settings Block

Network Settings Block

Mode 2 Network Mode 2 byte

Server / Service Enable

Energy Direction Block

Display Configuration Block

Block Window Average External Synchronization Block

Proper Values for BWA Synch Mask Assigned Inputs

External Module Software Interface Block

Test Mode Configuration Block

Full Scale Block

External Module Port Assignments

External Module Port Assignment Block

Manual Control Relay Block

Value Assignments

26 I2t and V2t Threshold Block

Internal KYZ Settings Block 46330-46372- EPM 9800 Only

Internal Input Pulse Accumulation Scale Factor Block

Channel Assignment

Internal KYZ Enable Assignment Bit

Internal KYZ Channel Assignment

Width milliseconds

End of Interval Pulse Byte Value Enable

Internal Input Pulse Accumulation Unit Label Block

ElectroLogic Block

Format of a Relay Structure

Value Update

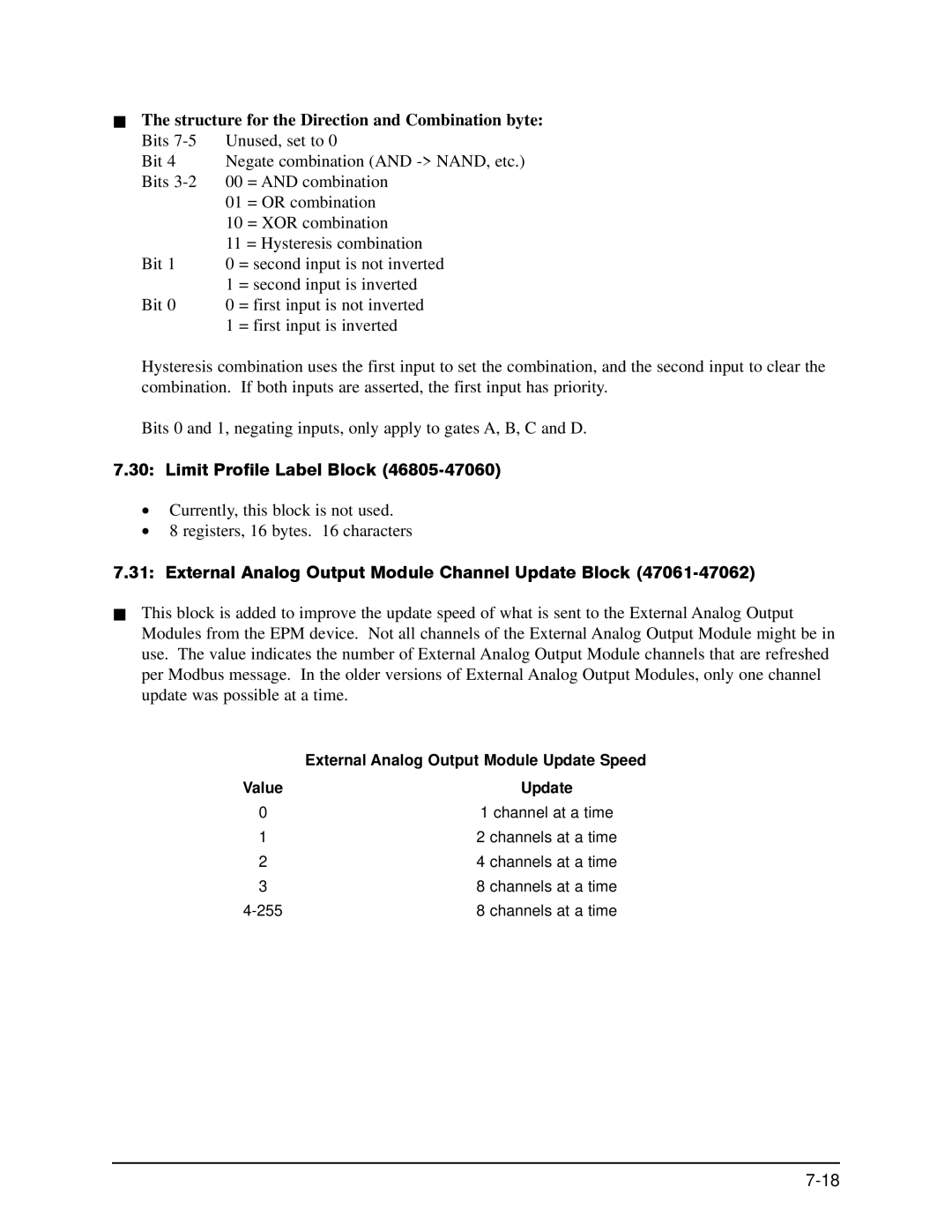

External Analog Output Module Channel Update Block

External Analog Output Module Update Speed

Structure for the Direction and Combination byte

Value Time 1 Minute Interval

Miscellaneous DNP Settings Block

Bytes to be Sent Out

DNP Freeze Date & Time 4 registers, 8 bytes

Registers Byte Name Range

Custom DNP Definition Block for Analog Input Object 30

Custom DNP Definition Block for Binary Counter Object 20

Class Assignments for Counter Change Event Bit

Custom DNP Definition Block for Binary Output Object 10

Bit Resets

Custom DNP Definition Block for Binary Input Object 1

Analog Input Labels Block

Custom DNP Definition Block for Global Values

Analog Input Scaling Factors Block

External Digital Input Module Labels Block

Index Baud Rate INP

Internal Modem Card Settings Block

EPM Internal Modem Card Baud Rate Settings

Bit 2 Bit Parity

Internal Modem Card Bitmap Settings

Numeric Pager ID 7 bytes Reserved for future use

Modem Feature Dial-Out Mask Event Mask

Bit Event Description

Customizable Modbus Map Settings Block

Email Client Settings Network Settings 10/100 Card

Enable / Disable 1 Register

Email Mode Bitmap

Connection Type/Option Bits

FTP Client Network Settings 10/100 Card

GE EGD Protocol Network Settings 10/100 Card

DNP LAN/WAN

Validate Connection Count 1 byte unsigned integer

DNP LAN/WAN Bitmap

Line Number 2 bytes Point Number 1 byte

Energy Scale Settings

Customizable Modbus Map Format Block

Update Settings Block

Page

On Time

Device Indentification Block

Real Time Block

Current Time

One Second Block

1 Cycle Block

Tenth Second Block

Minimum Block

Thermal Average Block

Maximum Block

Maximum Time Stamp Block

Harmonic Magnitude Block

Harmonic Phase Block

Phase Angle Block

14 THD/K-Factor Block

Time of Use Period Time Stamp Block

Digital Input Block

Primary Accumulation Block

Time of Use Frozen Block

Time of Use Active Register Block

Time of Use Prior Month Register Block

Time of Use Prior Month Total Block

Time of Use Active Total Block

Time of Use Frozen Label Block

Temperature

Time of Use Current Month Total Block

Time of Use Prior Month Label Block

Limit Combination Block

Reset Time Block

Analog Input Block

Relay Logic Block

Input Module Data Status Block

Test Mode Block

KYZ Output Accumulation Block

Flicker Status Block

Cumulative Demand Block

Energy and Pulses in the Interval Block

Flicker Countdown Block

Time of Use Active Cumulative Demand Block

TOU Current Month Continuous Cumulative Demand Block

Total Average Power Factor Block

TOU Active Continuous Cumulative Demand Block

Log Index Block

Enhanced Programmable Settings Block

Reset Active Time of Use Time Stamp

Enhanced Factory Settings Block

Negative Maximum Pulse Aggregation Average Block

Historical Log 1 Snapshot Header

Time of Use Calendar Block

Time of Use Upload Calendar Block

Limit Snapshot Log Header

Historical Log 2 Snapshot Header

Limit Trigger Log Header

Digital Input Log Header

System Event Log Header

Flicker Log Header

Waveform Trigger Log Header

Valid Bitmap Undefined

PQ Cbema Log Header

Reset Log Header

Waveform Samples Log Header

External Device Information Block Header

Window Index Block

Direct Memory Access Header

Device History Block Header

Page

Window Mode Block

Page

Window Block

Page

„ Auto Increment Window Index 1 register, 2 bytes

„ Auto Increment Configuration 1 Register, 2 bytes

Auto Increment Window Block

Byte Format Range Description

Alarm Block

„ Auto Increment Log Window 64 registers, 128 bytes

Last Alarm Snapshot

Format Description

Port Control Block

Port Control Lock States Register High Byte Low Byte

Receive and Transmit Buffers Port

Transmit

Current, Voltage, W, VAR 1 register, 2 bytes

Energy Preset Block

97 12-bit RTU Block

Action Block Resetting EPM Registers

Voltage Calibration Inputs Model

Current Calibration Inputs Model

Calibration Modification Block

Factory Calibration Block

Ctpt Compensation Calibration Block

Relay Locking Action Selection Values ValueDescription

Device Identification Block 2

Operational Communication Settings Block

Diagnostic Block

Xilinx Version / 320 Xilinx Version

Sealing Switch State

DSP Diagnostic Block

Password Block

Firmware Variation Strings

New Password a New Password B

Nvram Configuration Values

Dynamic Configuration Block

Hardware Option Settings

Hardware Options Block

CT’s PTs

Banked Executable Option Settings Modbus Register 9650 9800

EPM Forms Code

Amp 65364 High

300 V 65364 Low

Flash Control Block

Page

Flash Locked Port

GE Communicator EXT Flash Code Hex Line

Enhanced Serial Number

Serial Number

Page

Glossary

Eeprom

LCD

Nvram

Glossary-5

THD