Model 7112 T1 DSU/CSU

Copyright � 1998 Paradyne Corporation All rights reserved

Contents

Configuring the DSU/CSU

Monitoring the DSU/CSU

Messages and Troubleshooting

MIB Descriptions

Technical Specifications Glossary Index

About This Guide

Document Purpose and Intended Audience

Document Summary

Product-Related Documents

Model 7112 T1 DSU/CSU Features

About the T1 DSU/CSU

Typical DSU/CSU Configurations

Typical Configuration through a T1 network

Front Panel LED Status Indicators

User Interface Types

Rear Panel Interface Connections

Snmp Management Capabilities

Management Information Base MIB Support

Network

Using the Ascii Terminal Interface ATI

Accessing the ATI

Connecting to the Terminal Port

Initiating an ATI Session

Select

Screen Work Areas

Screen Format Types

What Affects Screen Displays

Use the screen format

Status Test Configuration Control

Navigating

Keyboard Keys

Press

Procedure

Switching Between Screen Work Areas

Screen Function Keys

For the screen Select Press Enter to Function

Example

Ending an ATI Session

Using the Ascii Terminal Interface ATI

Configuring the DSU/CSU

Entering Device and System Information

Main Menu → Control → Device

Configuring the DSU/CSU

Configuration Option Areas

Configuration Option Area Configuration Option Set

Accessing and Displaying Configuration Options

Saving Configuration Options

Main Menu → Configuration Load Configuration From

If you select Then

Assigning DS0 Channels to the Data Port

Cross Connect Assignments

Using the Block or Acami Assignment Method

Displaying DS0 Channel Assignments

Using the Individual Channel Assignment Method

Clearing DS0 Channel Assignments

Security

Overview

Creating a Login

Main Menu → Control → Administer Logins

On the Administer Enter Logins screen, for

Deleting a Login

Resetting the DSU/CSUs COM Port or Factory Defaults

ATI Access

If entering yes to prompt Then

Effective Access Level

Effective Access Levels ATI Access to Menu Functions

Controlling Snmp Access

Assigning Snmp Community Names and Access Levels

Connection Failed

Limiting Snmp Access through the IP Addresses

Security

IP Addressing

IP Addressing

IP Addressing Examples

Local Addressing Only No FDL

Subnet

FDL Connection ± Extending Subnet for FDL

NMS a NMS B

FDL Connection ± Unique FDL Subnet

LAN a

If using Then assign

Assigning IP Addresses and Subnet Masks

IP Addressing

Monitoring the DSU/CSU

What to Monitor

DSU/CSU LEDs

Main Menu → Status → Display LEDs

System LEDs

Fail

SIG ± Network Signal

Alarm

EER ± Excessive Error Rate

Network LEDs

Port LEDs

Status Screen Commands

System and Test Status

Main Menu → Status → System and Test Status

Health and Status Messages

Yyyyyyyy

Self-Test Results

Xxxxxxxx

Test Status Messages

Test Status Messages Meaning

Cross Connect Status

Main Menu → Status → Cross Connect Status

Network Time Slot Fields top Indicate

Network Performance Statistics

Main Menu → Status → Network Performance Statistics

Summary Information

Interval Table

Worst Interval

Ethernet Port Status

Hour Totals

Main Menu → Status → Ethernet Port Status

Management Protocol Statistics

Main Menu → Status → Management Protocol Statistics

March

Testing

Detecting Problems

Status Specific Trap Screen

Accessing the Test Menu

Main Menu → Test

Running Network Tests

Main Menu → Test → Network Tests

Line Loopback

Payload Loopback

Repeater Loopback

Remote Send Line Loopback

Test Patterns for the Network

Running Data Port Tests

Main Menu → Test → Data Port Tests

Data Terminal Loopback

CSU DSU

Data Channel Loopback

Send V.54 Up/Down Sequences

Send FT1 Up/Down Sequences

Test Patterns for the DTE

Lamp Test

Ending an Active Test

Messages and Troubleshooting

Configuring Snmp Traps

Snmp Traps

Device Messages

Device Messages 1 What Message Indicates What To Do

Device Messages 2 What Message Indicates What To Do

Troubleshooting

Troubleshooting 1 Symptom Possible Cause Solutions

Troubleshooting 2 Symptom Possible Cause Solutions

Messages and Troubleshooting

Configuration Option Tables

Select To Access To Configure

Test Timeout

System Options Menu

Table A-1. System Options

Self Test

Network Interface Options Menu

Table A-2. Network Interface Options 1

Line Framing Format

Line Coding Format

Bit Stuffing Possible Settings 62411, Part68, Disable

Line Build Out LBO Possible Settings 0.0, ±7.5, ±15, ±22.5

Table A-2. Network Interface Options 2

FDL Management Link

Table A-2. Network Interface Options 3

Network Initiated Line Loopback LLB

Network Initiated Payload Loopback PLB

Table A-2. Network Interface Options 4

Ansi Performance Report Messages

Circuit Identifier

Assign By Available Settings Block, ACAMI, Channel

Cross Connect Assignments

Table A-3. Cross Connect Assignments

Synchronous Data Port Assignments

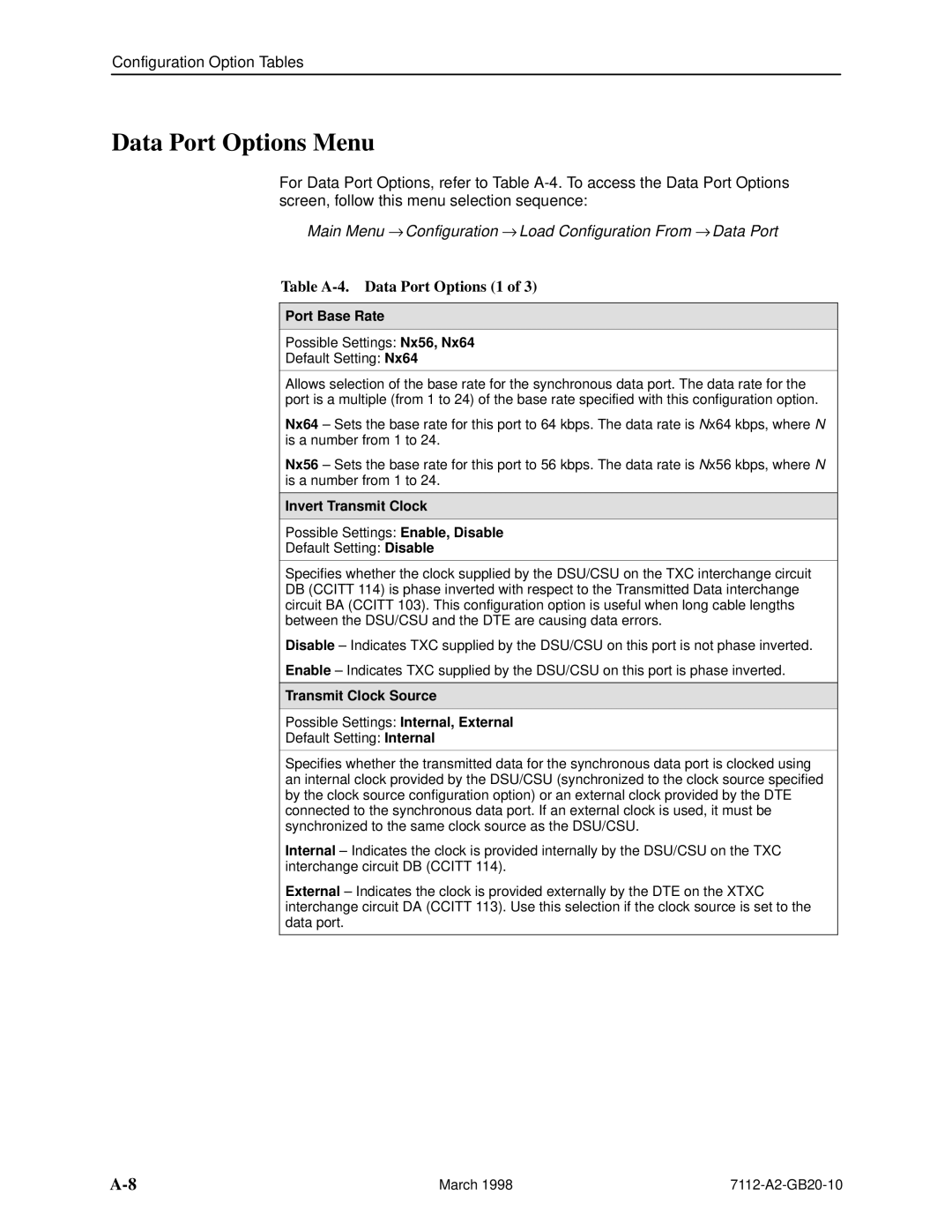

Data Port Options Menu

Table A-4. Data Port Options 1

Port Base Rate

Invert Transmit Clock

Action on Network Yellow Alarm

Table A-4. Data Port Options 2

Invert Transmit and Received Data

Table A-4. Data Port Options 3

Port Use Possible Settings 802.3, Version 2, Disable

Ethernet Port Options Menu

Table A-5. Ethernet Port Options 1

Terminal Port Options

Table A-5. Ethernet Port Options 2

Table A-6. Terminal Port Options 1

Character Length

Login Required

Port Access Level Possible Settings Level 1, Level 2, Level

Table A-6. Terminal Port Options 2

Stop Bits

Telnet Session Options

Table A-6. Terminal Port Options 3

Table A-7. Telnet Session Options 1

Table A-7. Telnet Session Options 2

Snmp Menu

General Snmp Management Options

Table A-8. General Snmp Management Options 1

Name 2 Access

Snmp NMS Security Options

Table A-8. General Snmp Management Options 2

Table A-9. Snmp NMS Security Options 1

Access Level

Table A-9. Snmp NMS Security Options 2

Snmp Traps Options

Table A-10. Snmp Traps Options 1

Snmp Traps

Number of Trap Managers

Link Traps Possible Settings Disable, Up, Down, Both

Table A-10. Snmp Traps Options 2

Enterprise Specific Traps

Link Trap Interfaces

Configuration Worksheets

Configuration Option Settings default in Bold

Enable, Disable

Worksheets

Disable, Enable

ESF, D4

Blank

Nx64, Nx56

Internal, External

Configuration Option Settings

Ethernet Port

Snmp

Snmp NMS Security

Worksheets

MIB Descriptions

MIB II ± RFC 1213 and RFC

System Group

SysDescr system

SysName system

Interfaces Group

Physical 1 ± Layer

Datalink/subnetwork

Internet 4 ± Layer

Version Hardware Revision º

EthernetCsmacd6 ± Used for

Up1

Testing3 state

IfInErrors ifEntry

IfInOctets ifEntry

Extension to Interface Table ifXTable

IfName ifXEntry

IfXEntry

Interface Stack Group

IfStackEntry1

IfStackEntry2

Interface Test Table

Generic Receive Address Table

IP Group

Invalid

Exist. The following objects must

Be specified

On next

Icmp Group

TCP Group

UDP Group

Do not specify the following

Snmp Group

Transmission Group

Table C-6. Transmission Group Objects Description

Transmission

DS1 Near End Group Configuration Table Objects

Dsx1ConfigEntry

DS1/E1 ± RFC

Dsx1ESF2 ± Indicates

Dsx1SendResetCode4 ±

Dsx1B8ZS2 ± Indicates

Dsx1AMI5 ± Indicates

Dsx1SendNoCode1 ±

Dsx1NoAlarm1 ± No

Dsx1LossOfSignal64 ±

Dsx1NoLoop1 ± The T1

Dsx1PayloadLoop2 ±

LoopTiming1 ±

LocalTiming2 ±

ThroughTiming3 ±

Dsx1other1 ± Snmp

DS1 Near End Group Current Table Objects

Dsx1CurrentEntry

DS1 Near End Group Interval Table Objects

Dsx1IntervalEntry

Dsx1IntervalEntry10

DS1 Near End Group Total Table Objects

Dsx1TotalEntry

Ethernet-Like MIB ± RFC

RS-232-Like MIB ± RFC

DS1 Fractional Group

Number of RS-232-Like Ports Object

Rs232PortEntry

Disabled2 ± Does not

Asynchronous Port Table Objects

Rs232AsyncPortEntry

Synchronous Port Table Objects

Rs232SyncPortEntry

Input Signal Table Objects

Rs232InSigEntry

Output Signal Table Objects

Rs232OutSigEntry

Generic Interface Extension MIB ± RFC

Generic Interface Test Table Objects

IfExtnsTestEntry

TestMon Qrss wellKnownTests

± Starts a Monitor 511 test on the interface

InSyncNoBitErrors

InSyncWithBitErrors

InProgress3 ± Test is

NotSupported4 ± Requested

Device Configuration Variable pdn-common

Enterprise MIB Object

Device Security, pdn-security pdn-common

Device Traps, pdn-traps pdn-common

MIB Descriptions

Standards Compliance for Snmp Traps

Trap warmStart

Trap authentificationFailure

Snmp Trap Description Possible Cause

Traps linkUp and linkDown

Interface LinkUp/Down Variable-Bindings Possible Cause

Traps enterpriseSpecific

Trap What It Indicates Possible Cause

Page

Standards Compliance for Snmp Traps

Cables and Pin Assignments

Cabling Overview

Modular RJ48C-to-RJ48C T1 Network Interface Cable

Modular RJ48C-to-CA81A T1 Network Interface Cable

Terminal Port EIA-232 Connector

10BaseT Connector

Signal Direction Pin #

Use Pin #

Serial Crossover Cable

Pin

DTE V.35 Connector

Signal

Direction Pin Socket Connector

Cables and Pin Assignments

Technical Specifications

Model 7112 DSU/CSU Technical Specifications 1

Model 7112 DSU/CSU Technical Specifications 2

Glossary

Configuration option

Default

Digital signal

Channel allocation

Factory defaults

EIA-232

Enterprise MIB

Enterprise-specific

Reset

Loopback

Manager Snmp

Multiplexing

RS-232

Self-test

Subnet

Subnet address

Yellow Alarm

In-8 pattern

Pattern

Index

Numbers

IN-2

IN-3

IN-4