Configuration Options

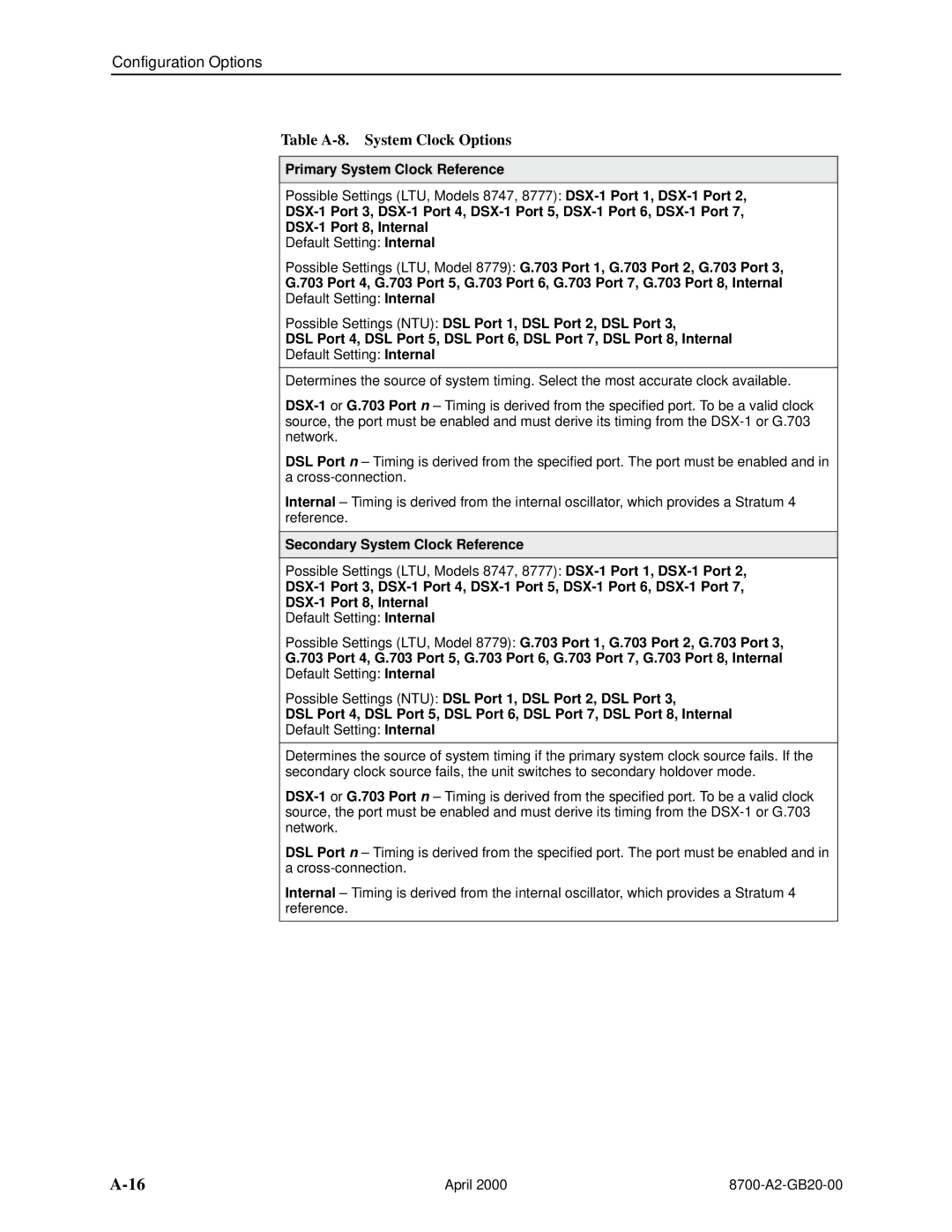

Table A-8. System Clock Options

Primary System Clock Reference

Possible Settings (LTU, Models 8747, 8777):

Default Setting: Internal

Possible Settings (LTU, Model 8779): G.703 Port 1, G.703 Port 2, G.703 Port 3,

G.703 Port 4, G.703 Port 5, G.703 Port 6, G.703 Port 7, G.703 Port 8, Internal Default Setting: Internal

Possible Settings (NTU): DSL Port 1, DSL Port 2, DSL Port 3,

DSL Port 4, DSL Port 5, DSL Port 6, DSL Port 7, DSL Port 8, Internal Default Setting: Internal

Determines the source of system timing. Select the most accurate clock available.

DSL Port n – Timing is derived from the specified port. The port must be enabled and in a

Internal – Timing is derived from the internal oscillator, which provides a Stratum 4 reference.

Secondary System Clock Reference

Possible Settings (LTU, Models 8747, 8777):

Default Setting: Internal

Possible Settings (LTU, Model 8779): G.703 Port 1, G.703 Port 2, G.703 Port 3,

G.703 Port 4, G.703 Port 5, G.703 Port 6, G.703 Port 7, G.703 Port 8, Internal Default Setting: Internal

Possible Settings (NTU): DSL Port 1, DSL Port 2, DSL Port 3,

DSL Port 4, DSL Port 5, DSL Port 6, DSL Port 7, DSL Port 8, Internal Default Setting: Internal

Determines the source of system timing if the primary system clock source fails. If the secondary clock source fails, the unit switches to secondary holdover mode.

DSL Port n – Timing is derived from the specified port. The port must be enabled and in a

Internal – Timing is derived from the internal oscillator, which provides a Stratum 4 reference.

April 2000 |