R

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU

©

XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI EXPRESS is a registered trademark of

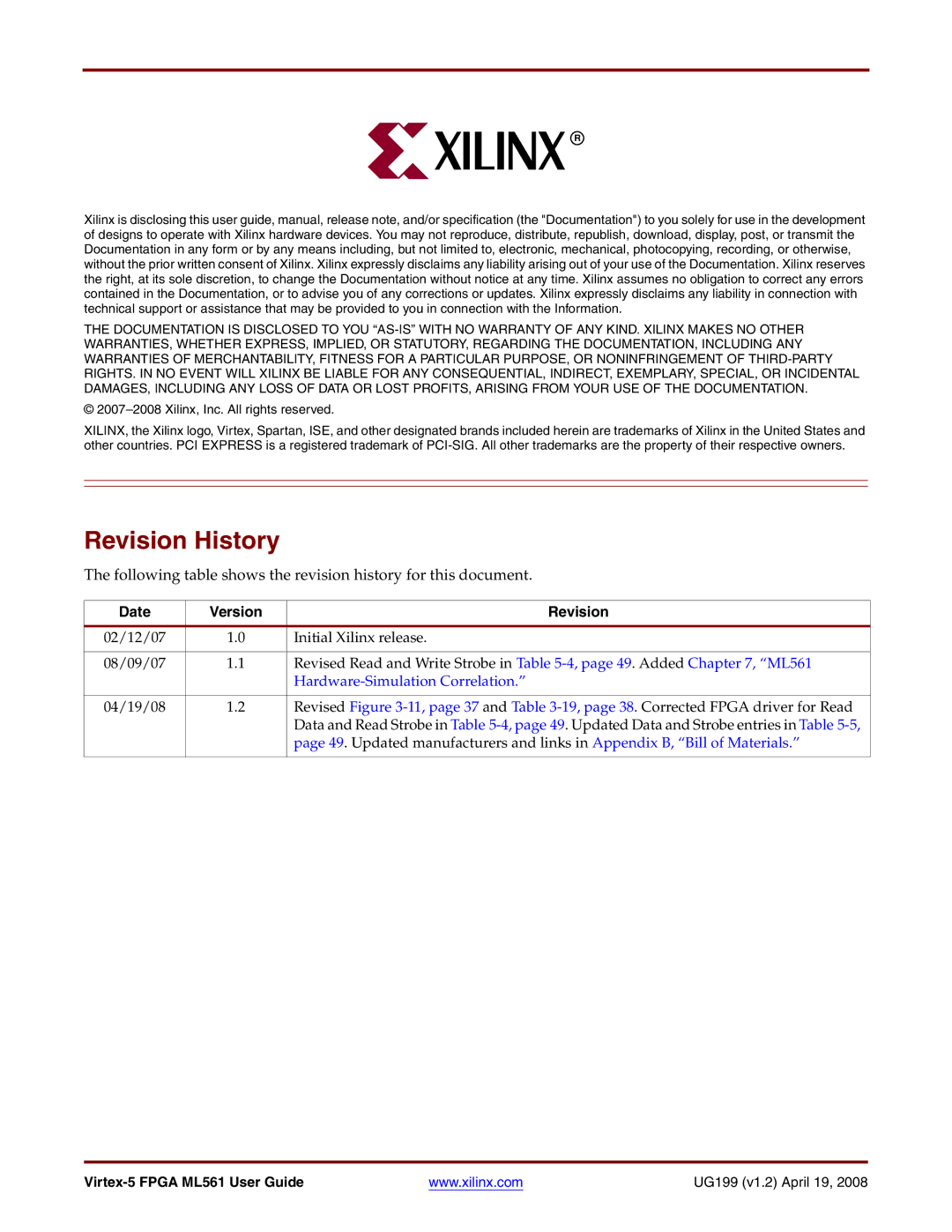

Revision History

The following table shows the revision history for this document.

Date | Version | Revision |

|

|

|

02/12/07 | 1.0 | Initial Xilinx release. |

|

|

|

08/09/07 | 1.1 | Revised Read and Write Strobe in Table |

|

| |

|

|

|

04/19/08 | 1.2 | Revised Figure |

|

| Data and Read Strobe in Table |

|

| page 49. Updated manufacturers and links in Appendix B, “Bill of Materials.” |

|

|

|

www.xilinx.com | UG199 (v1.2) April 19, 2008 |