R

External Interfaces

External Interfaces

The external interfaces of the

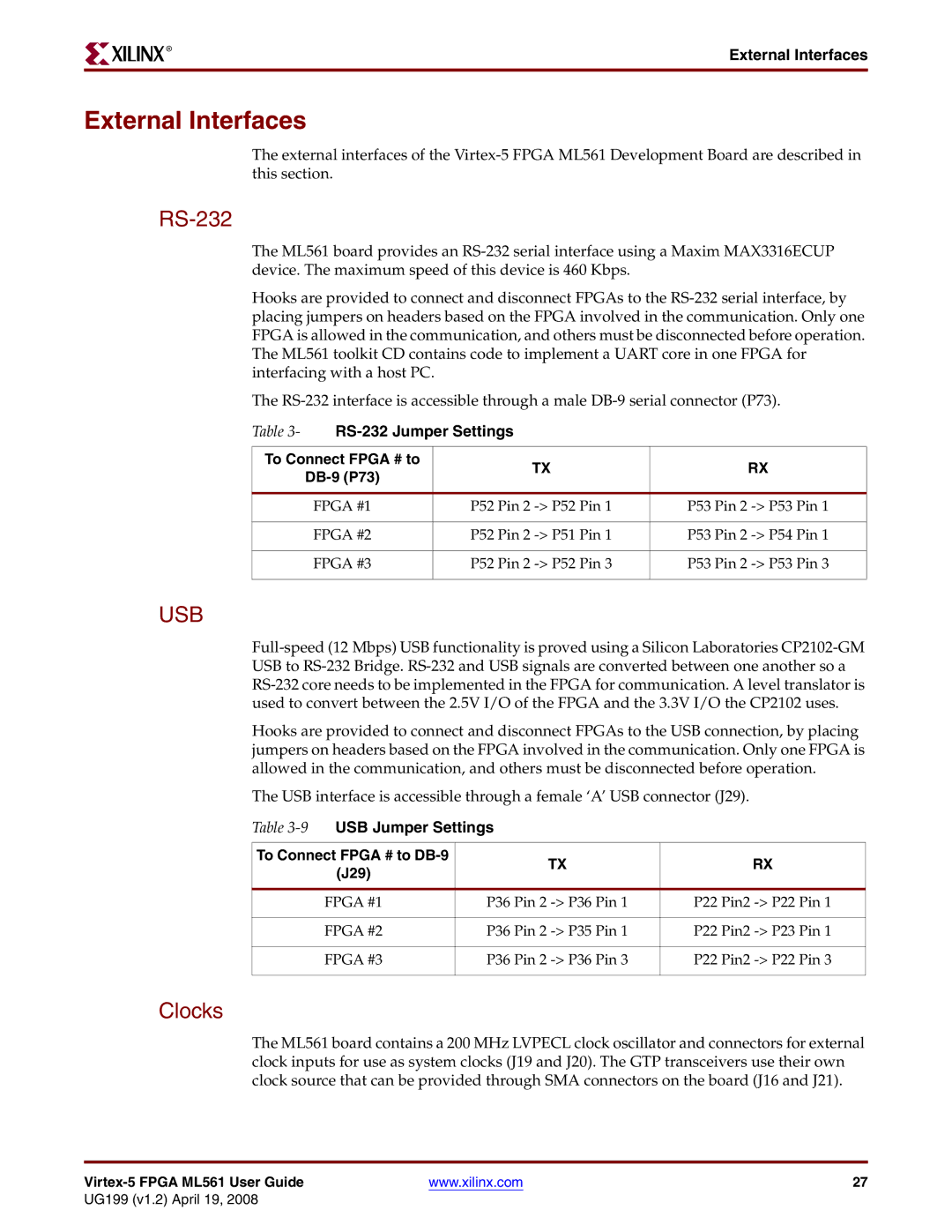

RS-232

The ML561 board provides an

Hooks are provided to connect and disconnect FPGAs to the

The

Table 3-8: RS-232 Jumper Settings

To Connect FPGA # to | TX | RX | |

|

| ||

|

|

| |

FPGA #1 | P52 Pin 2 | P53 Pin 2 | |

|

|

| |

FPGA #2 | P52 Pin 2 | P53 Pin 2 | |

|

|

| |

FPGA #3 | P52 Pin 2 | P53 Pin 2 | |

|

|

|

USB

Hooks are provided to connect and disconnect FPGAs to the USB connection, by placing jumpers on headers based on the FPGA involved in the communication. Only one FPGA is allowed in the communication, and others must be disconnected before operation.

The USB interface is accessible through a female ‘A’ USB connector (J29).

Table

To Connect FPGA # to | TX | RX | |

(J29) | |||

|

| ||

|

|

| |

FPGA #1 | P36 Pin 2 | P22 Pin2 | |

|

|

| |

FPGA #2 | P36 Pin 2 | P22 Pin2 | |

|

|

| |

FPGA #3 | P36 Pin 2 | P22 Pin2 | |

|

|

|

Clocks

The ML561 board contains a 200 MHz LVPECL clock oscillator and connectors for external clock inputs for use as system clocks (J19 and J20). The GTP transceivers use their own clock source that can be provided through SMA connectors on the board (J16 and J21).

| www.xilinx.com | 27 |

UG199 (v1.2) April 19, 2008