R

Conventions

Conventions

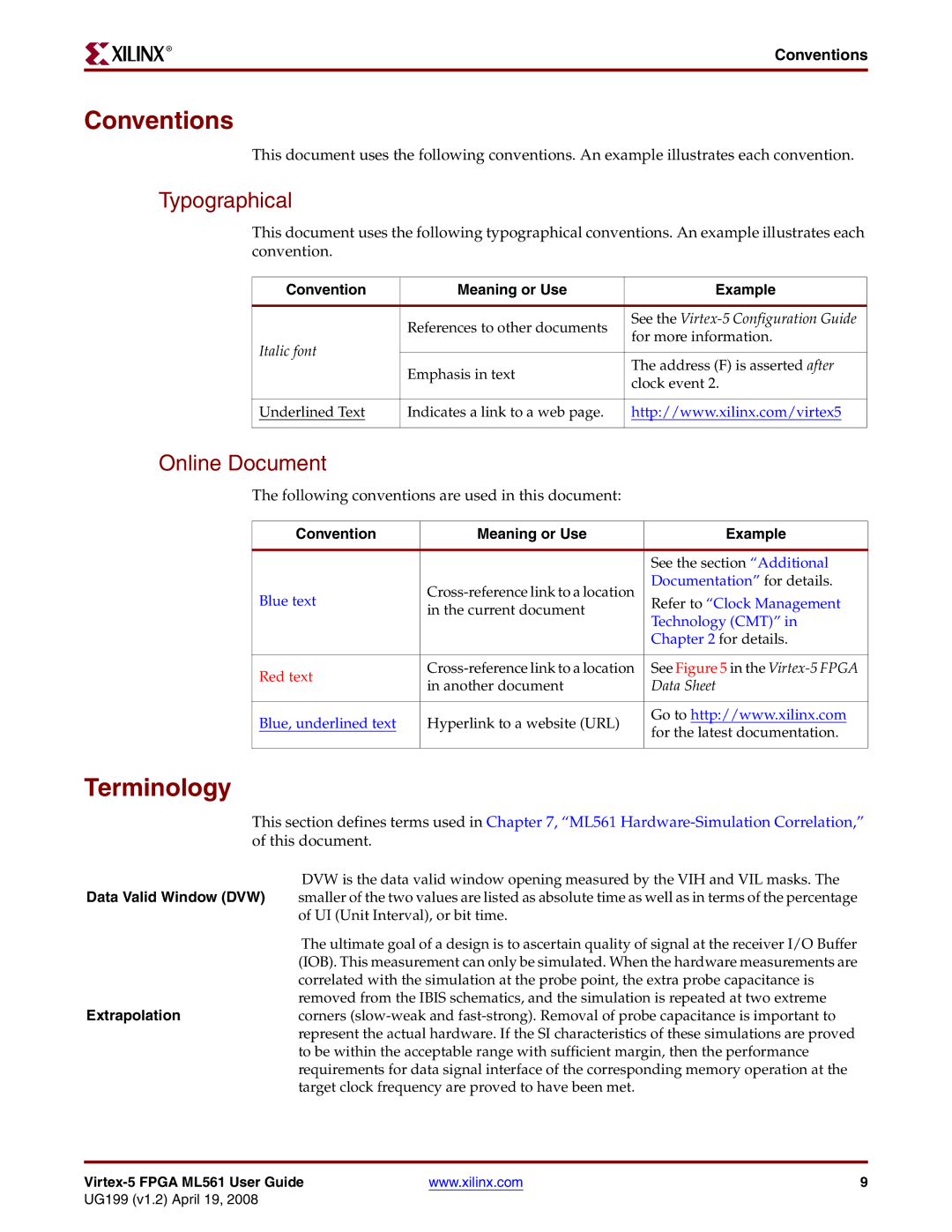

This document uses the following conventions. An example illustrates each convention.

Typographical

This document uses the following typographical conventions. An example illustrates each convention.

Convention | Meaning or Use | Example | |

|

|

| |

| References to other documents | See the | |

| for more information. | ||

Italic font |

| ||

|

| ||

Emphasis in text | The address (F) is asserted after | ||

| |||

| clock event 2. | ||

|

| ||

|

|

| |

Underlined Text | Indicates a link to a web page. | http://www.xilinx.com/virtex5 | |

|

|

|

Online Document

The following conventions are used in this document:

Convention | Meaning or Use | Example | |

|

|

| |

|

| See the section “Additional | |

| Documentation” for details. | ||

Blue text | Refer to “Clock Management | ||

in the current document | |||

| Technology (CMT)” in | ||

|

| ||

|

| Chapter 2 for details. | |

|

|

| |

Red text | See Figure 5 in the | ||

in another document | Data Sheet | ||

| |||

|

|

| |

Blue, underlined text | Hyperlink to a website (URL) | Go to http://www.xilinx.com | |

for the latest documentation. | |||

|

| ||

|

|

|

Terminology

This section defines terms used in Chapter 7, “ML561

DVW is the data valid window opening measured by the VIH and VIL masks. The

Data Valid Window (DVW) smaller of the two values are listed as absolute time as well as in terms of the percentage of UI (Unit Interval), or bit time.

The ultimate goal of a design is to ascertain quality of signal at the receiver I/O Buffer (IOB). This measurement can only be simulated. When the hardware measurements are correlated with the simulation at the probe point, the extra probe capacitance is removed from the IBIS schematics, and the simulation is repeated at two extreme

Extrapolationcorners

| www.xilinx.com | 9 |

UG199 (v1.2) April 19, 2008