HP 50g / 49g+ / 48gII graphing calculator

Advanced user’s reference manual

Page

Acknowledgements

Printing History

Page

Contents

Alog

Names

Algb

Amort

317

→COL

Delalarm

Delay

COL→

359

Expan

Findalarm

EXP2POW

Expand

IDIV2

Halt

IBP

Iferr

List

MIN

MAX

Maxr

Not

Parity

PA2B2

Parametric

Parsurface

3183

Roll

RND

Rnrm

Rolld

3226

Tail

Tabvar

→TAG

TAN

Utpc

Wireframe

Updir

Utpf

Contents

514

→ALG Apeek ARM→ ASM ASM→

610

Toff Tpar

Alrmdat

CST Exited Expr Iopar MASD.INI

Vpar

Contents of a Program

Understanding Programming

Examples of Program Actions

Calculations in a Program

Program Results

To enter a program

To enter commands and other objects in a program

Entering and Executing Programs

To store or name a program

3Q!Ì*4#3/* @Ë@Ï

To stop an executing program

3Q!Ì*4`3/*@Ï

@% @Ér # O4 /3 *!Ì Q3 @Ë@Ï

Program Keys Comments

Level

Osph K

To view or edit a program

To switch between entry modes

Viewing and Editing Programs

@%SPH% ˜

Creating Local Variables

Using Local Variables

Creating Programs on a Computer

`J!%SPH% @%SPH% ˜

Program Comments

`OSPHLV K

Evaluating Local Names

Defining the Scope of Local Variables

Compiled Local Variables

Creating UserDefined Functions as Programs

Key Programmable Description Command

Using Tests and Conditional Structures

Testing Conditions

To include a test in a program

Logical Functions

Using Logical Functions

Keys Programmable Description Command

TEST% L

Press !%BRCH% !%IF%

Using Conditional Structures and Commands

To enter if then END in a program

To enter IFT in a program

To enter Ifte in a program or in an algebraic

To enter if then Else END in a program

Press !%BRCH% @%#IF#%

Press !%BRCH% L!%IFTE%

To enter Case END in a program

Conditional Examples

Otst K

26 `52 J %TST%

Using Definite Loop Structures

Using Loop Structures

While … Repeat … END

To enter Start Next in a program

Start Next Structure

« … start finish Start loopclause Next … »

Press !%BRCH% !%START%

To enter Start Step in a program

Start Step Structure

« … start finish Start loopclause increment Step … »

Press ! %BRCH% … %START%

To enter for Next in a program

For Next Structure

« … start finish for counter loopclause Next … »

Press !%BRCH% ! %FOR%

To enter for Step in a program

For Step Structure

« … start finish for counter loopclause increment Step … »

Press ! %BRCH% … %FOR%

« … do loopclause Until testclause END … »

Using Indefinite Loop Structures

Do Until END Structure

To enter do Until END in a program

Duplicates n, stores the value into n

To enter While Repeat END in a program

While Repeat END Structure

« … While testclause Repeat loopclause END … »

Press !%BRCH% ! %WHILE%

To enter Incr or Decr in a program

Using Loop Counters

Press ! #MEM# %ARITH% %INCR% or %DECR%

Using Summations Instead of Loops

∑ j

Types of Flags

Using Flags

Setting, Clearing, and Testing Flags

To set, clear, or test a flag

Month/day/year format

Recalling and Storing the Flag States

Example

Day.month.year format

Execute Rclf !L %MODES% %FLAG% L%RCLF%

Using Subroutines

To recall the current flag states

To change the current flag states

Torsv K

Torsa K

` 8 J %TORSV%

Press !LL %RUN% %KILL%

To singlestep from the start of a program

To turn off the Halt annunciator at any time

@·J6 `8 `O%TORSV% !LL%RUN% %DBUG%

To singlestep from the middle of a program

To singlestep when the next step is a subroutine

@·J10 `12 O%TORSV% !LL%RUN% %DBUG%

To cause a userdefined error to occur in a program

Trapping Errors

Causing and Analyzing Errors

SingleStep Operations

Error Trapping Commands

To artificially cause a builtin error to occur in a program

To analyze an error in a program

%ERROR%

Press !LL %ERROR% !%IFERR%

Making an Error Trap

« … Iferr trapclause then errorclause END … »

Iferr then END Structure

Iferr then Else END Structure

Press !LL %ERROR% @%IFERR%

To enter Iferr then Else END in a program

Key Command Description

Data Input Commands

Using PROMPT, Cont for Input

Input

`OTPROMPT ‰

@·J %TPROM%

To enter Disp Freeze Halt in a program

Using Disp Freeze HALT, Cont for Input

To respond to Halt while running a program

To enter Input in a program

Using INPUT, Enter for Input

« … promptstring commandline Input OBJ→ … »

To respond to Input while running a program

%VSPH%

To include Input options

Commandline cursorposition operatingoptions

To design the commandline string for Input

Cursorposition

Press @ Õ ! Ê a @

To process the result string from Input

`O Tinput ‰

%TINPU%

Using Inform and Choose for Input

To set up an input form

To set up a choose box

`OPHONES ‰

To enter Beep in a program

Using Wait for Keystroke Input

Beeping to Get Attention

To enter Wait in a program

Output

Using KEY for Keystroke Input

Data Output Commands

OUT%

To label a result with a tag

Labeling Output with Tags

Labeling and Displaying Output as Strings

%TTAG% 1.5 ˜1.85 `

To set up a message box

Pausing to Display Output

Using Msgbox to Display Output

`OTSTRING ‰

Using Menus with Programs

Using Menus for Input

Olst ‰

Using Menus to Run Programs

To create a menubased application

SI%

@·J%EIZ%

@%%I%% 2*%%I%% !%%E%%

Turning Off the Calculator from a Program

%% !Ü.37~@6 68 %%I%% !%%Z%%

To turn off the calculator in a program

Page

FIB1 Fibonacci Numbers, Recursive Version

Fibonacci Numbers

RPL Programming Examples

%FIB1%

FIB2 Fibonacci Numbers, Loop Version

FIB1% !Ü10 N

%FIB2%

FIB2 program listing

10 %FIB2%

Structured programming. Fibt calls both FIB1 and FIB2

Fibt Comparing ProgramExecution Time

Techniques used in Fibt

Required Programs

13 %FIBT%

Displaying a Binary Integer

PAD Pad with Leading Spaces

Techniques used in PAD

`OPAD K

Preserve Save and Restore Previous Status

PAD program listing

Techniques used in Preserve

Preserve program listing

Bdisp Binary Display

`OPRESERVE K

Techniques used in Bdisp

PAD

Bdisp program listing

`OBDISP K

Tile Percentile of a list

Median of Statistics Data

144 %BDISP%

Tile program listing

Median Median of Statistics Data

Techniques used in %TILE

`O%TILE K

Techniques used in Median

Required Program

18 `12 `˜šš

Expanding and Collecting Completely

`OMEDIAN K

11 `1 `

Multi program listing

Multi Multiple Execution

Techniques used in Multi

`OMULTI K

Exco program listing

Exco Expand and Collect Completely

Techniques used in Exco

`OEXCO K

Ü4 *Y+Z +

Minimum and Maximum Array Elements

MNX Minimum or Maximum Element-Version

User and system flags for logic control

MNX program listing

`OMNX K

12 `56 `˜šš 45 `1 `

MNX2 Minimum or Maximum Element-Version

Techniques used in MNX2

MNX2 program listing

Techniques used in Aply

Applying a Program to an Array

%MNX2%

Aply program listing

Make sure the flag 1 is clear to begin

Ô3†2W†4` ‚Å 3 QA *7 `J %APLY% H#DISP ˜˜

Converting Between Number Bases

`OAPLY K

Techniques used in nBASE

NBASE program listing

Verifying Program Arguments

1000 `23 J %NBASE%

Names program listing

Names Check List for Exactly Two Names

Techniques used in Names

`ONAMES K

Techniques used in VFY

VFY Verify Program Argument

VFY program listing

Ojeff ` Osarah `

Converting Procedures from Algebraic to RPN

Oben `

%LIST% %²LIST%

Techniques used in →RPN

→RPN program listing

XQ3 `%²RPN%

Bessel Functions

Techniques used in BER

%BER%

BER program listing

`OBER K

%BER% !Ü2

Techniques used in Sintp

Animation of Successive Taylor’s Polynomials

Sintp Converting a Plot to a Graphics Object

Sintp program listing

Setts program listing

Setts Superimposing Taylor’s polynomials

Techniques used in Setts

`OSETTS K

TSA program listing

TSA Animating Taylor’s Polynomials

Techniques used in TSA

`OTSA K

Techniques used in PIE

Programmatic use of matrices and statistics commands

Programmatic Use of Statistics and Plotting

Temporary menu for data input

Angle

`OPIE K

983 %SLICE% 416 %SLICE% 85 %SLICE%

ΑENTER program listing

Trace Mode

Techniques used in αENTER and ßENTER

ßENTER program listing

Rootr program listing

InverseFunction Solver

Techniques used in Rootr

`OROOTR K

%X²FX% ` 599.5 ` 1 %ROOTR%

Animating a Graphical Image

@Å@É x †O3.7

Techniques used in Walk

`OWALK K

Type

Introduction

Acos

Input/Output

Other Provided Details

How Commands Are Alphabetized

Parallel Processing with Lists

Computer Algebra System Commands and Functions

Classification of Operations

Library identifier

Backup identifier

Realnumber time or angle in hoursminutessecond s format

Binary integer

ABS

Abcuv

ACK

Ackall

Type Description

ACOS2S

ASIN, ATAN, COS, Isol

Acosh z

Acosh

ASIN2C, ASIN2T, ATAN2S

Symb ACOSHsymb

ADD

Addtmod

Alog

Addtoreal

Algb

10z

Principal Interest Balance

Amort

TVM, TVMBEG, TVMEND, Tvmroot

Animate

ANS

Apply

Access …µAPPLY Input/Output

ARC

Archive

ARG

ARRY→

Access …µARRY→ Input/Output

Arit

→ARRY

Access !¼ ¼is the leftshift of the Skey

ASIN2T

ASIN2C

Asinh

Symb ASINHsymb

ASN

Asinh z

ACOSH, ATANH, ISOL, Sinh

Assume

Access … ÃL BIT ASR

ASR

Skey

Atan

ADDTOREAL, Unassume

Symb ATANsymb

ATAN2S

Atan z

ACOS, ASIN, ISOL, TAN

Atick

Access …µATICK

Atanh

Atanh z

Augment

Access …µATTACH Input/Output

Attach

#n #m

Axes

Access …µAUTO Input/Output None

Auto

BAR

AXM

Access …µAXES Input/Output

AXL

Atick xaxis label yaxis label

AXL, AXQ

AXQ

BAR

AXL, AXM, GAUSS, QXA

Basis

Access …µBAR Input/Output None

Barplot

Baud

Beep

Access …µBESTFIT Input/Output None

Access … Ã BIN

Bestfit

Blank

Access !L Pict BOX Is the leftshift of the Nkey

Bins

BOX

Bytes

Access …µBUFLEN Input/Output

Buflen

#n1 #m1 #n2 #m2 X1, y1 X2, y2

C2P

Access … Ã B → R

Cascfg

Case

Cascmd

Help

Xunit Nunit Symb CEILsymb

Ceil

Centr

FLOOR, IP, RND, Trnc

Chinrem

Cholesky

Choose

Command Result

CHR

NUM, POS

Circ

Cksm

REPL, SIZE, SUB

Cllcd

Clear

Clkadj

Closeio

Clvar

CLΣ

Clusr

Cmplx

COL→

→COL

COL

Collect

COL+

Colct

Symb1 Symb2

CON

Colσ

Comb

Symb COMBsymb ,m COMBn, symb COMBsymb ,symb

Carray constant Name

Cond

Rarray constant

IDN

Conic

Access …µCONIC Input/Output None

Conj

Constants

Conlib

Const

Rarray Carray Symb CONJsymb

Corr

Cont

Convert

X1unitssource X2unitstarget X3unitstarget

Cosh

Access Flags

COS

COV

Cswp

Crdir

Cross

…µCR

Cylin

Curl

Cyclotomic

COL+, COL-, Rswp

Date

→PX

Darcy

#n, #m

Dbug

→DATE

DATE+

→date

Decr

Ddays

DEC

« program » or program name

Define

Dedicace

DEF

Result See also

Degree

Delalarm

DEG

Name=exp Namename Name =expname

Delkeys

Delay

RCLALARM, Stoalarm

CR, OLDPRT, PRLCD, PRST, PRSTC, PRVAR, PR1

Depth

Access …µDEPND Input/Output

Depnd

Xkey1, ... ,xkey n

Dervx

Deriv

Desolve

Detach

Access …µDETACH Input/Output

DET

Attach

→DIAG

DIAG→

Diagmap

Diff

Diffeq

DIR

Access …µDIFFEQ Input/Output

Disp

Obj List

Dispxy

Distrib

FREEZE, HALT, INPUT, Prompt

DIV2MOD

DIV

DIV2

CURL, Hess

Divpc

Divis

Divmod

DIV2

Until testclause END

TAYLOR0, TAYLR, Series

DERIV, DERVX, DESOLVE, ∂

END

Doerr

Error

Dolist

Dosubs

List List n « program » Results Command Name List n+1

Domain

SIGNTAB, Tabvar

DOLIST, ENDSUB, NSUB, Stream

List « program » Command Name

DOT

CNRM, CROSS, DET, Rnrm

Draw

Access …µDRAW

Access …µDRAX Input/Output None

DRAW3DMATRIX

DROP2

Droite

Drop

Lagrange

DUP

Dropn

Dtag

DUP2

Dupdup

Dupn

Editb

Edit

Egcd

Else

EGV

Egvl

END

EPSX0

Endsub

ENG

Sign mantissa E sign exponent

EQ→

Eqnlib

EQW

Erase

Errn

ERR0

Errm

Euler

Obj See above

Eval

Exlr

→NUM

EXP

EXP&LN

Ex,y = excosy + iexsiny

EXP2POW

EXP2HYP

Expan

COLCT, EXPAND, ISOL, QUAD, Show

Expand

Expandmod

Result X2+X

Expm

Expfit

Expln

Eyept

Factor

F0λ

Fact

…µF0λ

Factors

Factormod

Modsto

Fanning

Access …µFANNING

FAST3D

Fcoef

Access …µFAST3D Input/Output None

Access ! Test LL FC ? C

FC?

CF, FC?, FS? FS?C, SF

Fdistrib

FFT

Distrib

Filer

Findalarm

Access …µFINISH

Finish

FONT6

Flasheval

Floor

Xunit Nunit Symb FLOORsymb

FONT→

FONT7

FONT8

→FONT

For

Freeze

Fourier

Free

Xunit Yunit Symb FPsymb

Display Area Value Code

Froots

FS?

CLLCD, DISP, Halt

Function

FS?C

CF, FC?, FC?C, FS?C, SF

Fxnd

Access …µFUNCTION

Exlr

Gbasis

Gamma

Gauss

AXQ, QXA

GET

GCD

Gcdmod

GCDMOD, EGCD, IEGCD, LCM

Objget

Geti

GETI, PUT, Puti

GET, PUT, Puti

GOR

Grad

#n #m Grob1

Greduce

Gramschmidt

Graph

DEG, RAD

Gridmap

Access …µGRIDMAP Input/Output None

Access …µ→GROB

→GROB

Gxor

Grob

Grobadd

→LCD, LCD→

Halt

Hadamard

Halftan

GOR, REPL, SUB

→HEADER

Head

HEADER→

Help

HEX

Hermite

Hess

CURL, DIV

Hilbert

Histogram

HMS

Access …µHISTPLOT Input/Output None

Histplot

HMS+

… & 9L HMS +

HMS→

→HMS

… &9L HMS →

Horner

Home

Iabcuv

IBP

Ibasis

Ibernoulli

ABCUV, Iegcd

Results See also

Ichinrem

IDN

Chinrem

DIV2, Iquot

IDIV2

Iegcd

Ax+by=c

Case

Iferr

ELSE, END, IFERR, then

∑ Y k e

Ifft

Ilap

IFT

Ifte

Obj It depends

…ßIM

Image

LAP, Lapl

Rarray Carray Symb IMsymb

Inform

Incr

Indep

Global Global xstart xend

Input

Resets

Title Format Resets Init → vals

Init

INT

Stack prompt Commandline prompt Result

PROMPT, STR→

INV

Integer

Intvx

INTVX, Risch

Invmod

Command INVMOD2 Result

Iquot

Isom

Iremainder

Isol

Symb1 Global Symb2

Mkisom

ISPRIME?

Jordan

NEXTPRIME, Prevprime

KEY

KER

Kerrm

BASIS, Image

Keyeval

Access …µKEYEVAL Input/Output

→KEYTIME

Kill

KEYTIME→

Kget

Label

LANGUAGE→

Access …µ→LANGUAGE Input/Output

Lagrange

→LANGUAGE

Last

LAP

Lapl

Objn Obj1

→LCD

Lastarg

LCD→

LCM

Lcxm

Ldec

Libs

Lgcd

Libeval

HERMITE, Tchebycheff

LIN

Lim

Limit

Title, nlib, nport, ...,title, nlib, nport

Linfit

Line

Σline

Model Form of Expression

LIST→

Linin

Linsolve

→LIST

Πlist

List

Σlist

Access …¹ ¹is the rightshift of the Qkey

Lncollect

Lname

LNP1

Ln x +

Local

LOG

Symb LNP1symb

Access !Ø Input/Output

Logfit

LSQ

Access …µLR Input/Output

Full Command and Function Reference 3139

Intercept x Slope x

DET, INV

Lvar

MAD

Lname

Mant

Access …µMAP Input/Output

Main

MAP

↑MATCH

Access …µ↓MATCH Input/Output

Access …µ↑MATCH

Symb Symb symb

MAX

Maths

Matr

Symb Symb , symb

Mcalc

Maxr

Maxσ

Input/Output See also

Menu

Mean

MEM

BINS, MAXΣ, MINΣ, SDEV, TOT, VAR

Menuxy

RCLMENU, Tmenu

Minehunt

Merge

MIN

MENU, Tmenu

Minit

MINIFONT→

→MINIFONT

Minr

Mkisom

Minσ

Mitm

00000000000E-499

Modular

MOD

Modsto

Mod y

Msgbox

Molwt

Mroot

Name Or xunit String

Mslv

Msolvr

→NDISP

Multmod

Muser

EQNLIB, MCALC, MINIT, MITM, MROOT, MSLV, Muser

Ndupn

Access …ß NEG ßis the rightshift of the 1key

Ndist

NEG

Next

Newob

Nextprime

Not

Access ! Test L not Is the leftshift of the Nkey

NIP

Noval

NUM

Nsub

→NUM

…µNΣ

Numy

Numx

OBJ→

Oldprt

OCT

OFF

… &NL OBJ →

Access …µOPENIO

Access …µOLDPRT

Openio

Memory Directory Lorder is the leftshift of the Nkey

Order

Over

Global1 ... globaln

Parametric

P2C

PA2B2

Xmin, ymin, xmax, ymax, indep, res, axes, ptype, depend

Access …µPARITY Input/Output

Parity

Parsurface

Partfrac

Pcoef

Path

Pcar

Home directoryname 1 ... directoryname n

Pcontour

Access …µPCONTOUR Input/Output None

Pcov

Perm

Pdim

Perinfo

Xmax, ymax

Pgdir

Pertbl

Peval

Pick

Picture

Pict Command Puts the name Pict on the stack

Pict

Pinit

Pixoff

Access …µPKT

PIX?

Pixon

Pmax

Plot

Plotadd

Pmin

Finds the minimal polynomial of a matrix

Pmini

Polar

An nxn matrix a

POP

Access …µPOLAR

Polynomial

Form of Current Plotting Action Equation

Potential

Input An expression raised to a power

POS

Powexpand

Powmod

PR1

…µPR1

Predv

Predx

Object

Predy

Preval

Prompt

Prevprime

Prlcd

Promptsto

Global→

Proot

Propfrac

Prompt STO

Prvar

Prst

Prstc

Name Name1 name2 Nport global

Psi

Psdev

PSI

MEAN, PCOV, PVAR, SDEV, TOT, VAR

Purge

Ptayl

Ptprop

Symb String or x or xunit or name

Global Global1 ... globaln

Push

PUT

CLEAR, CLVAR, NEWOB, Pgdir

Obj put List

This command sequence

Puti

Obj put List Name

Pvars

Pvar

MEAN, PCOV, PSDEV, SDEV, VAR

Pview

Access …µPVARS Input/Output

Nport namebackup Memory

Pwrfit

→Qπ

PX→C

+ c/d*i

+ c/ d

Quad

̟ + c/ d* ̟

LQ, LSQ

Arithmetic, !ÞPOLYNOMIAL !«

Quot

Quote

Quotient of the Euclidean division

Rand

QXA

RAD

Rank

Ratio

Access …µRATIO

Ranm

LQ, LSQ, QR

Rcij

Rceq

RCI

Steq

Rclalarm

RCL

Rclkeys

FINDALARM, Stoalarm

Rclf

Rclmenu

Rcws

Rclvx

Rclσ

RDM

COMB, PERM, Rand

RDZ

…ßL RE

Recv

Recn

Rect

REsymb

Quot

Remainder

Rename

New name Old name

Repl

Reorder

Repeat

END, While

String target

Plot Type Default Interval

RES

String String result

Resultant

Restore

Backup To restore a

Slopefield

Rewrite

Revlist

Risch

RKF

Rkferr

Rkfstep

Problem for a differential equation

Is the rightshift 3key

RLB, RR, RRB

RLB

RND

RNDsymb

Rolld

Rnrm

Roll

Romupload

ROW

Root

ROT

3207

ROW→

ROW+

→ROW

RRB

Access … ÃL Byte RRB Is the rightshift of the 3key

RPL

RL, RLB, RRB

Rref

Rref

Rrefmod

RRK

− 2 t + t 2

Rrkstep

RSD

Rsberr

RKF, RKFERR, RKFSTEP, RRK, Rsberr

Rules

Access … Ã R → B

Rswp

DET, IDN

180/̟x

Same

→R, IM, RE

→Dsymb

Scale

Access …µSCALEH Input/Output

Sbrk

Scaleh

Scatter

Scatrplot

AUTO, SCALEH, Xrng

SCI

Access …µSCATTER Input/Output None

Schur

Sclσ

Sdev

Sconj

Scroll

Send

Series

SEQ

DOSUBS, Stream

Server

Seval

Sigma

Show

Sidens

X1/cm3

Sigmavx

Access !ÖDERIV L

Access !ÖDERIV LL

Sign

SIGNsymb

Signtab

SIMP2

ABS, MANT, Xpon

Sincos

Simplify

SIN

Sin z

Size

Sinh

Sinv

Sinh z

String Integer List Vector

SLB

Slopefield

Symb Grob

Snrm

Sneg

NEG, SCONJ, Sinv

Solve

Solveqn

Solvevx

Solver

Sort

Square Analytic Function Returns the square of the argument

Sphere

Srad

SQsymb

COND, SNRM, Trace

SRB

Srecv

ASR, SL, SLB, SR

SST

Access …µSRECV

Srepl

SST↓

STD

Start

Step

Steq

Access …µSTIME

Step

Stime

STO

Stoalarm

Access Input/Output

Buflen

Stokeys

Access …µSTOF

Stof

Óis the rightshift of the 9 key

Stovx

Store

STO+

STO/, +

→STR

Stoσ

STR→

DTAG, EQ→, LIST→, OBJ→, →STR

Sturm

Stream

Strm

List Obj Result

SUB

Sturmab

Stws

Sturmab

X1, y1 X2, y2

Subst

Subtmod

CHR, GOR, GXOR, NUM, POS, REPL, Size

Swap

SVD

SVL

DIAG→, MIN, SVL

Sylvester

Syseval

SYST2MAT

X, symb

Tabval

100 y

Symb 1, symb

Tail

Tabvar

→TAG

→ARRY

TAN2SC

TAN

TAN2CS2

Tan z

Tanh z

TAN2SC2

Tanh

TANHsymb

Tchebycheff

TAYLOR0

Taylr

HERMITE, Legendre

Tests

Tcollect

Tdelta

TDELTAsymb1, symb2

Text

Teval

Texpand

Then

→TIME

Ticks

Time

Tinc

TINCsymb1, symb2

Tlin

Tline

SIMPLIFY, TCOLLECT, Texpand

Trace

Tmenu

TOT

Tran

Effect

Transio

Trig

BAUD, CKSM, Parity

Trigsin

Trigcos

Trigo

Trigtan

Trnc

TRN

CONJ, Tran

TRNCz

Trunc

Truth

TRNCsymb

Tsimp

Access …µTRUTH Input/Output None

Tstr

Tvmbeg

Tvars

TVM

Tvmend

Ubase

Builtin Commands

Type

Object Type Number User objects

Unassign

Ufact

UFL1→MINIF

Unassume

→UNIT

Unbind

Unpick

Updir

Unrot

Until

Utpc

UTPF, UTPN, Utpt

Utpf

Utpn

UTPC, UTPN, Utpt

Uval

Utpt

UVALsymb

X1, x2

Flag -16 clear Rectangular mode Flag -16 set Polar mode € y

Coordinate System -16, Complex Mode

X1, x2, ..., xn Xn-2

Vandermonde

VAR

VER

Access …µVERSION Input/Output

Vars

Version

Visit

Variable name Contents opened in the command line Editor

Variable name Contents opened in the most suitable Editor

Visitb

Vtype

Access ! L in Wait Is the leftshift of the Nkey

Wait

While testclause Repeat loopclause END

Wireframe

While

While Repeat

Wslog

ΣX2

Access …µWSLOG

Access …µΣX Input/Output

Log4 ... log1

Xget

ΣX2

Xcol

Xmit

Xnum

Access …µXMIT

XOR

XPONsymb

Xpon

Xput

MANT, Sign

Xrecv

Command XQ.3658 Results 1829/5000

Command XQ.3658 Results √19/142

Xrng

Xserv

Access …µXSEND

Xsend

Input/Output RPN

ΣXY

Xvol

Xxrng

ΣX*Y

Ycol

ΣY2

ΣY2

…µΣY

Yslice

Yrng

AUTO, PDIM, PMAX, PMIN, Xrng

Zeros

Yvol

Yyrng

EYEPT, XVOL, XXRNG, YYRNG, Zvol

Zfactor

Power

Access Q

Zvol

Zsymb

Where

√ Square Root

Symbz

SQ, , Isol

? Undefined

Access …Á Áis the rightshift of the Ukey

Integrate

Lower limit, upper limit, integrand, name

Sigma Plus

∞ Infinity

Summation

Results -π/2

Sigma Minus

Access …µΣ+ Input/Output

Access …µΣ Input/Output

X 2, …, x m 1, …, x 1 m x n 1, … , x n m

14159265359…

∂ Derivative

Factorial

Symb Name Xunit

Xy/100

Percent

Unit attachment

Symb,x

Less than

« » Program delimiters

Type Object Description

≤ Less than or Equal

#n1 #n2

Greater than

≥ Greater than or Equal

≠ Not equal

Multiply

≠ symb

+ Add

Subtract

Divide

= Equal

Y1/unit

== Logical Equality

DEFINE, RCL, →, STO

Store

→ Create Local

… É

Semicolon

CLEAR, DROP, DROPN, DROP2

Points to note when choosing settings

CAS Settings

Selecting CAS Settings

CAS directory, Casdir

Computer Algebra System

Compatibility with Other Calculators

Using the CAS

Examples and Help

Extending the CAS

Algebra commands, …×

Computer algebra command categories listed by menu

Arithmetic commands

Arithmetic Integer commands, !ÞINTEGER

Arithmetic Permutation commands, !Þ Permutation

Arithmetic Modulo commands, !Þ Modulo

Other Arithmetic commands, !Þ

Calculus commands

Create, !Ø Create

Exp and Lin commands, !Ð

Matrixrelated commands

Operations, !Ø Operations

Linear Applications, !Ø Linear Appl

Quadratic form, !Ø Quadratic Form

Linear Systems, !Ø Linear Systems

Eigenvectors, !Ø Eigenvectors

Other Trigonometry commands, …Ñ

Symbolic solve commands, !Î

Trigonometry commands

Hyperbolic, …Ñ Hyperbolic

Base conversion tools, !Ú Base

Convert commands, !Ú

Unit conversion tools, !Ú Units Tools

Trigonometric conversions, !Ú Trig Conv

Other CAS operations, …µ

Matrix convert, !Ú Matrix Convert

These commands display menus or lists of CAS operations

CAS menu commands, …µ

CAS utility operations

Equation Reference

Equation Reference

FLUIDS, 24 *********************3

Σcr Critical stress Σmax Maximum stress

Columns and Beams

Variable Description

Internal bending moment at

Equations

Elastic Buckling 1

Eccentric Columns 1

Example

Simple Slope 1

Simple Deflection 1

Equation

Simple Moment 1

Solution V=624.387lbf

Simple Shear 1

Cantilever Slope 1

Cantilever Deflection 1

Cantilever Moment 1

Solution V=200lbf Equation Reference

Cantilever Shear 1

Relative permittivity

Electricity

Relative permeability

Ohm’s Law and Power 2

Coulomb’s Law 2

Solution I1=5.6250A

Wire Resistance 2

Solution V1=80V

Voltage Divider 2

Series and Parallel R 2

Solution R=0.175

Series and Parallel C 2

Capacitive Energy 2

Solution V=50V

Series and Parallel L 2

Inductive Energy 2

DC Capacitor Current 2

RLC Current Delay 2

Solution q=0.0020C Equation Reference

Capacitor Charge 2

RC Transient 2

Solution V=3.2968V

DC Inductor Voltage 2

RL Transient 2

Plate Capacitor 2

Solution I=0.0072A

Resonant Frequency 2

Cylindrical Capacitor 2,19

Solenoid Inductance 2

Toroid Inductance 2

Sinusoidal Voltage 2

Fluids

Sinusoidal Current 2

Reynolds number

Pressure at Depth 3

Bernoulli Equation 3

Initial and final velocities

Flow with Losses 3

Forces and Energy

Flow in Full Pipes 3

Linear Mechanics 4

Centripetal Force 4

Angular Mechanics 4

Hooke’s Law 4

Law of Gravitation 4

1D Elastic Collisions 4

Drag Force 4

MassEnergy Relation 4

Gases

Ideal Gas Law 5

Isothermal Expansion 5

Solution Vf=21

Ideal Gas State Change 5

Polytropic Processes 5

Real Gas Law 5

Real Gas State Change 5

Heat Transfer

Kinetic Theory 5

Thermal Expansion 6

Heat Capacity 6

Conduction 6

Convection 6

Conduction + Convection 6

Fba

Magnetism

Black Body Radiation 6

Ia, Ib

Straight Wire 7

Force between Wires 7

Magnetic B Field in Solenoid 7

Solution B=0.0785T

Magnetic B Field in Toroid 7

Motion

Object in Free Fall 8

Linear Motion 8

Projectile Motion 8

Terminal Velocity 8

Angular Motion 8

Circular Motion 8

Escape Velocity 8

Optics

Law of Refraction 9

Critical Angle 9

Brewster’s Law 9

Spherical Refraction 9

Solution n2=1.5000

Spherical Reflection 9

Thin Lens 9

Oscillations

Simple Pendulum 10

MassSpring System 10

Example Given L=15cm

Torsional Pendulum 10

Conical Pendulum 10

Simple Harmonic 10

Plane Geometry

Ellipse 11

Circle 11

Equations Example

Rectangle 11

Regular Polygon 11

Circular Ring 11

Triangle 11

Solid Geometry

Cone 12

Cylinder 12

Parallelepiped 12

Sphere 12

Solid State Devices

Drawn gate length Nmos Transistors, or

Saturation current density

Drawn mask length PN Step Junctions, or

Channel length JFETs

PN Step Junctions 13

Nmos Transistors 13

VDS

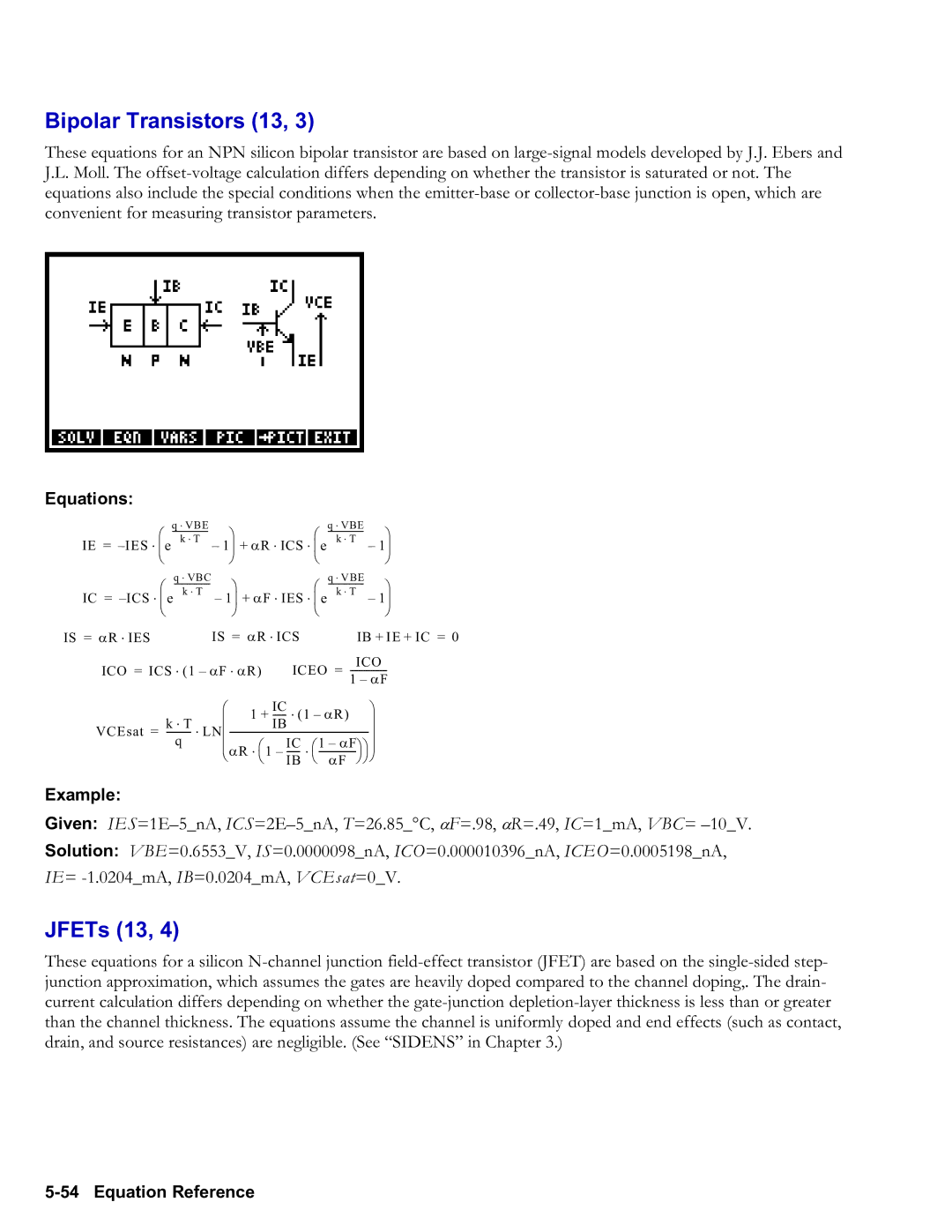

Bipolar Transistors 13

JFETs 13

Xdmax = ⋅ Vbi VGS + VDS

Maximum principal normal stress

Stress Analysis

Minimum principal normal stress

Shear Stress 14

Normal Stress 14

Stress on an Element 14

Mohr’s Circle 14

Example

Transverse Waves 15,1

Waves

Longitudinal Waves 15

Sound Waves 15

References

Page

Development Library

Obj1 … objn Symb Obj1, ...,objn

Development Library Command Reference

Obj String

Development Library

String Obj

BetaTesting

String Obj Debug string Error list

Code String

Library Object String

String Error list Edited string

Library n

LC~C

Ey,z.Et

→LST

Obj … obj Obj 1, ...,obj n

Pokearm

Obj 1 … obj n Obj 1, ...,obj n

Returns

→S2

String1 String2

String Global

Crlib Create Library Command

Xlib

Extension program

Starting Masd

Masd The Machine Language and System RPL Compiler

Introduction

Modes

Format of the error list

Errors

Error messages Message Description

Links

Labels

Extable

Constants

Expressions

Operator Priority

Macros and includes

Compilation directive

Filename conventions

Directive Description

!DBGINF directive

Docstr

CPU architecture

Saturn ASM mode

Bit registers

New instructions

Other notes

Skips

Skips instructions Equivalents

These instructions Are equivalent to

Tests

Saturn instructions syntax

Syntax Example

Syntax Example

DReg=hh

See above. This is only valid in emulated Saturn

Places the value of Exp in the code, on x nibbles

CARRY0

003AA Autousertest

ARM mode

ARM architecture

Instruction set

Description Form

Operation Assembler Action Flags

REG a

Armsat instruction

Offset Element

REG B

REG C REG D REG R0 REG R1 REG R2 REG R3 REG R4

Reals and system binary

System RPL mode

Instructions

Unnamed local variables

Tokens

Defines

Token Description

Code

LC 001 Gosbvl Outcinrtn ?CBIT=1.6

Turnmenuoff

LC 80100 Armsat

Disassemblers

Level

Nop

Entry Point Library Extable

Library

String String 1, ...,string n

Message Meaning # hex

Error and Status Messages A1

Messages Listed Alphabetically

C0C

A2 Error and Status Messages

Error and Status Messages A3

A4 Error and Status Messages

Σdat

Error and Status Messages A5

A6 Error and Status Messages

C0B

Error and Status Messages A7

C0E

C0D

A8 Error and Status Messages

Error and Status Messages A9

# hex Message General Messages

A10 Error and Status Messages

# hex Message

Error and Status Messages A11

OutofMemory Prompts

Object Editing Messages

Stack Errors and Messages

A12 Error and Status Messages

Equation Writer Application Messages

Array Messages

# hex Message FloatingPoint Errors

Error and Status Messages A13

Statistics Messages

Mode and Plot Input Form Prompts

A14 Error and Status Messages

Error and Status Messages A15

# hex Message 70F

A16 Error and Status Messages

73F

Error and Status Messages A17

75F

A18 Error and Status Messages

78F

Error and Status Messages A19

A20 Error and Status Messages

Advanced Statistics Messages

Error and Status Messages A21

80F

A22 Error and Status Messages

82F

Error and Status Messages A23

85F

A24 Error and Status Messages

87F

Statistics Help Messages

Error and Status Messages A25

HP Solve Application Messages

Time Messages

# hex Message Unit Management

Printing

Programmer’s Doerr

Error and Status Messages A27

A28 Error and Status Messages

System Flags Choose Box Prompts

Error and Status Messages A29

A30 Error and Status Messages

Error and Status Messages A31

A32 Error and Status Messages

Prompts

Error and Status Messages A33

A34 Error and Status Messages

Error and Status Messages A35

Statistics Prompts

Time and Alarm Prompts

A36 Error and Status Messages

Error and Status Messages A37

Symbolic Application Prompts

A38 Error and Status Messages

Error and Status Messages A39

Plot Application Prompts

A40 Error and Status Messages

Error and Status Messages A41

A42 Error and Status Messages

Solve Application Prompts

Error and Status Messages A43

A44 Error and Status Messages

Error and Status Messages A45

CAS Messages

A46 Error and Status Messages

Error and Status Messages A47

DF0A DF0B DF0C DF0D DF0E DF0F

A48 Error and Status Messages

Filer Application Messages

DF1A DF1B DF1C DF1D DF1E DF1F

Error and Status Messages A49

Constants Library Messages

Minehunt Game Prompts

A50 Error and Status Messages

Equation Library Messages

MultipleEquation Solver Messages

Financial Solver Messages

Error and Status Messages A51

Periodic Table Messages

Development Library and Miscellaneous Messages

A52 Error and Status Messages

Units

Tables of Units and Constants B1

B2 Tables of Units and Constants

Tables of Units and Constants B3

B4 Tables of Units and Constants

Tables of Units and Constants B5

Constant Full Name Value in SI Units

Properties of Elements

B6 Tables of Units and Constants

Not used

System Flags

Flag Description

System Flags C1

C2 System Flags

System Flags C3

C4 System Flags

System Flags C5

C6 System Flags

System Flags C7

Internal use only /0 occurred

C8 System Flags

User Flags

System Flags C9

Page

Reserved Variables D1

Contents of the System Reserved Variables

ΒENTER

Reserved Variables D3

Exited

D4 Reserved Variables

Reserved Variables D5

N1, n2

MHpar

Mpar

Nmines

BAR, etc

Reserved Variables D7

Prtpar

D8 Reserved Variables

S1, s2

Reserved Variables D9

NUMX, Numy

Parameter Description Default Value Command

To use for input into the table

D10 Reserved Variables

Statistical Matrix for Variables 1 to m

Var1 var2 … varm

Reserved Variables D11

EXPFIT, PWRFIT, or Logfit

D12 Reserved Variables

Casdir Reserved Variables

Modulo

D14 Reserved Variables

Object Type Size bytes

Object Size

Technical Reference E1

Pattern Antiderivative

Symbolic Integration

E2 Technical Reference

Technical Reference E3

→DEF Expansions

E4 Technical Reference

Order Operation

Technical Reference E5

International Standard publication No. ISO 31/l197 8 E

E6 Technical Reference

General rules for parallel processing

Group 1 Commands that cannot parallel process

Group 2 Commands that must use Dolist to parallel process

Parallel Processing with Lists F1

Group 4 ADD and +

Group 5 Commands that set modes / states

Group 6 Oneargument, oneresult commands

F2 Parallel Processing with Lists

Group 9 Multipleresult commands

Group 7 Two argument, one result commands

Group 8 Multipleargument, oneresult commands

Group 10 Quirky commands

Using Dolist for Parallel Processing

F4 Parallel Processing with Lists

$ & F

$ & C

$ & D

$ & +

@ & ³ @ & O

Keycode Keystroke Definition

¥ ! &I

~@ & O

@%VARNAME% = varname

~@ & Í @ &†

Keyboard Shortcuts G3

G4 Keyboard Shortcuts

Syntax Example

Menu Numbers

MenuNumber Table H1

Menus 0 through

H2 The MenuNumber Table

MenuNumber Table H3

Menus 118 through

H4 The MenuNumber Table

BuiltIn Library Menus

Menus 178 through

MenuNumber Table H5

Page

Key ALPHARS2 MTH NXT Prob

Command MenuPath Table

+ key

Command Type Library Size Keys Menu First

I2 The Command MenuPath Table

«MODULAR» Addtoreal

MTH List

Arith Modul

CAT Algb

I4 The Command MenuPath Table

PRG NXT

LS&MODE Flag

PRG Test NXT NXT PRG NXT Modes Flag Chinrem

CHR

I6 The Command MenuPath Table

RS&TIME NXT

CAT Delalarm

PRG NXT NXT Time Alrm Delay

PRG NXT NXT Time NXT

I8 The Command MenuPath Table

MTH Matrx NXT

PRG NXT NXT Error Iferr

«POLYNOMIAL» EGV

Else

I10 The Command MenuPath Table

I11

I12 The Command MenuPath Table

PRG Brch NXT

Calc Deriv NXT

«INTEGER»

«DIFF» NXT NXT

I14 The Command MenuPath Table

I15

I16 The Command MenuPath Table

I17

I18 The Command MenuPath Table

I19

I20 The Command MenuPath Table

I21

I22 The Command MenuPath Table

I23

I24 The Command MenuPath Table

I25

I26 The Command MenuPath Table

I27

I28 The Command MenuPath Table

CAT Vtype

Matrices Creat NXT NXT MTH Matrx Make NXT NXT

DUP Menuxy Version

XLIB~

Alphalse

I30 The Command MenuPath Table

SLV NXT

MTH NXT Const «CONSTANTS»

PRG Test «TESTS» NXT

Σline

Σlist

→ALG

I32 The Command MenuPath Table

Character Codes

Code Description

Ascii Character Codes and Translations J1

Code Trans. Description

J2 Ascii Character Codes and Translations

Index

Alpha keyboard

Calculator

59, 531

375 Preserving calculator status

Flags

132

Last argument

Memory

Nested structures

545

Programs

Range 3115

Serial communications

237, D3

Tagged objects

UPs