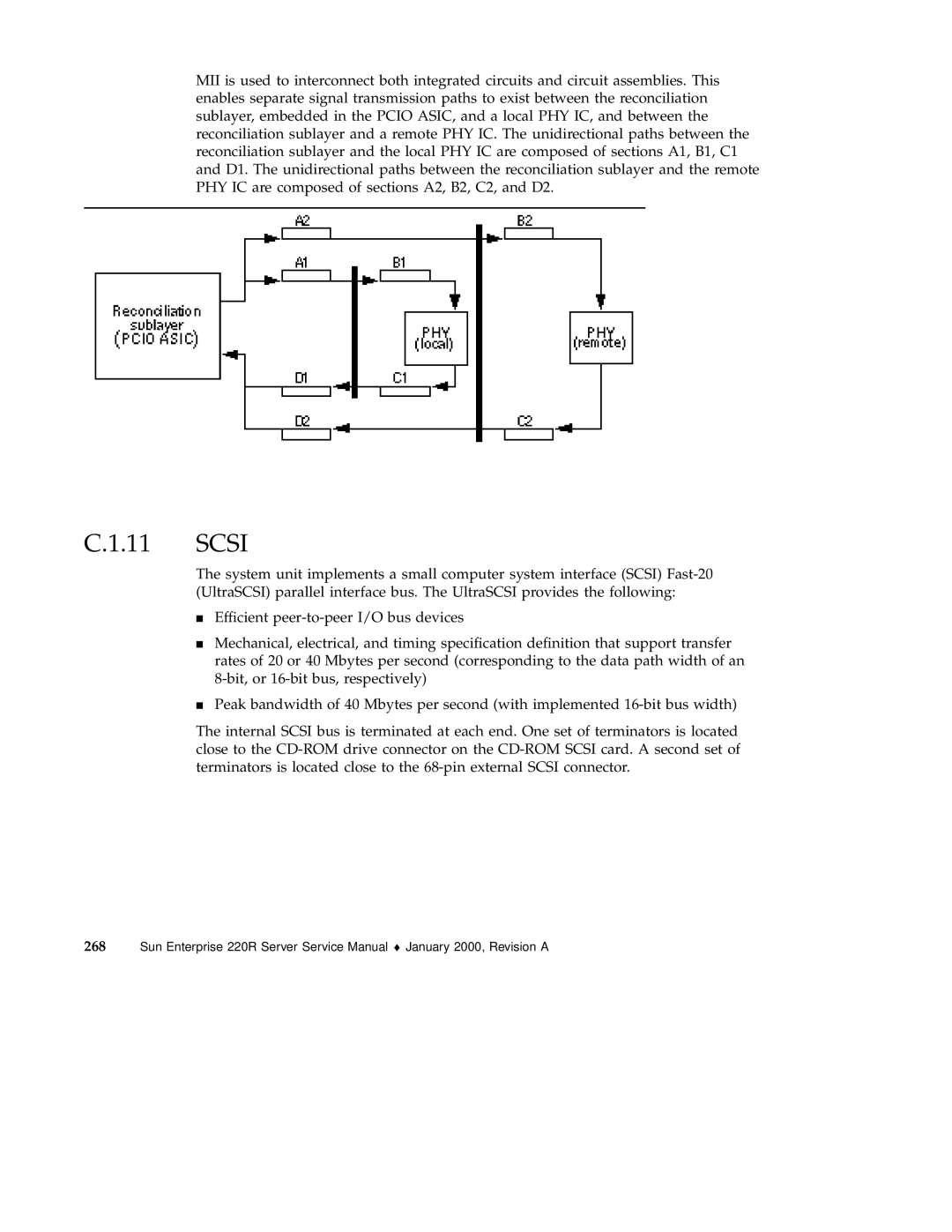

MII is used to interconnect both integrated circuits and circuit assemblies. This enables separate signal transmission paths to exist between the reconciliation sublayer, embedded in the PCIO ASIC, and a local PHY IC, and between the reconciliation sublayer and a remote PHY IC. The unidirectional paths between the reconciliation sublayer and the local PHY IC are composed of sections A1, B1, C1 and D1. The unidirectional paths between the reconciliation sublayer and the remote PHY IC are composed of sections A2, B2, C2, and D2.

C.1.11 SCSI

The system unit implements a small computer system interface (SCSI)

Efficient

Mechanical, electrical, and timing specification definition that support transfer rates of 20 or 40 Mbytes per second (corresponding to the data path width of an

4

Peak bandwidth of 40 Mbytes per second (with implemented

The internal SCSI bus is terminated at each end. One set of terminators is located close to the

268 Sun Enterprise 220R Server Service Manual ♦ January 2000, Revision A