Attached System Bus LAN Subsystem

Network Commprocessor

PIN Quad Flat Pack TOP View

Pinout

Description

Block diagram and signal descriptions

TMS380C26

Terminal Functions

PIN Name Description

AX1 AX0

Maxph

Maxpl

AX3 AX2

Mreset OUT

Sreset

MOE

Mras

NSELOUT0 NSELOUT1

Prtyen

Sbhe

= H

Sddir Direction DIO DMA

Shrq

Sintr

SWR

SRD

= Selects 8-bit mode see Note

108 Reserved. This signal must be left unconnected see Note

= Selects 16-bit mode

Syncin

System Interface ± Motorola Mode SI/M

= L

SBHE/ Srnw

Sbgr

Terminal Functions = L

Sbrq

Sirq

Suds

Sdtack

Slds

Nsrt

FRAQ/TXD

Pxtalin

RCVR/RXD

Lpbk

TXC

Coll

Terminal Functions

VSS1 VSS2

Vssl

VSS3

VSS4 VSS5 VSS6

Architecture

Communications processor CP

System interface SIF

Protocol handler PH

Memory interface MIF

Clock generator CG

Adapter support function ASF

Address Description

Adapter-Internal Pointers for Token-Ring²

Adapter-Internal Pointers for Ethernet ²

³ 68xxx Mode is always 16-bit

User-Access Hardware Registers

Word Transfers

Byte Transfers

Bit 5 Swddir Ð Current Sddir Signal Value

Bits 0-2 Test 0±2. Value on Test 0±2 pins

SIF Adapter Control Register Sifacl

Sifacl Register

Bit 7 Psdmaen Ð Pseudo-System-DMA Enable

Bit 6 Swhrq Ð Current Shrq Signal Value

Bit 8 Areset Ð Adapter Reset

Bit 10 Boot Ð Bootstrap CP Code

Bit 13 PEN Ð Adapter Parity Enable

Bit 12 Sinten Ð System-Interrupt Enable

Bit 14 Ð 15 Nselout 0±1 Ð Network selection outputs

System Psdmaen Swhrq Swhlda Sinten Interrupt Result

Systeminterrupt SINTR/SIRQ

Sifacl Control for Pseudo-DMA Operation

DMA SHRQ/SBRQ

Dmadir Sddir Swhlda Swddir Swhrq Psdmaen Sinten

MIN NOM MAX Unit

Recommended operating conditions

Parameter Test Conditions MIN TYP MAX Unit

See Note

High Low

Test measurement

Vload IOL

Output Under Test

Reference Periods

When

Clkdiv = Oscout MBCLK1² MBCLK2²

Timing parameter symbology

Static signals

Signal Function

Timing parameters

Parameter MIN MAX Unit

289² ThRST Hold time of DMA size from High Intel mode only

Reaches minimum high level

HVDDH-RSL 118² Pulse duration High

Minimun VDD High Level

VDD Sbclk Oscin MBCLK1 MBCLK2 Sreset S8/SHALT

103

101 106 104 105 102 107 110 108 109 111 117 118 119 288 289

Mreset

126 Delay time from MBCLK1 no longer low to Valid

NMI

121 Hold time Valid after MBCLK1 low

Mreset

MBCLK1 MBCLK2 MAX0 MAX2 ADD/EN Mromen Maxph Maxpl

MADH0±MADH7

Memory bus timing clocks, MRAS, MCAS, and MAL to Address

MADL0±MADL7 Maxph Maxpl

Mromen MAL

Address

Column Row

Address Status

Column Status

Mcas MOE

Memory bus timing read cycle

Maxph Maxpl MADH0±MADH7

Maxph Maxpl

Mras Mcas

MAX0 MAX2 Mromen

Address Status Data/Parity

Mbiaen

Memory bus timing write cycle

MAX0, Address

Enable Address

MAX2 Mromen

Mras Mcas Mben

Parameter MIN

Memory bus timing TMS380C26 releases control of bus

MBCLK1 MBCLK2 Mben

75a 74a

Mddir MAL Mbiaen Mbrq Mbgr

Setup time High before MBCLK1 rising edge, bus resume

Memory bus timing TMS380C26 resumes control of bus

Hold time Valid after MBCLK1 low, bus resume

Memory Bus Timing TMS380C26 Resumes Control of Bus

Mben Mddir MAL Mbiaen Mbrq Mbgr

Memory bus timing external bus master read from TMS380C26

Macs

Hold time Low after MBCLK2 low, external bus master read

MBCLK1 MBCLK2

MAX0 MAX2 Maxph Maxpl MADH0±MADH7

Mddir Macs

Memory bus timing external bus master write to TMS380C26

MAX0, MAX2 Maxph Maxpl

Data/Pty

MADL0±MADL7 Mras

Memory bus timing Dram refresh timing

73a

Mcas Mref

Bit

Xmatch and Xfail timing

127 128

Xmatch Xfail

Parameter MIN TYP MAX Unit

Token ring Ð ring interface timing

Rclk

Rcvr

Rclk or Pxtalin

Token ring Ð transmitter timing see Figure

Drvr

160 159

Ethernet timing of Xmit signals

Ethernet timing of clock signals

TXD

Txen

CRS

Ethernet timing of RCV signals Ð start of frame

RXC

RXD

Crshld

Ethernet timing of RCV signals Ð end of frame

320 321

322

Ethernet timing of RCV signals Ð no RXC

Norxc

TXD Txen

TXC TXD

350

Data

JAM

80x8x DIO read timing

SRS0± SRS2 Sbhe

SCS, Srsx

Sras

Sdben

80x8x DIO write timing

267 272a 280 281

Valid 264 265 268 256

281a

282W 283W 276 279 275 282b

80x8x interrupt acknowledge timing ± second Siack pulse

80x8x interrupt acknowledge timing ± first Siack pulse

SRD, SWR SCS Siack

287 First 286 Second

Sddir High

SCS, Srsx SRS0±SRS2 Sbhe Siack SWR SRD

Sdben SRDY²HI-Z

SADH0±SADH7 SADL0±SADL7,HI-ZSPH, SPL

Sown

80x8x mode bus arbitration timing, SIF takes control

SRD SWR

SWR Sown

Sbbsy Shlda

SRD, SWR

SADL0±SADL7 SPH, SPL

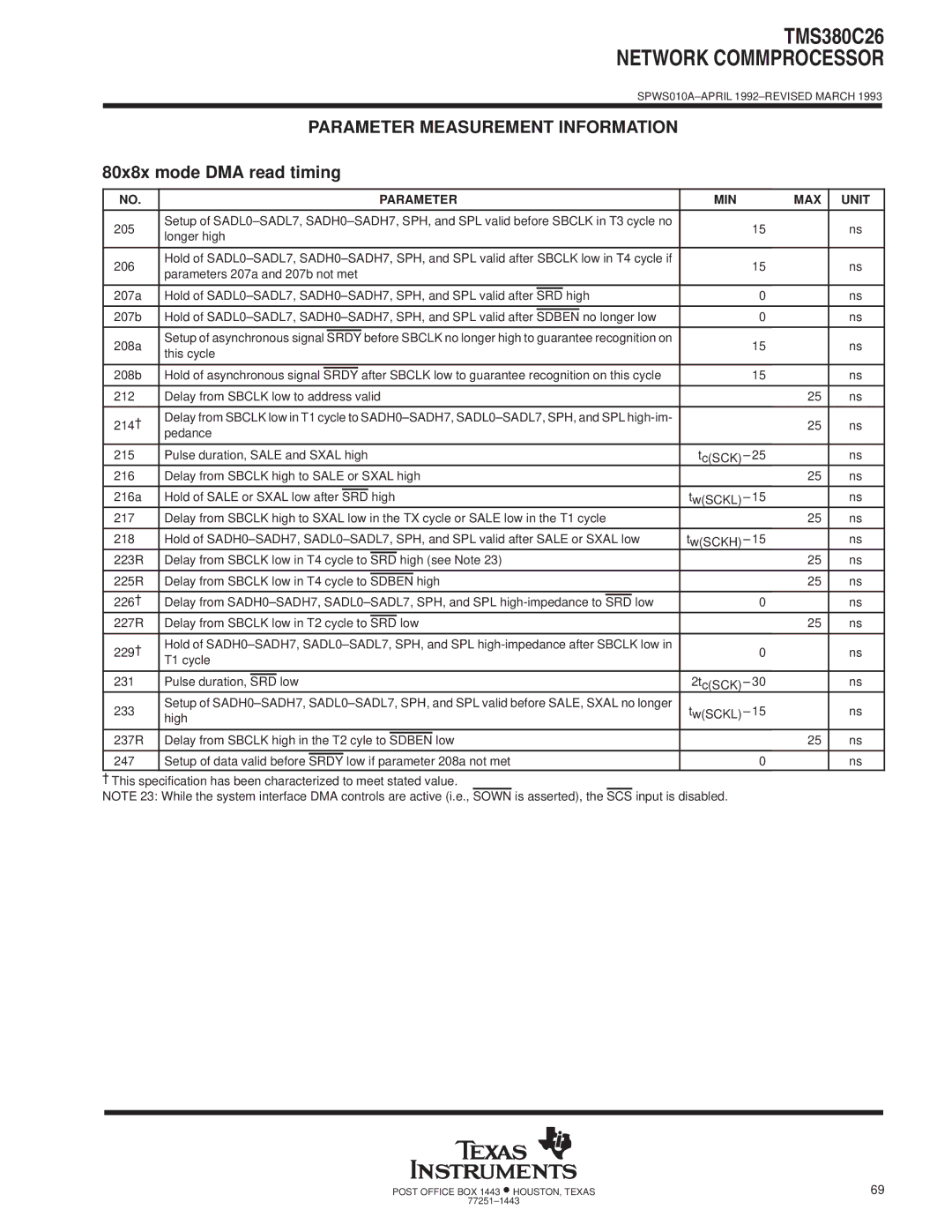

212 Delay from Sbclk low to address valid 214 ²

After Sbclk low to guarantee recognition on this cycle

This cycle 208b

High TwSCKL ±

Sbclk Sras

Slds

80x8x mode DMA write timing

SADL0±SADH7

SRD High

SADH0±SADL7 SPH, SPL

Sddir High

80x8x mode bus arbitration timing, SIF returns control

Sbrls Sown

80x8x mode bus release timing

TW or

208c

68xxx DIO read timing

Siack Srnw

SRS0, SRS1

Suds Slds

SDTACK²HI-Z SADH0±SADH7 SADL0±SADL7,HI-Z SPH, SPL

Suds Slds Sdtack

68xxx DIO write timing

SDBEN³

SCS SRSX, SRS0, SRS1 Siack Srnw

SDTACK²

SADH0±SADH7 SADL0±SADL7,HI-Z SPH, SPL

SCS Siack

68xxx interrupt acknowledge cycle timing

SCS Srnw Sdtack

Siack Sdtack

Sdben SDTACK² HI-Z

SCS, Srsx SRS0, SRS1 Sbhe Siack Srnw Slds

SADH0±SADH7 SADL0±SADL7, HI-ZSPH, SPL

275 282a 255

241 Delay from Sbclk high in TX cycle to High

68xxx mode bus arbitration timing, SIF takes control

Sbgr

Sbrq

SAS, Slds

Sberr Sdtack Sbbsy

Suds Srnw

SADH0±SADH7 HI-Z SADL0±SADL7 SPH, SPL

237R Delay from Sbclk high in the T2 cycle to Low

68xxx mode DMA read timing

On this cycle 208b

Suds SAS

Sale SADL0±SADH7 SADH0±SADL7 SPH, SPL

Sdben Suds Slds

68xxx mode DMA write timing

SADL0±SADH7, SADH0±SADL7 SPL, SPH

SAS

240 ² Setup SRNW,

68xxx mode bus arbitration timing, SIF returns control

Read HI-Z Write

Sbclk Sbgr Sdtack

SIF HI-Z

Write Read

Sown Sberr

68xxx mode bus release and error timing

Sbrls Sown

Sberr Sdtack

Normal completion with delayed start²

Rerun cycle with delayed start²

Sbclk Sdtack Sberr Shalt

TH B TH E Sbclk Sdtack Sberr Shalt Sown

254 0.010 NOM 635 0.025 NOM 76 0.030 NOM

Jedec plastic leaded quad flat package PQ suffix

Jedec NO. Outline Terminals MIN MAX

MO±069±AD

Important Notice