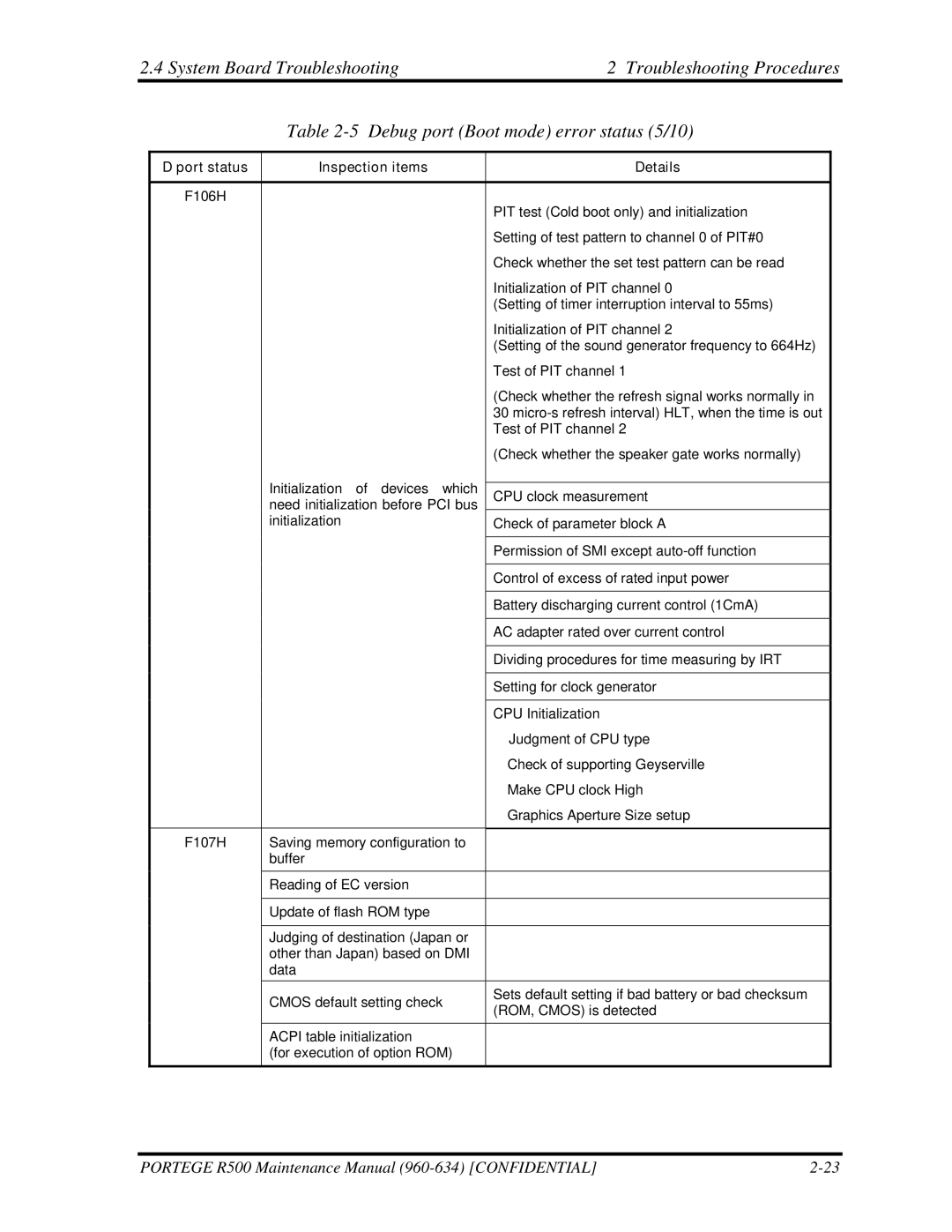

2.4 System Board Troubleshooting | 2 Troubleshooting Procedures |

Table

D port status | Inspection items |

| Details |

|

|

|

|

F106H |

|

| PIT test (Cold boot only) and initialization |

|

|

| |

|

|

| Setting of test pattern to channel 0 of PIT#0 |

|

|

| Check whether the set test pattern can be read |

|

|

| Initialization of PIT channel 0 |

|

|

| (Setting of timer interruption interval to 55ms) |

|

|

| Initialization of PIT channel 2 |

|

|

| (Setting of the sound generator frequency to 664Hz) |

|

|

| Test of PIT channel 1 |

|

|

| (Check whether the refresh signal works normally in |

|

|

| 30 |

|

|

| Test of PIT channel 2 |

|

|

| (Check whether the speaker gate works normally) |

| Initialization of devices | which |

|

| CPU clock measurement | ||

| need initialization before PCI bus | ||

|

| ||

| initialization |

| Check of parameter block A |

|

|

|

|

|

|

| Permission of SMI except |

|

|

|

|

|

|

| Control of excess of rated input power |

|

|

|

|

|

|

| Battery discharging current control (1CmA) |

|

|

|

|

|

|

| AC adapter rated over current control |

|

|

|

|

|

|

| Dividing procedures for time measuring by IRT |

|

|

|

|

|

|

| Setting for clock generator |

|

|

|

|

|

|

| CPU Initialization |

|

|

| Judgment of CPU type |

|

|

| Check of supporting Geyserville |

|

|

| Make CPU clock High |

|

|

| Graphics Aperture Size setup |

|

|

| |

F107H | Saving memory configuration to |

| |

| buffer |

|

|

|

|

|

|

| Reading of EC version |

|

|

|

|

|

|

| Update of flash ROM type |

|

|

|

|

| |

| Judging of destination (Japan or |

| |

| other than Japan) based on DMI |

| |

| data |

|

|

| CMOS default setting check | Sets default setting if bad battery or bad checksum | |

| (ROM, CMOS) is detected | ||

|

|

| |

|

|

|

|

| ACPI table initialization |

|

|

| (for execution of option ROM) |

| |

|

|

|

|

PORTEGE R500 Maintenance Manual |