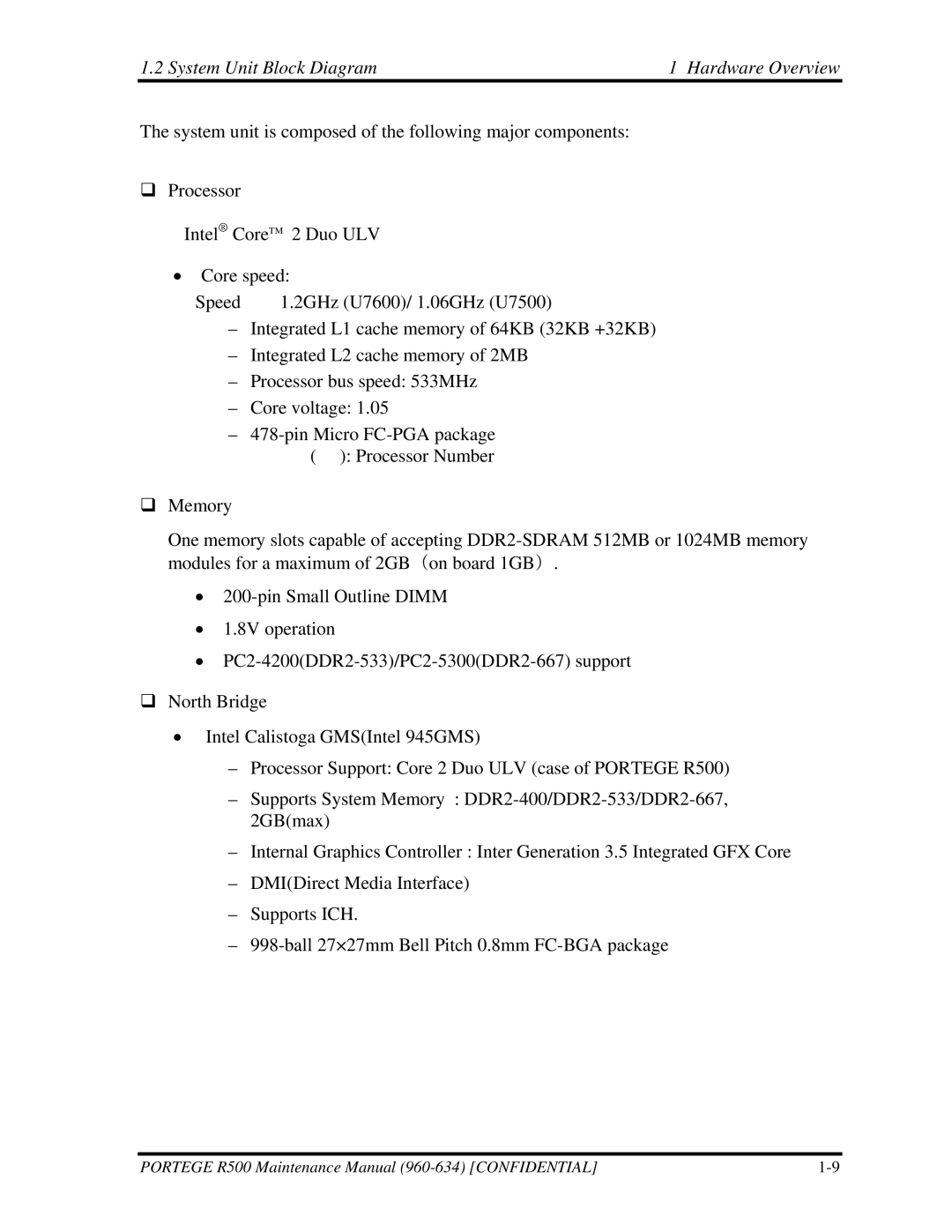

1.2 System Unit Block Diagram | 1 Hardware Overview |

The system unit is composed of the following major components:

Processor

Intel® CoreTM 2 Duo ULV

•Core speed:

Speed | 1.2GHz (U7600)/ 1.06GHz (U7500) |

–Integrated L1 cache memory of 64KB (32KB +32KB)

–Integrated L2 cache memory of 2MB

–Processor bus speed: 533MHz

–Core voltage: 1.05

–

( ): Processor Number

Memory

One memory slots capable of accepting

•

•1.8V operation

•

North Bridge

•Intel Calistoga GMS(Intel 945GMS)

–Processor Support: Core 2 Duo ULV (case of PORTEGE R500)

–Supports System Memory :

–Internal Graphics Controller : Inter Generation 3.5 Integrated GFX Core

–DMI(Direct Media Interface)

–Supports ICH.

–

PORTEGE R500 Maintenance Manual |