ΜPD75402A

Page

Major Revisions in This Version

Content to be read carefully

Instruction Functions and Application

Remarks

Related Documentation Device Related Documents

Development Tool Related Documents

Other Related Documents

Latest documents should be used for design purposes, etc

Contents

Basic Interval Timer

Interrupt Control Circuit Configuration

Digital INPUT/OUTPUT Ports

Clock Generation Circuit

Standby Mode Setting and Operation States

Standby Mode Reset

Operation After Standby Mode Reset

Standby Mode Application

Contents of Figures

Fig. No Title

Contents of Tables

Table No Title

General

FAX PPC

ECR VCR

General Outline of Functions

For details, see Interrupt Functions

General Ordering Information and Quality Grade

Ordering Information

Quality Grade

VPP

Block Diagram

PORT0 PORT1 PORT2 PORT3 PORT5

INT0 Interrupt INT2 Control

PORT6

General PIN Configuration

SCK

SO/SB0

VPP NC

Prom mode

2 44-Pin Plastic QFP 10mm Normal operating mode

NC NC NC P50

P01/SCK

NC V SS NC P22/PCL

A2 NC NC NC NC

PIN Functions

ΜPD75402A PIN Function List Port Pin List

SCK

SO/SB0

INT0

SCK SB0

PIN Functions Normal Operating Mode

Port 0’s, 1’s Dual-Function Pins

4 INT0 ..... Port 1 Dual-Function Input

5 INT2 ..... Port 1 Dual-Function Input

PCL ..... Port 2 Dual-Function Output

Reset Reset

7 X1, X2 Crystal

PIN Functions Prom Mode

CE Chip Enable ..... Input

OE Output Enable ..... Input

1 A0 to A14 Address ..... Input

PIN Functions PIN INPUT/OUTPUT Circuits

Pin Input/output Types

Remarks a circle

P22/PCL

OUT

IN/OUT

Type F B Type M a

P00, Reset

PIN Functions Unused PIN Treatment

Features of Architecture and Memory MAP

Data Memory Bank Configuration

FB0H

Fbfh

FF0H Fffh

Addressing Mode List

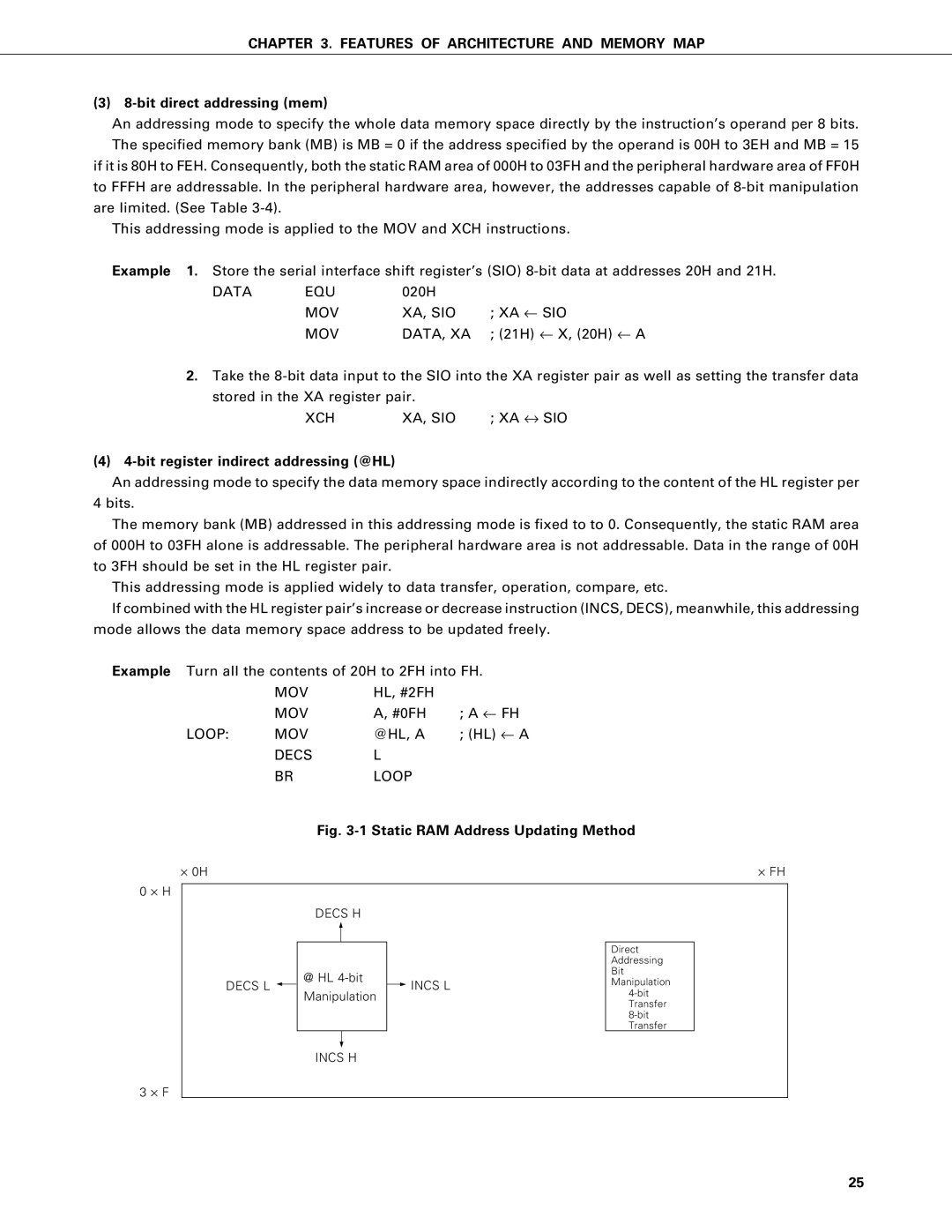

@HL

Data Memory Addressing Modes

Bit direct addressing mem.bit

Bit direct addressing mem

Bit register indirect addressing @HL

Specific address bit manipulation addressing fmem. bit

Stack addressing

SUB Push POP RET

Push HL POP

Push HL Push XA RET

Features of Architecture and Memory MAP MEMORY-MAPPED I/O

Applicable Addressing Modes at Peripheral Hardware Operation

ΜPD75402A I/O Map 1/2

ΜPD75402A I/O Map 2/2

Internal CPU Functions

Program Counter PC .... Bits

PC1 PC0

Program Memory ROM .... ,920 Words × 8 Bits

Program Memory Map

Internal CPU Functions Data Memory RAM

Data area

General register area

Stack area

Peripheral hardware area

General Register Configuration

Internal CPU Functions General Register .... × 4 Bits

Internal CPU Functions Accumulator

Accumulators

Internal CPU Functions Stack Pointer SP .... Bits

Range of 020H to 03FH

MOV SP, XA

SP4 SP3 SP2 SP1 SP0

Data Saved to Stack Memory

IST0 PSW

Internal CPU Functions Program Status Word PSW .... Bits

Carry flag CY

Carry Flag Manipulation Instructions

Interrupt Status Flag Indication Content

SET1

Skip flag SK2, SK1, SK0

Interrupt status flag IST0

Peripheral Hardware Functions

PORT0

Digital Input/Output Port Types and Characteristics

Csim Poga

PO0

PO1

INT2 INT0

Configuration of Port

PO3

Configuration of Ports 2

Input/Output Mode Setting

PM5 Pmgb

Digital Input/Output Port Handling Instructions

Pmga

Fech PM5 PM2 Pmgb

Bit handling instructions

Operations when input mode is set

Operations when output mode is set

Digital Input/Output Port Operations

Operations with Input/Output Port Handling Instructions

Internal Pull-Up Resistor Specification for Each Port

Internal Pull-up Resistors

MOV POGA, XA

PORT1

Fdch PO6 PO3 PO2 PO1 PO0

Digital Input/Output Port Input/Output Timing

Data fetch by 2-machine-cycle instruction

Data latching by 1-machine-cycle instruction

Data latching by 2-machine-cycle instruction

Clock Generation Circuit Configuration

Peripheral Hardware Functions Clock Generation Circuit

Clock Generation Circuit Function and Operaion

Processor clock control register PCC

SEL

MOV PCC, a

FB3H PCC3 PCC2 PCC1 PCC0

PCC

System clock oscillation circuit

12 System Clock Oscillation Circuit External Circuitry

13 Example of Poor Resonator Connection Circuit 2/2

CPU Clock Setting

Use of Variable Minimum Instruction Execution Time Function

Example

15 Change of Φ after Power-On Reset

Maximum Time Required for Change of CPU Clock

Differences Between μPD75402A and μPD75402

17 μPD75402 Processor Clock Control Register Format

FB3H PCC3 PCC2 PCC1

Clock Output Circuit Configuration

Peripheral Hardware Functions Clock Output Circuit

P22/PCL CLOM3 CLOM1 CLOM0 Clom PORT2.2

Clock Output Mode Register Clom

Clom

Clock Output Procedure

Examle of Remote Control Application

Peripheral Hardware Functions Basic Interval Timer

Basic Interval Timer Configuration

MPX

BTM3 BTM2

Basic Intercal Timer Mode Register BTM

MOV BTM. a

BTM3

BTM

Basic Interval Timer Operation

From the beginning

Examples of Basic Interval Timer Applications

MOV BTM,A

Iebt

SEL MOV

Operation-halted mode

Wire serial I/O mode

Peripheral Hardware Functions Serial Interface

Serial Interface Functions

SBI mode serial bus interface mode

Serial Interface Configuration

Serial Interface Block Diagram

Functions

Serial operating mode register Csim

Serial bus interface control register Sbic

Shift register SIO

SO latch

Register Functions Serial operating mode register Csim

Intcsi control circuit

Serial clock control circuit

Serial interface operating mode selection bit W

Serial clock selection bit W

Csie COI WUP CSIM3 CSIM1 Csim

Signal from address comparator R

Csie

MOV CSIM, XA

SET1 Csie

Csie CSIM3

Csie CSIM1

FE2H

Cmdd Reld Cmdt Relt

Command trigger bit W

Command detection flag R

Bus release detection flag R

Acknowledge trigger bit W

Busy enable bit R/W

Acknowledge detection flag R

SIO

CLK

BUSY/ACK

Error detection

See 5.5.6 8 Error detection for details

Slave address register SVA

Slave address detection

Register setting

Csie C0I WUP CSIM3 CSIM1 Csim

5 3-Wire Serial I/O Mode Operation

28 Example of 3-Wire Serial I/O System Configuration

Remarks Figuer Apply to fXX = 4.19 MHz operation

Shift register data do not match Register data match

Command trigger bit

FE2H Bsye Ackd Acke Ackt Cmdd Reld Cmdt Relt Sbic

29 3-Wire Serial I/O Mode Timing

Communication operation

Serial Clock Selection and Use in 3-Wire Serial I/O Mode

Signals

Serial clock selection

Relt Cmdt

Data transfer order

Start of transfer

Wire serial I/O mode applications

MOV XA, Tdata

MOV SIO, XA

SCK SO/SB0

MOV XA, Tdata SIO, XA

Iecsi

MOV XA, Tdata XCH XA, SIO

MOV RDATA, XA

SBI Mode Operation

+ VDD

CPU SB0 SCK

SB0 SCK

Address/command/data differentiation function

Acknowledge signal ACK control function

Busy signal Busy control function

SBI functions

SBI definition

SB0 ACK

SB0 C0 ACK Busy

SB0 D0 ACK Busy

Bus release signal REL

Command signal CMD

SCK H

SCK H SB0

Address

37 Slave Selection by Address

Command & data

Data

Acknowledge signal ACK

SCK SB0 ACK

Busy signal BUSY, ready signal Ready

100

SCK SB0 ACK Busy

101

102

103

104

Serial Clock Selection and Use in SBI Mode

105

RELT, CMDT, Reld & Cmdd Operation Slave

106

SIO SCK SB0 Relt Cmdt Reld Cmdd

SIO SCK

44 Ackt Operation

107

When Acke is set after completion of transfer

When Acke = 0 on completion of transfer

When Acke = 1 interval is short

108

When ACK signal is output after 9th SCK clock interval

109

SCK SB0 ACK Ackd

SCK SB0 Bsye ACK

110 Signals in SBI Mode

SCK Cmdd

SB0 ACK Ready

SB0 Ready

111

REL CMD

Pin configuration

Pin Configuration Diagram

Address match detection method

Use of slave address register SVA

113

114

Chapter

Peripheral

Hardware

50 Command Transmission from Master Device to Slave

115

116

51 Data Transmission from Master Device to Slave Device

52 Data Transmission from Slave Device to Master Device

117

Points to note concerning SBI mode

118

SBI mode application

Serial bus configuration

119

Description of commands Command types

Ii Communication procedure

120

Iii Command formats

➀ Read command

➁ WRITE, END and Stop commands

121

122

MSM

ACK Stop

➂ Status command

123

Status

MSB LSB

Reset command

➄ Chgmst command

124

Chgmst

Iv Error occurrence

Errors generated on the slave side

Errors generated on the master side

125

Interrupt Functions

127

Interrupt Functions Interrupt Source Types and Vector Table

Interrupt Request Source Types

VEN T1 GOT OBT

VENT1 Gotobt VENT2 GOTO0

Interrupt request flag & interrupt enable flag

Interrupt Request Flag Setting Signal

Example EI

IE0

External interrupt input pin hardware

130

INT0 Noise Elimination Circuit Input/Output Timing

INT2 Input Noise Elimination

Interrupt master enable flag IME

132

FB4H IM03

FB2H

Interrupt status flag

IST0 Interrupt Servicing Status

133

Interrupt Functions Interrupt Sequence

YES

IME=1

Interrupt INTxxx generation

136

Interrupt Functions Interrupt Applications

Interrupt enabling/disabling

EI Iecsi

Example using INTBT, INT0 falling edge active, and Intcsi

138

CLR1 IRQ0

➄ Reti

139

EI IE0

➂ Intcsi Reti

➃ EI Iecsi Reti

Pending interrupt execution

140

INT0 Intcsi ➁ Reti

Stop mode

Halt mode

Standby Function

Standby Function Standby Mode Setting and Operation States

Standby Mode Operation States

Standby Function Standby Mode Reset

Stop mode reset by Reset input

Halt mode reset by Reset input

Halt mode reset by interrupt generation

144

Halt

Standby Function Operation After Standby Mode Reset

IME =

Reset Signal Acceptance

Reset at Power-on

State of Hardware after Reset

147

OFF

Architecture and Memory MAP

148

Instruction SET Special Instructions

Bit Manipulation Instructions

Stack Instructions

Example A0

Base Correction Instructions

Base correction at addition

Addc

Adds Addc

Instruction SET Instruction SET and ITS Operation

Operation identifier and description

Operation description legend

Description of addressing area field symbols

Description of machine cycle field

152

Movt XA, @PCXA

Adds

Addc

XOR

154

Instruction Group

Instructions

155

NOP

Description of operation code symbols

Instruction SET Operation Code of Each Instruction

Bit manipulation addressing operation code

Iebt Iecsi IE0 IE2

Rorc Not Incs

SET CLR SKT Not

RET Rets Reti Push POP

Halt Stop NOP

Instruction SET Instruction Functions and Application

Move Instructions

MOV A, #0BH

MOV HL, #5FH

MOV XA, 20H

160

Loop XCH

MOV XCH

161

Table Reference Instructions

Table data on that

162

02FFH

Arithmetic and Logic Instructions

See section

163

Or A, @HL

164

Rorc a

165

Incs reg

166

SKE reg, #n4

167

Carry Flag Operation Instructions

168

Bit Manipuration Instructions

169

SKF mem. bit

170

BR addr

171

Subroutine Stack Control Instructions

172

Push rp

173

Interrupt Control Instructions

174

Input/Output Instructions

175

Halt

176

177

178

Language Processor

Prom Writing Tools

179

Debugging Tools

180

Development Tool Configuration

181

IBM PC/AT

182

183

184

Irqcs

Pmgb Cmdd

Port