Apple II Original ROM Information

Qjjj

Data

0005A0 FDA9A920 EDFDA98D 4CEDFDA9 8D4CEDFD

Page

Page

Page

JI@

Page

001AC0 FFFFE1E1 EFEEE7E8 EEE7F3FB FBEEE1EF

001AA0 F3FFE8E1 E8E8EFEB FFFFE0FF Ffefeeef

001AE0 E8EEE7E8 Efefeeef Eeefeeee Efeeeeee

001DB0 9CDD9CDE DD9EC3DD Cfcacdcb 00479AAD

001FB0 Ffffffff FFFF2071 E14CBFEF 2003EEA9

Page

60FFFFFF .JJ

DDBAF9F0 0DBDBAF9

FA60FFFF

02E61FBD JJJ

AEAEA8AD

Page

Page

Return

Page

Basl

System Monitor Copyright

LOC0

LOC1

Mask

INY NO, INC Index X-COORD

LDY PCH

PRMN1 LDA

FMT1 DFB

Format Above

EOR

STA A3H FAE2 A2 FB

Tabv STA Vtabs to ROW in A-REG

STA Bash

BCC Clreol Clear to END of Line

NXTA4 INC A4L Incr 2-BYTE A4

STA BASL,Y Replace Flashing Screen

Fdad A5 3C

LT2 LDA A2L,X Copy A2 2 Bytes to

Ioprt LDA A2L SET RAM IN/OUT Vectors

BCC RD3 Loop Until Done

STA A3H,X

DFB LIST-1 FFF3 CC

BRTBL,X

Save

LSR Prepare Carry for BC, BNC

Stat LDA R0L

JSR STAT2 Push LOW PC Byte VIA R12

JSR

LDA IN,Y

CMP

BNE Nomove

RTN

Mloop

DCR

BNZ Mloop

BM1

INR

BNC

BNZ

Load DOUBLE-BYTE Indirect

Example

Load Indirect

Store Indirect

POP Indirect

Store DOUBLE-BYTE Indirect

Store POP Indirect

Subtract

ACC

POP DOUBLE-BYTE Indirect

BNC LOOP1

Compare

BF A0 SET $A0BF

LOOP1 SUB

BNZ LOOP2

Return to 6502 Mode

Decrement

LOOP2

LOOP3 SUB

Branch if no Carry

Branch if Carry SET

Branch if Plus

Return from Sweet 16 Subroutine

Branch if Minus ONE

Branch if not Minus ONE

Break

STA IND+1 LDA OPTBL,X

LDA #ADRH

STA IND JMP

Page

Page

Sweet 16 Introduction

Page

Source

NVA

DSP

Print Dbload Sweet REM Ctrl D

Input Enter String a $ , a $

Sweet

Poke 776 , a REM Poke Destination

Print Print Goto

Call -605 Return REM XAM8 in Monitor

Mnemr

MINI-ASSEMBLER

Baum

Mneml

SBC PCL Form ADDR-PC-2

JSR Cout Position

FORM7 STX A1H Save Index

BNE

ORG

CLC

STA

Norm LDA EXP1 ZERO?

Shift Dividend Left

Floating Point Representation LOW

Floating Point Package

Number Exponent Mantissa

Stored

High LOW EXP Mantissa

Floating Point Representation Examples

Floating Point Subroutine Descriptions

Page

Page

Page

Page

HIGH-ORDER

STY Init MANT1 LDY

STY

Calling Sequence

Page

Page

Page

Page

Page

Page

Mmmmmmmm

Seeeeeee

Fsub

ORG SET Base page Adresses

STA X2,X

Common LOG of MANT/EXP1 Result in MANT/EXP1

Ovflw BRK Overflow

1EBB STA X2,X Load EXP/MANT2 with Z 1EBD DEX 1EBE BPL LF3

Addend

YES,RETURN with MANT1 Normalized

Right Shift MANT1 or Swap with MANT2 on Carry

CMP

Normx BCC Norm If EXEN, Normalize PRODUCT, Else Complement

LDX Load X for High Byte of Exponent

Errata for Rankins Floating Point Routines

LDA STA

Fmul

LOG

Fadd

Fsub

Page

Mantissa

MOD 9/76 Load X for Later

M2MHL

Contin

1EAD LFA LDA Z,X

L2E DCM

Mdend

RTLOG1

Normx

Object Code Dump

Page

Lstcom

Tapdel

Hsbdry

Toutfl

=UIRQVC

Outvec

Urcvec

=UBRKVC

ADC

TAX

Stocom STA

ORA

BPL HASHUS+2

Restore Except A,F

JMP

BEQ

STX

CPX

TXA

Exwrap RTS

Chksad PHP

Outxah PHA

Nibasc and #$0F Nibble in a to Ascii in a

BCS INST1

RTI

Ldbyte JSR Inbyte

Verify MEM

E1PARM JMP

STD2

MORED2 LDY

JSR Brtt INC Ercnt UP to FF

MEM3EX CLC

SBC P3L

BNE Exitgk

Ksconf LDA

Txtmov LDA

BNE INRT2

Outone

Newdev LDA

Dftxfr LDX

LDA Toutfl

8BFF 0D

Msfirst

Ddrdig

Bufadh

LOADT2

STA Mode

BNE Lcerr Last Char not

Kgettr LDA

H8DFF

BCC PACKT3

DUMPT4 LDY

Dumpt

DUMPT1 TXA

DMPT1A LDA

Outbth LDX

Outcht STX

Register Name Patch

HS Tape Boundary

Nowln

Rockwell International

Udrah

Uddra

TMASK1 =MOVAD

Oldlen

Length

Movad

TABUF2

Curpos

Checksum

Tabuff

Write Edge Detect Control not Used Because KB

EQS

CRB

CFD2A0A0A0A0

DB TO,EQS

SEI Disable Interrupt

RS6 JSR Crlow Clear Display

E1AC Have Valid Command

Space Comm

Nxtadd TYA

LOAD1A LDA

For

LOADK5 LDX

JMP LOADK5 Next

E46A EE INC Bkflg SET FLG

OUTCK1 PHA

Outcks LDA

DUMPT1 LDA

Dumpta LDX

E5EA

TOGTA1 LDA

TOGTA2 LDA

BCC JD3

MSG

Whereo LDY

CPY

ANY Other

STA Outflg

Outall PHA

Output PHA

ROL Priflg Restore FLG

Wrax JSR Numa

EAA3 CA DEX

Memerr JSR

STA STIY+2

Dehalf LDA

EC5E 4A LSR Only ROW

Debkey LDX

Onekey LDA

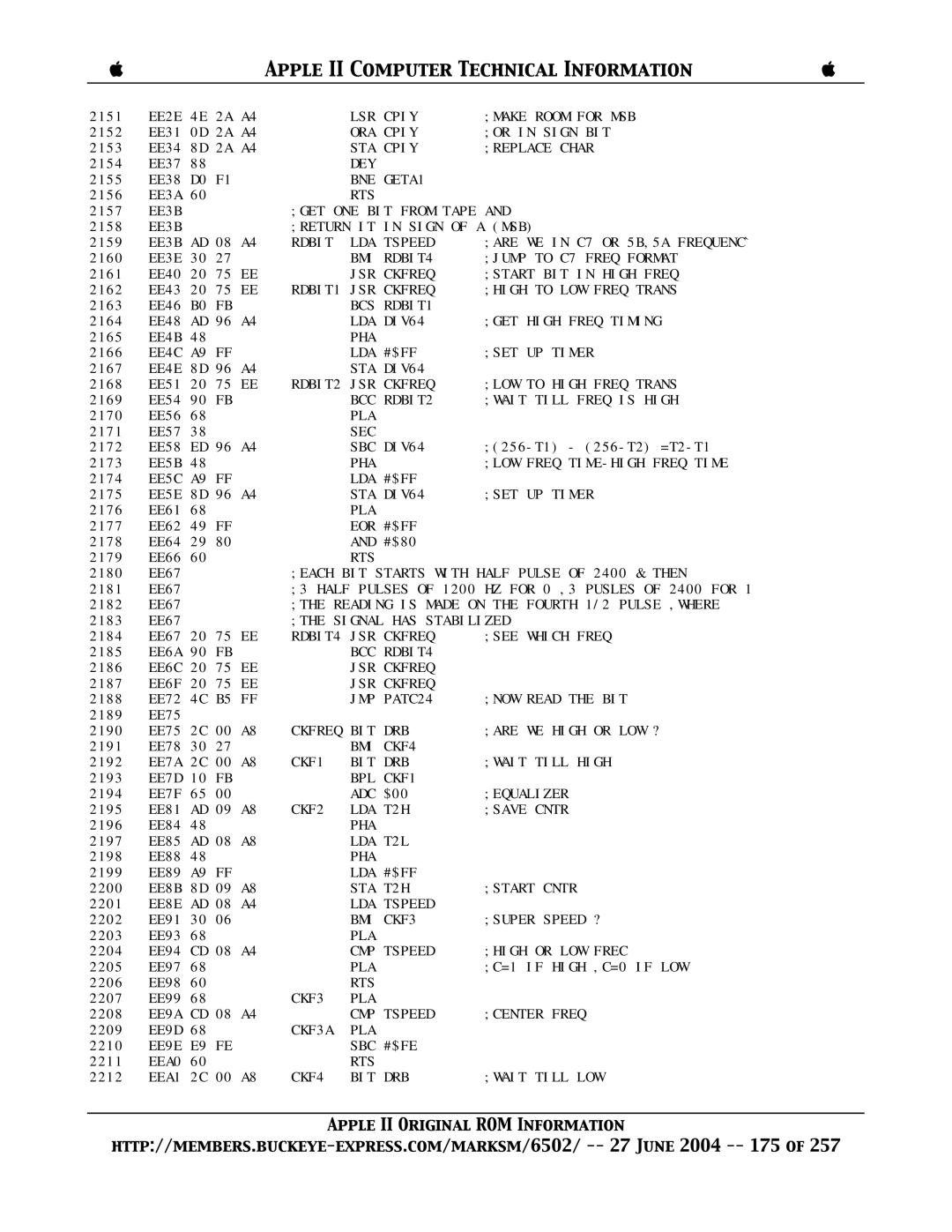

ED3B GET a Char from Tape Subroutine

Edba

LSR Cpiy Make Room for MSB

Outtty PHA

OUTD2A TXA

OUTD1A CPX

OUTDD1 PHA

LDA First Chip Select

Prndot LDA

LDA #PRTIME/256 Start T2 for 1.7 Msec

BIT Imask See if DOT is SET

Newcol LDA

NEW Print ROW

Bkcksm LDA

Ckbuff LDA

OUTTA2 LDX

OUTTA1 PHA

Zero Leftmost Column

F2E1 3E7E7F3E7F7FCOL0

DB BGYU76HN

MNNDX2 LSR

Rtmode

Getfmt TAX

MNNDX1 LSR

PLA

PRADR2 LDA

PRADR4 DEX

BPL PCADJ4

AIM Text Editor

LDA END+1 CMP with END

AF E7 JMP KEP

RUB

COMMAND-FIND String

JMP CHN1

See if WE RAN Past END of Buffer Limit

BEQ REP2

SBC Oldlen

GOGO1 RTS

FB46 8A9AAABACADA

ROM Table

Startm JSR

Rdaddr LDY

IMMED1 LDX

Tryjmp LDA

Brnchc JMP

OPCMP1 LDA

Convrt LDA

Brcomp LDA

FORMD2 LDX

Compbr LDX

Forwrd LDA

Backwd LDA

Curead TXA

MATCH1 JMP

PATCH4 LDX CURPO2 Dont do Anything if 8D

PATC15 JSR Crlf Decode Command

Brcomp

Addblk

ADDS1A

Bkcksm

CRA

Goerr

Namo E8CF NAMO1

RD2 EA5D RD1

E6AC

AIM 65 Microcomputer Monitor Program Listing

AIM 65 Microcomputer Basic Language Reference Manual

Table of Contents

Introduction

WIDTH?

Installing Basic in the AIM ROM Installation Procedure

Entering Basic

Memory SIZE?

Printer Control

Exiting Basic

Reentering Basic

Basic Cursor

ASC

Getting Started with Basic Basic Command SET

CHR$

Listing a Program

Direct and Indirect Commands Direct Commands

Indirect Commands

Operating on Programs and Lines

List Printing Data

Deleting a Line

Replacing a Line

Deleting a Program

Number Format

Print ONE Half Equals 1/2

Number Output Format

Input R

Variables Assigning Variables with AN Input Statement

Variable Names

Print A, A*2 LET Z=7 Print Z, Z-A

PSTG$

Reserved Words

Input B

Program Using Relations

Remarks

Relational Tests

Print Nsqrn

Looping

Square Root Program

AN Improved Square Root Program

Some Other Looping Operations

Another Square Root Program

Print Nsqrn Next N

COUNT-BACKWARD Program

Sort Program

Print What is the Number

Print I,J Next Next J

Matrix Operations

Stopping a Program

Print BAD GUESS, TRY Again Restore

Input N

Print Must be Integer

Print LENA$,LENMICROCOMPUTER

Strings

$=ROCKWELL R6500 Print A$ Rockwell R6500

LEN Function

MID$ Function

RIGHT$ Function

Data AIM 65,DOG

Print B$ Basic for Rockwell R6500

Print C$ Basic FOR-ROCKWELL-R6500 VAL and Strs Functions

CHR$ Function

Print Print X$

Additional String Considerations

Name Example PURPOSE/USE DIM

Input Input X$

Print X/1.3

Operators Symbol Sample Statement

ESC

Cntl Print

Negation

Symbol Sample Statement PURPOSE/USE

Relational Operators

Operator Argument Result Not

Not If not Q3 then

Statement SYNTAX/FUNCTION Example Clear

Commands

Print Intruder Alert

Alert

Statement SYNTAX/FUNCTION NEW

Statement SYNTAX/FUNCTION FRE

Statement SYNTAX/FUNCTION List

Statement SYNTAX/FUNCTION Load

Statement SYNTAX/FUNCTION Example DEF

Statement SYNTAX/FUNCTION Example RUN

Statement SYNTAX/FUNCTION Example Save

Program Statements

Statement SYNTAX/FUNCTION END

Statement SYNTAX/FUNCTION DIM

Statement SYNTAX/FUNCTION For

Statement SYNTAX/FUNCTION IF...THEN

Statement SYNTAX/FUNCTION Gosub

Statement SYNTAX/FUNCTION Goto

Statement SYNTAX/FUNCTION IF...GOTO

Statement SYNTAX/FUNCTION ON...GOSUB

If X0 then Print ERROR, X Negative Goto Example

Statement SYNTAX/FUNCTION LET

Statement SYNTAX/FUNCTION Next

Statement SYNTAX/FUNCTION Return

Statement SYNTAX/FUNCTION Restore

Symbol SYNTAX/FUNCTION Wait

Example Restore Return

Print Value ISA

Statement SYNTAX/FUNCTION Input

Statement SYNTAX/FUNCTION POS

Statement SYNTAX/FUNCTION Print

String Functions Statement SYNTAX/FUNCTION ASC

Statement SYNTAX/FUNCTION Read

Statement SYNTAX/FUNCTION SPC

Statement SYNTAX/FUNCTION TAB

Statement SYNTAX/FUNCTION RIGHT$

Statement SYNTAX/FUNCTION LEFT$

Statement SYNTAX/FUNCTION LEN

Statement SYNTAX/FUNCTION MID$

Statement SYNTAX/FUNCTION EXP

Arithmetic Functions Statement SYNTAX/FUNCTION ABS

Statement SYNTAX/FUNCTION ATN

Statement SYNTAX/FUNCTION COS

Print Sinx

Statement SYNTAX/FUNCTION Example SGN

Print Sgnx

Statement SYNTAX/FUNCTION Example SIN

?XX Error

Error Messages

Inverse Hyperbolic Secant

Space Hints

TAB, SPC

PRINTX,Y,Z

Speed Hints

Storage Allocation Information

OLD

This is Probably the Most Important Speed Hint

Converting Basic Programs not Written for AIM 65 Basic

OLD AIM

SOH

Assembly Language Subroutines

Ascii Character Codes Decimal

NUL

Printx

Address Content

$AE

Inputnumbern

RUN NUMBER?

Recording on Cassette Using the Basic Save Command

Storing AIM 65 Basic Programs on Cassette

IN=

Cassette Operations Using the AIM 65 Editor

OUT=T F=

OUT=T F=FNAME T=

0FAC

ATN Implementation

Entered by Alter Memory M

OF9C

Saving ATN Object Code on Cassette

WIDTH? Bytes Free AIM 65 Basic