Main

How to Reach Us:

Page

Page

Chapter 1 Overview

Chapter 2 Signal Descriptions

Page

Page

Page

Chapter 3 ColdFire Core

Chapter 4 Enhanced Multiply-Accumulate Unit (EMAC)

Chapter 5 Memory Management Unit (MMU)

Chapter 6 Floating-Point Unit (FPU)

Chapter 7 Local Memory

Chapter 8 Debug Support

Chapter 9 System Integration Unit (SIU)

Chapter 10 Internal Clocks and Bus Architecture

Chapter 11 General Purpose Timers (GPT)

Chapter 12 Slice Timers (SLT)

Chapter 13 Interrupt Controller

Chapter 14 Edge Port Module (EPORT)

Chapter 15 GPIO

Chapter 16 32-Kbyte System SRAM

Chapter 17 FlexBus

Chapter 18 SDRAM Controller (SDRAMC)

Page

Chapter 19 PCI Bus Controller

Page

Chapter 20 PCI Bus Arbiter Module

Chapter 21 FlexCAN

Chapter 22 Integrated Security Engine (SEC)

Page

Chapter 23 IEEE 1149.1 Test Access Port (JTAG)

Chapter 24 Multichannel DMA

Page

Chapter 25 Comm Timer Module (CTM)

Chapter 26 Programmable Serial Controller (PSC)

Page

Page

Chapter 27 DMA Serial Peripheral Interface (DSPI)

Chapter 28 I2C Interface

Chapter 29 USB 2.0 Device Controller

Page

Page

Page

Chapter 31 Mechanical Data

Page

About This Book

Audience

Organization

Page

Suggested Reading

General Information

ColdFire Documentation

Conventions

Register Conventions

Acronyms and Abbreviations

Table ii. . Acronyms and Abbreviated Terms (continued)

Terminology and Notational Conventions

Table iii shows notational conventions used throughout this document.

Table iii. Notational Conventions

Table ii. . Acronyms and Abbreviated Terms (continued)

Table iii. Notational Conventions (continued)

Table iv. MCF548x Revision History

Table iii. Notational Conventions (continued)

Page

Page

lii Freescale Semiconductor

Section/Page Substantive Changes

Page

Table iv. MCF548x Revision History (continued)

Page

Page

Page

Page

Chapter 1 Overview

1.1 MCF548x Family Overview

1.2 MCF548x Block Diagram

Figure 1-1. MCF548x Block Diagram

Figure 1-1 shows a top-level block diagram of the MCF548x products.

1.3 MCF548x Family Products

1.4 MCF548x Family Features

Table 1-1. MCF548x Family Products

Page

1.4.1 ColdFire V4e Core Overview

1.4.2 Debug Module (BDM)

1.4.3 JTAG

1.4.4 On-Chip Memories

1.4.4.1 Caches

1.4.4.2 System SRAM

1.4.5 PLL and Chip Clocking Options

1.4.6 Communications I/O Subsystem

1.4.6.1 DMA Controller

1.4.6.2 10/100 Fast Ethernet Controller (FEC)

1.4.6.3 USB 2.0 Device (Universal Serial Bus)

1.4.6.4 Programmable Serial Controllers (PSCs)

1.4.6.5 I2C (Inter-Integrated Circuit)

1.4.6.6 DMA Serial Peripheral Interface (DSPI)

1.4.6.7 Controller Area Network (CAN)

1.4.7 DDR SDRAM Memory Controller

1.4.8 Peripheral Component Interconnect (PCI)

1.4.9 Flexible Local Bus (FlexBus)

1.4.10 Security Encryption Controller (SEC)

1.4.11 System Integration Unit (SIU)

1.4.11.1 Timers

1.4.11.2 Interrupt Controller

1.4.11.3 General Purpose I/O

Chapter 2 Signal Descriptions

2.1 Introduction

2.1.1 Block Diagram

Figure 2-1. MCF548x Signals

MCF548x

2-2 Freescale Semiconductor

Table 2-1 lists the signals for the MCF548x in functional group order.

Table 2-1. MCF548x Signal Description

Page

Page

Page

Page

Page

Page

Table 2-2 lists the MCF548x signals in pin number order for the 388 PBGA package.

Table 2-2. MCF5485/MCF5484 Signal Description by Pin Number

Page

Page

Page

Page

Table 2-2. MCF5485/MCF5484 Signal Description by Pin Number (Continued)

2.2 MCF548x External Signals

2.2.1 FlexBus Signals

2.2.1.1 Address/Data Bus (AD[31:0])

2.2.1.2 Chip Select (FBCS[5:0])

2.2.1.3 Address Latch Enable (ALE)

2.2.1.4 Read/Write (R/W)

2.2.1.5 Transfer Burst (TBST)

2.2.1.6 Transfer Size (TSIZ[1:0])

2.2.2 SDRAM Controller Signals

2.2.2.1 SDRAM Data Bus (SDDATA[31:0])

2.2.2.2 SDRAM Address Bus (SDADDR[12:0])

Page

2.2.3 PCI Controller Signals

2.2.4 Interrupt Control Signals

2.2.5 Clock and Reset Signals

2.2.5.1 Reset In (RSTI)

2.2.5.2 Reset Out (RSTO)

2.2.5.3 Clock In (CLKIN)

2.2.6 Reset Configuration Pins

2.2.6.2 AD5FlexBus Size Configuration (FBSIZE)

2.2.6.3 AD432-bit FlexBus Configuration (FBMODE)

2.2.6.4 AD3Byte Enable Configuration (BECONFIG)

2.2.6.5 AD2Auto Acknowledge Configuration (AACONFIG)

2.2.6.6 AD[1:0]Port Size Configuration (PSCONFIG)

2.2.7 Ethernet Module Signals

2.2.7.1 Management Data (E0MDIO, E1MDIO)

Page

2.2.8 Universal Serial Bus (USB)

2.2.9 DMA Serial Peripheral Interface (DSPI) Signals

2.2.10 FlexCAN Signals

2.2.11 I2C I/O Signals

2.2.12 PSC Module Signals

2.2.13 DMA Controller Module Signals

2.2.14 Timer Module Signals

2.2.14.1 Timer Inputs (TIN[3:0])

2.2.14.2 Timer Outputs (TOUT[3:0])

2.2.15 Debug Support Signals

2.2.15.1 Processor Clock Output (PSTCLK)

2.2.16 Test Signals

2.2.16.1 Test Mode (MTMOD[3:0])

2.2.17 Power and Reference Pins

Page

Part I Processor Core

Page

Chapter 3 ColdFire Core

3.1 Core Overview

3.2 Features

3.2.1 Enhanced Pipelines

Figure 3-1. ColdFire Enhanced Pipeline

3.2.1.1 Instruction Fetch Pipeline (IFP)

3.2.1.2 Operand Execution Pipeline (OEP)

Page

3.2.1.3 Harvard Memory Architecture

3.2.2 Debug Module Enhancements

3.3 Programming Model

Figure 3-3. ColdFire Programming Model

3.3.1 User Programming Model

3.3.1.1 Data Registers (D0D7)

3.3.1.2 Address Registers (A0A6)

3.3.2 User Stack Pointer (A7)

3.3.2.1 Program Counter (PC)

3.3.3 EMAC Programming Model

3.3.4 FPU Programming Model

3.3.5 Supervisor Programming Model

3.3.5.1 Status Register (SR)

3.3.5.2 Vector Base Register (VBR)

3.3.5.3 Cache Control Register (CACR)

3.3.5.4 Access Control Registers (ACR0ACR3)

3.3.5.5 RAM Base Address Registers (RAMBAR0 and RAMBAR1)

3.3.6 Programming Model Table

Table 3-4. ColdFire CPU Registers

3.4 Data Format Summary

3.4.1 Data Organization in Registers

3.4.1.1 Integer Data Format Organization in Registers

3.4.1.2 Integer Data Format Organization in Memory

3.4.2 EMAC Data Representation

+=

()2

value 1 a

3.4.2.1 Floating-Point Data Formats and Types

3.5 Addressing Mode Summary

3.6 Instruction Set Summary

3.6.1 Additions to the Instruction Set Architecture

Table 3-6. ColdFire Effective Addressing Modes

Page

Table 3-7. V4 New Instruction Summary (Continued)

3.6.2 Instruction Set Summary

Table 3-8 lists user-mode instructions by opcode.

Table 3-8. User-Mode Instruction Set Summary

Table 3-7. V4 New Instruction Summary (Continued)

Page

Page

Page

Table 3-9 describes supervisor-mode instructions.

3.7 Instruction Execution Timing

3.7.1 MOVE Instruction Execution Timing

Page

3.7.2 One-Operand Instruction Execution Timing

Table 3-14 shows standard timings for single-operand instructions.

Table 3-13. MAC and Miscellaneous Move Execution Times

Table 3-14. One-Operand Instruction Execution Times

3.7.3 Two-Operand Instruction Execution Timing

Table 3-15 shows standard timings for double operand instructions.

Table 3-15. Two-Operand Instruction Execution Times

3.7.4 Miscellaneous Instruction Execution Timing

Table 3-16 lists timings for miscellaneous instructions.

Table 3-16. Miscellaneous Instruction Execution Times

Table 3-15. Two-Operand Instruction Execution Times (Continued)

3.7.5 Branch Instruction Execution Timing

Table 3-17 shows general branch instruction timing.

Table 3-17. General Branch Instruction Execution Times

Table 3-16. Miscellaneous Instruction Execution Times (Continued)

Table 3-18 shows timing for Bcc instructions.

3.7.6 EMAC Instruction Execution Times

Table 3-18. Bcc Instruction Execution Times

Table 3-19. EMAC Instruction Execution Times

3.7.7 FPU Instruction Execution Times

Table 3-20 specifies the instruction execution times associated with the FPU execute engine.

Table 3-20. FPU Instruction Execution Times1, 2

Table 3-19. EMAC Instruction Execution Times

3.8 Exception Processing Overview

Page

3.8.1 Exception Stack Frame Definition

3.8.2 Processor Exceptions

Table 3-22. Format/Vector Word

Table 3-23. Processor Exceptions

Table 3-23. Processor Exceptions (Continued)

3.9 Precise Faults

Page

Page

Chapter 4 Enhanced Multiply-Accumulate Unit (EMAC)

4.1 Introduction

4.1.1 MAC Overview

4.1.2 General Operation

yi() a

Page

Page

4.2 Memory Map/Register Definition

4.2.1 MAC Status Register (MACSR)

Table 4-1 describes MACSR fields.

Figure 4-7. MAC Status Register (MACSR) Table 4-1. MACSR Field Descriptions

Table 4-2 summarizes the interaction of the MACSR[S/U,F/I,R/T] control bits.

Table 4-1. MACSR Field Descriptions (Continued)

4.2.1.1 Fractional Operation Mode

Page

4.2.2 Mask Register (MASK)

4.3 EMAC Instruction Set Summary

4.3.1 EMAC Instruction Execution Timing

4.3.2 Data Representation

+=

()2

value 1 a

ai

4.3.3 EMAC Opcodes

Page

Page

Page

Page

Page

Chapter 5 Memory Management Unit (MMU)

5.1 Features

5.2 Virtual Memory Management Architecture

5.2.1 MMU Architecture Features

5.2.2 MMU Architecture Location

Figure 5-1. CF4e Processor Core Block with MMU

5.2.3 MMU Architecture Implementation

5.2.3.1 Precise Faults

5.2.3.2 MMU Access

5.2.3.3 Virtual Mode

5.2.3.4 Virtual Memory References

5.2.3.5 Instruction and Data Cache Addresses

5.2.3.6 Supervisor/User Stack Pointers

5.2.3.7 Access Error Stack Frame

5.2.3.8 Expanded Control Register Space

5.2.3.9 Changes to ACRs and CACR

5.2.3.10 ACR Address Improvements

Table 5-1. New ACR and CACR Bits

5.2.3.11 Supervisor Protection

5.3 Debugging in a Virtual Environment

5.4 Virtual Memory Architecture Processor Support

5.4.1 Precise Faults

5.4.2 Supervisor/User Stack Pointers

5.4.3 Access Error Stack Frame Additions

5.5 MMU Definition

5.5.1 Effective Address Attribute Determination

5.5.2 MMU Functionality

5.5.3 MMU Organization

5.5.3.1 MMU Base Address Register (MMUBAR)

5.5.3.2 MMU Memory Map

5.5.3.3 MMU Control Register (MMUCR)

Table 5-5 describes MMUCR fields.

5.5.3.4 MMU Operation Register (MMUOR)

Figure 5-5 shows the MMUOR.

Figure 5-4. MMU Control Register (MMUCR) Table 5-5. MMUCR Field Descriptions

Table 5-6 describes MMUOR fields.

Figure 5-5. MMU Operation Register (MMUOR) Table 5-6. MMUOR Field Descriptions

5.5.3.5 MMU Status Register (MMUSR)

MMUSR, Figure 5-6, is updated on all data access faults and search TLB operations.

Figure 5-6. MMU Status Register (MMUSR)

Table 5-7 describes MMUSR fields.

Table 5-6. MMUOR Field Descriptions (Continued)

5.5.3.6 MMU Fault, Test, or TLB Address Register (MMUAR)

The MMUAR format, Figure 5-7, depends on how the register is used.

Figure 5-7. MMU Fault, Test, or TLB Address Register (MMUAR)

Table 5-8 describes MMUAR fields.

Table 5-7. MMUSR Field Descriptions

5.5.3.7 MMU Read/Write Tag and Data Entry Registers (MMUTR and MMUDR)

Table 5-10 describes MMUDR fields.

Figure 5-9. MMU Read/Write TLB Data Register (MMUDR) Table 5-10. MMUDR Field Descriptions

Table 5-9. MMUTR Field Descriptions (Continued)

5.5.4 MMU TLB

Table 5-10. MMUDR Field Descriptions (Continued)

5.5.5 MMU Operation

5.6 MMU Implementation

5.6.1 TLB Address Fields

5.6.2 TLB Replacement Algorithm

5.6.3 TLB Locked Entries

Figure 5-11. Version 4 ColdFire MMU Harvard TLB

5.7 MMU Instructions

Page

Chapter 6 Floating-Point Unit (FPU)

6.1 Introduction

6.1.1 Overview

6.1.1.1 Notational Conventions

Table 6-2 describes addressing modes and syntax for floating-point instructions.

Table 6-1. Notational Conventions (Continued)

6.2 Operand Data Formats and Types

6.2.1 Signed-Integer Data Formats

6.2.2 Floating-Point Data Formats

6.2.3 Floating-Point Data Types

6.2.3.1 Normalized Numbers

6.2.3.2 Zeros

6.2.3.3 Infinities

6.2.3.4 Not-A-Number

6.2.3.5 Denormalized Numbers

Table 6-3. Real Format Summary (Continued)

6.3 Register Definition

6.3.1 Floating-Point Data Registers (FP0FP7)

6.3.2 Floating-Point Control Register (FPCR)

Table 6-4 describes FPCR fields.

Figure 6-9. Floating-Point Control Register (FPCR) Table 6-4. FPCR Field Descriptions

6.3.3 Floating-Point Status Register (FPSR)

6.3.4 Floating-Point Instruction Address Register (FPIAR)

6.4 Floating-Point Computational Accuracy

6.4.1 Intermediate Result

6.4.2 Rounding the Result

Freescale Semiconductor 6-13

Figure 6-12. Rounding Algorithm Flowchart

6.5 Floating-Point Post-Processing

6.5.1 Underflow, Round, and Overflow

6.5.2 Conditional Testing

Page

6.6 Floating-Point Exceptions

Table 6-9. Floating-Point Conditional Tests (Continued)

6.6.1 Floating-Point Arithmetic Exceptions

6.6.1.1 Branch/Set on Unordered (BSUN)

6.6.1.2 Input Not-A-Number (INAN)

6.6.1.3 Input Denormalized Number (IDE)

6.6.1.4 Operand Error (OPERR)

6.6.1.5 Overflow (OVFL)

6.6.1.6 Underflow (UNFL)

6.6.1.7 Divide-by-Zero (DZ)

6.6.1.8 Inexact Result (INEX)

6.6.2 Floating-Point State Frames

Page

6.7 Instructions

6.7.1 Floating-Point Instruction Overview

Table 6-24 defines the terminology used in Table 6-23.

Table 6-24. Instruction Format Terminology

Table 6-23. Floating-Point Instruction Formats (Continued)

6.7.2 Floating-Point Instruction Execution Timing

6.7.3 Key Differences between ColdFire and M68000 FPU Programming Models

Page

Page

Chapter 7 Local Memory

7.1 Interactions between Local Memory Modules

7.2 SRAM Overview

7.3 SRAM Operation

7.4 SRAM Register Definition

7.4.1 SRAM Base Address Registers (RAMBAR0/RAMBAR1)

RAMBARn fields are described in detail in Table 7-1.

Figure 7-1. SRAM Base Address Registers (RAMBARn) Table 7-1. RAMBARn Field Description

7.5 SRAM Initialization

7.5.1 SRAM Initialization Code

7.6 Power Management

7.7 Cache Overview

7.8 Cache Organization

7.8.1 Cache Line States: Invalid, Valid-Unmodified, and Valid-Modified

7.8.2 The Cache at Start-Up

Figure 7-4. Data CacheA: at Reset, B: after Invalidation, C and D: Loading Pattern

7.9 Cache Operation

Page

7.9.1 Caching Modes

7.9.1.1 Cacheable Accesses

7.9.1.2 Cache-Inhibited Accesses

7.9.2 Cache Protocol

7.9.2.1 Read Miss

7.9.2.2 Write Miss (Data Cache Only)

7.9.2.3 Read Hit

7.9.2.4 Write Hit (Data Cache Only)

7.9.3 Cache Coherency (Data Cache Only)

7.9.4 Memory Accesses for Cache Maintenance

7.9.4.1 Cache Filling

7.9.4.2 Cache Pushes

7.9.5 Cache Locking

Figure 7-7. Data Cache Locking

7.10 Cache Register Definition

7.10.1 Cache Control Register (CACR)

Page

Table 7-4. CACR Field Descriptions (Continued)

7.10.2 Access Control Registers (ACR0ACR3)

7.11 Cache Management

Page

Page

7.12 Cache Operation Summary

7.12.1 Instruction Cache State Transitions

Figure 7-12. Instruction Cache Line State Diagram

Table 7-6 describes the instruction cache state transitions shown in Figure 7-12.

Table 7-6. Instruction Cache Line State Transitions

7.12.2 Data Cache State Transitions

Table 7-7. Data Cache Line State Transitions

In Table 7-9 the current state is valid.

Table 7-8. Data Cache Line State Transitions (Current State Invalid)

Table 7-9. Data Cache Line State Transitions (Current State Valid)

In Table 7-10 the current state is modified.

7.13 Cache Initialization Code

The following example sets up the cache for FLASH or ROM space only.

Table 7-10. Data Cache Line State Transitions (Current State Modified)

Chapter 8 Debug Support

8.1 Introduction

8.1.1 Overview

8.2 Signal Descriptions

8.2.1 Processor Status/Debug Data (PSTDDATA[7:0])

Page

8.3 Real-Time Trace Support

8.3.1 Begin Execution of Taken Branch (PST = 0x5)

Table 8-4. Processor Status Encoding (Continued)

8.3.2 Processor Stopped or Breakpoint State Change (PST = 0xE)

8.3.3 Processor Halted (PST = 0xF)

8.4 Memory Map/Register Definition

Figure 8-5. Debug Programming Model

Table 8-6. BDM/Breakpoint Registers

8.4.1 Revision A Shared Debug Resources

8.4.2 Configuration/Status Register (CSR)

Table 8-8 describes CSR fields.

Figure 8-6. Configuration/Status Register (CSR) Table 8-8. CSR Field Descriptions

Table 8-8. CSR Field Descriptions (Continued)

8.4.3 PC Breakpoint ASID Control Register (PBAC)

Figure 8-7. PC Breakpoint ASID Control Register (PBAC)

Table 8-8. CSR Field Descriptions (Continued)

8.4.4 BDM Address Attribute Register (BAAR)

8.4.5 Address Attribute Trigger Registers (AATR, AATR1)

Table 8-11 describes AATR and AATR1 fields.

Table 8-10. BAAR Field Descriptions

8.4.6 Trigger Definition Register (TDR)

Table 8-11. AATR and AATR1 Field Descriptions (Continued)

Table 8-12 describes TDR fields.

Figure 8-10. Trigger Definition Register (TDR) Table 8-12. TDR Field Descriptions

Table 8-12. TDR Field Descriptions (Continued)

8.4.7 Program Counter Breakpoint and Mask Registers (PBRn, PBMR)

8.4.8 Address Breakpoint Registers (ABLR/ABLR1, ABHR/ABHR1)

Table 8-15 describes ABLR and ABLR1 fields.

Table 8-16 describes ABHR and ABHR1 fields.

8.4.9 Data Breakpoint and Mask Registers (DBR/DBR1, DBMR/DBMR1)

Table 8-16. ABHR and ABHR1 Field Description

Table 8-17 describes DBRn fields.

Table 8-18 describes DBMRn fields.

Figure 8-14. Data Breakpoint Registers (DBR/DBR1) Table 8-17. DBRn Field Descriptions

Figure 8-15. Data Breakpoint Mask Registers (DBMR/DBMR1) Table 8-18. DBMRn Field Descriptions

8.4.10 PC Breakpoint ASID Register (PBASID)

8.4.11 Extended Trigger Definition Register (XTDR)

Table 8-21 describes XTDR fields.

Table 8-21. XTDR Field Descriptions

8.4.11.1 Resulting Set of Possible Trigger Combinations

Table 8-21. XTDR Field Descriptions (Continued)

8.5 Background Debug Mode (BDM)

8.5.1 CPU Halt

Page

8.5.2 BDM Serial Interface

8.5.2.1 Receive Packet Format

Table 8-22 describes receive BDM packet fields.

8.5.2.2 Transmit Packet Format

The basic transmit packet, Figure 8-20, consists of 16 data bits and 1 control bit.

8.5.3 BDM Command Set

Figure 8-19. Receive BDM Packet Table 8-22. Receive BDM Packet Field Description

Figure 8-20. Transmit BDM Packet Table 8-23. Transmit BDM Packet Field Description

Table 8-24. BDM Command Summary

8.5.3.1 ColdFire BDM Command Format

8.5.3.2 Command Sequence Diagrams

Page

8.5.3.3 Command Set Descriptions

Page

Command Sequence:

Figure 8-28. READ Command Sequence

Operand Data The only operand is the longword address of the requested location.

Figure 8-27.

Page

Page

8-40 Freescale Semiconductor

DUMP does not check for a valid address; it is a valid command only when

Command Sequence:

Operand Data: None

Figure 8-32. DUMP Command Sequence

Figure 8-31. DUMP Command/Result Formats

Page

Page

Page

Page

Page

Table 8-26. ColdFire CPU Control Register Map

Page

Page

Page

Page

8.6 Real-Time Debug Support

8.6.1 Theory of Operation

Page

8.6.1.1 Emulator Mode

8.6.2 Concurrent BDM and Processor Operation

8.7 Debug C Definition of PSTDDATA Outputs

8.7.1 User Instruction Set

Page

Page

Page

Table 8-31 shows the PSTDDATA specification for multiply-accumulate instructions.

Table 8-31. PSTDDATA Values for User-Mode Multiply-Accumulate Instructions

Table 8-32. PSTDDATA Values for User-Mode Floating-Point Instructions

Table 8-31. PSTDDATA Values for User-Mode Multiply-Accumulate Instructions (Continued)

8.7.2 Supervisor Instruction Set

Table 8-33. Data Markers and FPU Operand Format Specifiers

Table 8-34. PSTDDATA Specification for Supervisor-Mode Instructions

Table 8-32. PSTDDATA Values for User-Mode Floating-Point Instructions (Continued)

8.8 ColdFire Debug History

8.8.1 ColdFire Debug Classic: The Original Definition

8.8.2 ColdFire Debug Revision B

8.8.3 ColdFire Debug Revision C

8.8.3.1 Debug Interrupts and Interrupt Requests (Emulator Mode)

8.9 Freescale-Recommended BDM Pinout

Figure 8-51. Recommended BDM Connector

Part II System Integration Unit

Page

Chapter 9 System Integration Unit (SIU)

9.1 Introduction

9.2 Features

9.3 Memory Map/Register Definition

9.3.1 Module Base Address Register (MBAR)

9.3.1.1 System Breakpoint Control Register (SBCR)

Figure 9-1. Module Base Address Register (MBAR)

Figure 9-2. System Breakpoint Control Register (SBCR) Table 9-2. SBCR Field Descriptions

9.3.1.2 SEC Sequential Access Control Register (SECSACR)

Figure 9-3. SEC Sequential Access Control Register (SECSACR) Table 9-3. SECSACR Field Descriptions

Table 9-2. SBCR Field Descriptions (Continued)

9.3.1.3 Reset Status Register (RSR)

Figure 9-5. JTAG Device ID Register (JTAGID)

9.3.1.4 JTAG Device Identification Number (JTAGID)

Figure 9-4. Reset Status Register (RSR) Table 9-4. RSR Field Descriptions

Table 9-5. JTAGID Field Descriptions

Chapter 10 Internal Clocks and Bus Architecture

10.1 Introduction

Figure 10-1. MCF548x Internal Bus Architecture

10.1.1 Block Diagram

Figure 10-1 shows a top-level block diagram of the MCF548x products.

10.1.2 Clocking Overview

10.1.3 Internal Bus Overview

10.1.4 XL Bus Features

10.1.5 Internal Bus Transaction Summaries

10.1.6 XL Bus Interface Operations

10.1.6.1 Basic Transfer Protocol

10.1.6.2 Address Pipelines

10.2 PLL

10.2.1 PLL Memory Map/Register Descriptions

10.2.2 System PLL Control Register (SPCR)

Table 10-2. System PLL Memory Map

Figure 10-4. System PLL Control Register (SPCR) Table 10-3. SPCR Field Descriptions

10.3 XL Bus Arbiter

10.3.1 Features

10.3.2 Arbiter Functional Description

10.3.2.1 Prioritization

10.3.2.2 Bus Grant Mechanism

10.3.2.3 Watchdog Functions

10.3.3 XLB Arbiter Register Descriptions

10.3.3.1 Arbiter Configuration Register (XARB_CFG)

Figure 10-5. Arbiter Configuration Register (XARB_CFG) Table 10-5. XARB_CFG Bit Descriptions

Table 10-4. XL Bus Arbiter Memory Map (Continued)

10.3.3.2 Arbiter Version Register (XARB_VER)

Figure 10-6. Arbiter Version Register (XARB_VER) Table 10-6. VER Field Descriptions

Table 10-5. XARB_CFG Bit Descriptions (Continued)

10.3.3.3 Arbiter Status Register (XARB_SR)

10.3.3.4 Arbiter Interrupt Mask Register (XARB_IMR)

Figure 10-7. Arbiter Status Register (XARB_SR) Table 10-7. XARB_SR Field Descriptions

Figure 10-8. Arbiter Interrupt Mask Register (XARB_IMR) Table 10-8. XARB_IMR Field Descriptions

10.3.3.5 Arbiter Address Capture Register (XARB_ADRCAP)

10.3.3.6 Arbiter Bus Signal Capture Register (XARB_SIGCAP)

10.3.3.7 Arbiter Address Tenure Time Out Register (XARB_ADRTO)

Figure 10-11. Arbiter Address Tenure Time Out Register (XARB_ADRTO)

10.3.3.8 Arbiter Data Tenure Time Out Register (XARB_DATTO)

Table 10-11. XARB_ADRTO Field Descriptions

10.3.3.9 Arbiter Bus Activity Time Out Register (XARB_BUSTO)

10.3.3.10 Arbiter Master Priority Enable Register (XARB_PRIEN)

Figure 10-14. Arbiter Master Priority Enable Register (XARB_PRIEN)

10.3.3.11 Arbiter Master Priority Register (XARB_PRI)

Table 10-16. XARB_PRI Field Descriptions

Chapter 11 General Purpose Timers (GPT)

11.1 Introduction

11.1.1 Overview

11.1.2 Modes of Operation

11.2 External Signals

11.3 Memory Map/Register Definition

11.3.1 GPT Enable and Mode Select Register (GMSn)

Figure 11-1. GPT Enable and Mode Select Register (GMSn) Table 11-2. GMSn Field Descriptions

Table 11-2. GMSn Field Descriptions (Continued)

11.3.2 GPT Counter Input Register (GCIRn)

Figure 11-2. GPT Counter Input Register (GCIRn)

Table 11-2. GMSn Field Descriptions (Continued)

11.3.3 GPT PWM Configuration Register (GPWMn)

Table 11-3. GCIRn Field Descriptions

Figure 11-3. GPT PWM Configuration Register (GPWMn) Table 11-4. GPWMn Field Descriptions

11.3.4 GPT Status Register (GSRn)

Figure 11-4. GPT Status Register (GSRn) Table 11-5. GSRn Field Descriptions

Table 11-4. GPWMn Field Descriptions (Continued)

11.4 Functional Description

11.4.1 Timer Configuration Method

11.4.2 Programming Notes

Chapter 12 Slice Timers (SLT)

12.1 Introduction

12.1.1 Overview

12.2 Memory Map/Register Definition

12.2.1 SLT Terminal Count Register (STCNTn)

12.2.2 SLT Control Register (SCRn)

Figure 12-2. SLT Control Register (SCRn)

Figure 12-1. SLT Terminal Count Register (STCNTn) Table 12-2. STCNTn Field Descriptions

12.2.3 SLT Timer Count Register (SCNTn)

Table 12-3. SCRn Field Descriptions

Figure 12-3. SLT Count Register (SCNTn) Table 12-4. SCNTn Field Descriptions

12.2.4 SLT Status Register (SSRn)

Figure 12-4. SLT Status Register (SSRn) Table 12-5. SSRn Field Descriptions

Chapter 13 Interrupt Controller

13.1 Introduction

13.1.1 68K/ColdFire Interrupt Architecture Overview

13.1.1.1 Interrupt Controller Theory of Operation

Page

13.2 Memory Map/Register Descriptions

13.2.1 Register Descriptions

13.2.1.1 Interrupt Pending Registers (IPRH, IPRL)

Table 13-2. Interrupt Controller Memory Map (Continued)

Figure 13-1. Interrupt Pending Register High (IPRH) Table 13-3. IPRH Field Descriptions

Figure 13-2. Interrupt Pending Register Low (IPRL)

13.2.1.2 Interrupt Mask Register (IMRH, IMRL)

13.2.1.3 Interrupt Force Registers (INTFRCH, INTFRCL)

Table 13-5. IMRH Field Descriptions

Figure 13-4. Interrupt Mask Register Low (IMRL) Table 13-6. IMRL Field Descriptions

Figure 13-5. Interrupt Force Register High (INTFRCH) Table 13-7. INTFRCH Field Descriptions

Figure 13-6. Interrupt Force Register Low (INTFRCL) Table 13-8. INTFRCL Field Descriptions

13.2.1.4 Interrupt Request Level Register (IRLR)

13.2.1.5 Interrupt Acknowledge Level and Priority Register (IACKLPR)

13.2.1.6 Interrupt Control Registers 163 (ICRn)

Figure 13-9. Interrupt Control Registers 163 (ICRn) Table 13-11. ICRn Field Descriptions

Table 13-10. IACKLPR Field Descriptions (Continued)

13.2.1.6.1 Interrupt Sources Table 13-12 lists the interrupt sources for each interrupt request line

Table 13-12. Interrupt Source Assignments

13.2.1.7 Software and Level n IACK Registers (SWIACKR, L1IACKL7IACK)

Table 13-12. Interrupt Source Assignments (Continued)

Page

Chapter 14 Edge Port Module (EPORT)

14.1 Introduction

14.2 Interrupt/General-Purpose I/O Pin Descriptions

14.3 Memory Map/Register Definition

14.3.1 Memory Map

14.3.2 Register Descriptions

14.3.2.1 EPORT Pin Assignment Register (EPPAR)

14.3.2.2 EPORT Data Direction Register (EPDDR)

Figure 14-3. EPORT Data Direction Register (EPDDR)

Figure 14-2. EPORT Pin Assignment Register (EPPAR) Table 14-2. EPPAR Field Descriptions

14.3.2.3 Edge Port Interrupt Enable Register (EPIER)

14.3.2.4 Edge Port Data Register (EPDR)

Figure 14-5. EPORT Port Data Register (EPDR)

Table 14-3. EPDDR Field Descriptions

Figure 14-4. EPORT Port Interrupt Enable Register (EPIER) Table 14-4. EPIER Field Descriptions

14.3.2.5 Edge Port Pin Data Register (EPPDR)

14.3.2.6 Edge Port Flag Register (EPFR)

Figure 14-7. EPORT Port Flag Register (EPFR)

Table 14-5. EPDR Field Descriptions

Figure 14-6. EPORT Port Pin Data Register (EPPDR) Table 14-6. EPPDR Field Descriptions

Table 14-7. EPFR Field Descriptions

Chapter 15 GPIO

15.1 Introduction

Figure 15-1. MCF548x GPIO Module Block Diagram

15.1.1 Overview

15.1.2 Features

15.2 External Pin Description

Page

SDA PFECI2C1 SCL PFECI2C0

Primary Function (Pin Name)1GPIO Alternate

Alternate

Page

15.3 Memory Map/Register Definition

Table 15-3 summarizes all the registers in the MCF548x GPIO module address space.

15.3.1 Register Overview

Table 15-2. MCF548x Multiple-Pin Functions

Table 15-3. MCF548x GPIO Module Memory Map

15.3.2 Register Descriptions

15.3.2.1 Port x Output Data Registers (PODR_x)

Table 15-3. MCF548x GPIO Module Memory Map (Continued)

Page

Figure 15-3. 7-Bit PODR_DSPI Register (PODR_x) Table 15-5. 7-Bit PODR_DSPI Field Descriptions

15.3.2.2 Port x Data Direction Registers (PDDR_x)

Figure 15-6. 5-Bit PODR_FBCS Register Table 15-8. 5-Bit PODR_FBCS Field Descriptions

Page

Page

15.3.2.3 Port x Pin Data/Set Data Registers (PPDSDR_x)

Figure 15-11. 5-Bit PDDR_FBCS Register Table 15-13. 5-Bit PDDR_FBCS Field Descriptions

Page

Page

Table 15-16. 5-Bit PPDSDR_PCIBG and PPDSDR_PCIBR Field Descriptions (Continued)

15.3.2.4 Port x Clear Output Data Registers (PCLRR_x)

Figure 15-17. 8-Bit Port Clear Output Data Registers Table 15-19. 8-Bit PCLRR_x Field Descriptions

Page

15.3.2.5 Port x Pin Assignment Registers (PAR_x)

15.3.2.6 FlexBus Chip Select Pin Assignment Register (PAR_FBCS)

Figure 15-23. Flexbus Chip Select Pin Assignment Register (PAR_FBCS)

Table 15-24. PAR_FBCTL Field Descriptions (Continued)

15.3.2.7 DMA Pin Assignment Register (PAR_DMA)

15.3.2.8 FEC/I2C/IRQ Pin Assignment Register (PAR_FECI2CIRQ)

Table 15-25. PAR_FBCS Field Descriptions

Figure 15-24. DMA Pin Assignment Register (PAR_DMA) Table 15-26. PAR_DMA Field Descriptions

Page

15.3.2.9 PCI Grant Pin Assignment Register (PAR_PCIBG)

Table 15-27. PAR_FEC/I2C/IRQ Field Descriptions (Continued)

15.3.2.10 PCI Request Pin Assignment Register (PAR_PCIBR)

The PAR_PCIBR controls the functions of the PCI request pins. The PAR_PCIBR is read/write.

Table 15-28. PAR_PCIBG Field Descriptions (Continued)

15.3.2.11 PSC3 Pin Assignment Register (PAR_PSC3)

The PAR_PSC3 register controls the functions of the PSC3 pins. The PAR_PSC3 register is read/write.

Figure 15-28. PSC3 Pin Assignment Register (PAR_PCS3) Table 15-30. PAR_PSC3 Descriptions

Table 15-29. PAR_PCIBR Field Descriptions (Continued)

15.3.2.12 PSC2 Pin Assignment Register (PAR_PSC2)

The PAR_PSC2 register controls the functions of the PSC2 pins. The PAR_PSC2 register is read/write.

The PAR_PSC1 register controls the functions of the PSC1 pins. The PAR_PSC1 register is read/write.

15.3.2.13 PSC1 Pin Assignment Register (PAR_PSC1)

Figure 15-29. PSC2 Pin Assignment Register (PAR_PSC2) Table 15-31. PAR_PSC2 Descriptions

15.3.2.14 PSC0 Pin Assignment Register (PAR_PSC0)

The PAR_PSC0 register controls the functions of the PSC0 pins. The PAR_PSC0 register is read/write.

Figure 15-31. PSC0 Pin Assignment Register (PAR_PSC0)

Figure 15-30. PSC1 Pin Assignment Register (PAR_PSC1) Table 15-32. PAR_PCS1 Descriptions

15.3.2.15 DSPI Pin Assignment Register (PAR_DSPI)

Table 15-33. PAR_PCS0 Descriptions

Figure 15-32. DSPI Pin Assignment Register (PAR_DSPI) Table 15-34. PAR_DSPI Descriptions

15.3.2.16 General Purpose Timer Pin Assignment Register (PAR_TIMER)

Figure 15-33. General Purpose Timer Pin Assignment Register (PAR_TIMER)

Table 15-34. PAR_DSPI Descriptions (Continued)

15.4 Functional Description

15.4.1 Overview

Page

Page

Part III On-Chip Integration

Page

Chapter 16 32-Kbyte System SRAM

16.1 Introduction

Long Word 8191

Figure 16-1. SRAM Organization

This chapter explains the operation of the MCF548x 32-Kbyte system SRAM.

16.2 Memory Map/Register Definition

16.2.1 System SRAM Configuration Register (SSCR)

Each field is described in Table 16-2.

Figure 16-2. System SRAM Configuration Register (SSCR) Table 16-2. SSCR Register Field Descriptions

Table 16-1. System SRAM Memory Map (Continued)

16.2.2 Transfer Count Configuration Register (TCCR)

Each field is described in the Table 16-3.

16.2.3 Transfer Count Configuration RegisterDMA Read Channel (TCCRDR)

16.2.4 Transfer Count Configuration RegisterDMA Write Channel (TCCRDW)

16.2.5 Transfer Count Configuration RegisterSEC (TCCRSEC)

16.3 Functional Description

Chapter 17 FlexBus

17.1 Introduction

17.1.1 Overview

17.1.2 Features

17.1.3 Modes of Operation

17.2 Byte Lanes

17.3 Address Latch

Figure 17-2. Multiplexed FlexBus Implementation

17.4 External Signals

Table 17-1. FlexBus Signal Summary

17.4.1 Chip-Select (FBCS[5:0])

17.4.2 Address/Data Bus (AD[31:0])

17.4.3 Address Latch Enable (ALE)

17.4.4 Read/Write (R/W)

17.4.5 Transfer Burst (TBST)

17.4.7 Byte Selects (BE/BWE[3:0])

17.4.8 Output Enable (OE)

17.4.9 Transfer Acknowledge (TA)

17.5 Chip-Select Operation

17.5.1 General Chip-Select Operation

17.5.1.1 8-, 16-, and 32-Bit Port Sizing

17.5.1.2 Global Chip-Select Operation

17.5.2 Chip-Select Registers

Table 17-4. AD[2]/AA Automatic Acknowledge of Boot FBCS0

Table 17-5. AD[1:0]/PS[1:0], Port Size of Boot FBCS0

Table 17-6. Chip-Select Registers

17.5.2.1 Chip-Select Address Registers (CSAR0CSAR5)

CSARn, Figure 17-3, specify the chip-select base addresses.

Figure 17-3. Chip-Select Address Registers (CSARn) Table 17-7. CSARn Field Descriptions

Table 17-6. Chip-Select Registers (Continued)

17.5.2.2 Chip-Select Mask Registers (CSMR0CSMR5)

Table 17-8 describes CSMR fields.

Figure 17-4. Chip-Select Mask Registers (CSMRn) Table 17-8. CSMRn Field Descriptions

17.5.2.3 Chip-Select Control Registers (CSCR0CSCR5)

Table 17-9 describes CSCRn fields.

Figure 17-5. Chip-Select Control Registers (CSCRn) Table 17-9. CSCRn Field Descriptions

Table 17-9. CSCRn Field Descriptions (Continued)

17.6 Functional Description

17.6.1 Data Transfer Operation

17.6.2 Data Byte Alignment and Physical Connections

17.6.3 Address/Data Bus Multiplexing

17.6.4 Bus Cycle Execution

17.6.4.1 Data Transfer Cycle States

Figure 17-7. Data Transfer State Transition Diagram

Table 17-11 describes the states as they appear in subsequent timing diagrams.

Table 17-11. Bus Cycle States

17.6.5 FlexBus Timing Examples

17.6.5.1 Basic Read Bus Cycle

Figure 17-9. Basic Read Bus Cycle

17.6.5.2 Basic Write Bus Cycle

Figure 17-10. Write Cycle Flowchart

17.6.5.3 Bus Cycle Multiplexing

Figure 17-12. Single Word Read Transfer with Muxed 32-A / 16-D or Non-Muxed 16-A / 16-D

Figure 17-13. Single Word Write Transfer with Muxed 32-A / 16-D or Non-Muxed 16-A / 16-D

Page

Figure 17-15. Single Byte Write Transfer with Muxed 32-A / 8-D or Non-Muxed 24-A / 8-D

Figure 17-16. Longword Read Transfer with Muxed 32-A / 32-D

17.6.5.4 Timing Variations

Figure 17-18. Basic Read Bus Cycle (No Wait States)

Figure 17-19. Basic Write Bus Cycle (No Wait States)

Figure 17-20. Read Bus Cycle (One Wait State)

Figure 17-21. Write Bus Cycle (One Wait State)

Figure 17-22. Read Bus Cycle with Two Clock Address Setup (No Wait States)

Figure 17-23. Write Bus Cycle with Two Clock Address Setup (No Wait States)

Figure 17-24. Read Cycle with Two Clock Address Hold (No Wait States)

Figure 17-26 shows a bus cycle that uses address setup, wait states, and address hold.

Figure 17-25. Write Cycle with Two Clock Address Hold (No Wait States)

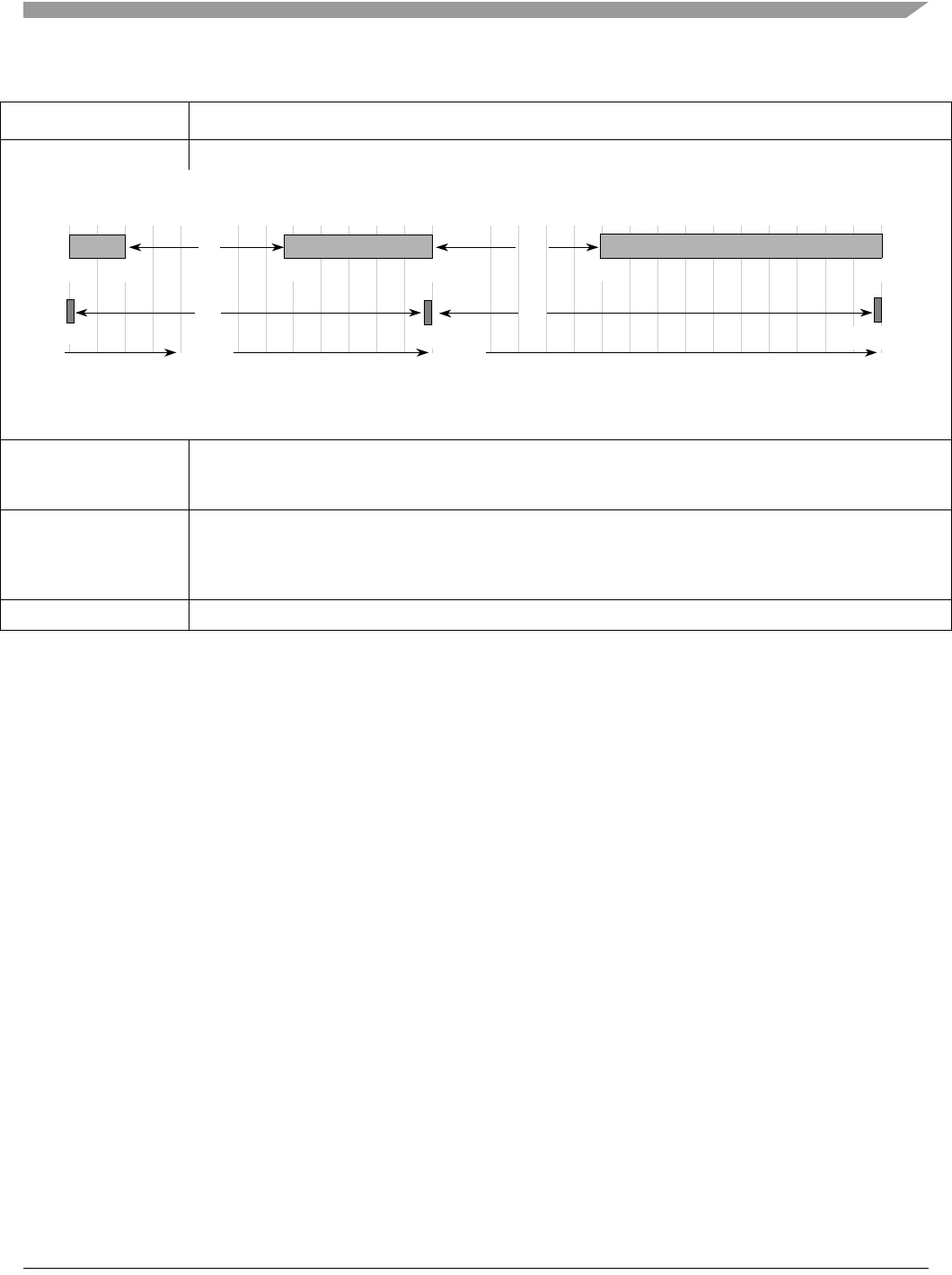

17.6.6 Burst Cycles

Page

Figure 17-28. Longword Write Burst to 8-Bit Port 3-1-1-1 (No Wait States)

Figure 17-29. Longword Read Burst-Inhibited from 8-Bit Port (No Wait States)

Figure 17-30. Longword Write Burst-Inhibited to 8-Bit Port (No Wait States)

Figure 17-31. Longword Read Burst from 8-Bit Port 4-2-2-2 (One Wait State)

Figure 17-31 illustrates a write burst transfer with one wait state.

Figure 17-32. Longword Write Burst to 8-Bit Port 4-2-2-2 (One Wait State)

Figure 17-34 shows a write cycle with one clock of address setup and address hold.

Figure 17-33. Longword Read Burst from 8-Bit Port 4-1-1-1 (Address Setup and Hold)

17.6.7 Misaligned Operands

17.6.8 Bus Errors

Chapter 18 SDRAM Controller (SDRAMC)

18.1 Introduction

18.2 Overview

18.2.1 Features

18.2.2 Terminology

18.3 External Signal Description

18.3.1 SDRAM Data Bus (SDDATA[31:0])

18.3.2 SDRAM Address Bus (SDADDR[12:0])

18.3.3 SDRAM Bank Addresses (SDBA[1:0])

Page

18.3.12 SDRAM Clock Enable (SDCKE)

18.3.13 SDR SDRAM Data Strobe (SDRDQS)

18.3.14 SDRAM Memory Supply (SDVDD)

18.3.15 SDRAM Reference Voltage (VREF)

18.4 Interface Recommendations

18.4.1 Supported Memory Configurations

Table 18-2. SDRAM Address Multiplexing

18.4.2 SDRAM SDR Connections

18.4.3 SDRAM DDR Component Connections

Figure 18-3. MCF548x Connections to DDR SDRAM

18.4.4 SDRAM DDR DIMM Connections

18.4.5 DDR SDRAM Layout Considerations

18.4.5.1 Termination Example

Figure 18-5 shows the recommended termination circuitry for DDR SDRAM signals.

Figure 18-5. MCF548x DDR SDRAM Termination Circuit

18.5 SDRAM Overview

18.5.1 SDRAM Commands

Table 18-3. SDRAM Commands

18.5.1.1 Row and Bank Active Command (ACTV)

18.5.1.2 Read Command (READ)

18.5.1.3 Write Command (WRITE)

18.5.1.4 Precharge All Banks Command (PALL)

18.5.1.5 Load Mode/Extended Mode Register Command (LMR, LEMR)

Page

18.5.1.6 Auto Refresh Command (REF)

18.5.1.7 Self-Refresh (SREF) and Power-Down (PDWN) Commands

18.5.2 Power-Up Initialization

18.5.2.1 SDR Initialization

18.5.2.2 DDR Initialization

18.6 Functional Overview

18.6.1 Page Management

18.6.2 Transfer Size

18.7 Memory Map/Register Definition

18.7.1 SDRAM Drive Strength Register (SDRAMDS)

Figure 18-8. SDRAM Drive Strength Register (SDRAMDS) Table 18-7. SDRAMDS Field Descriptions

Table 18-8. SDRAM Drive Strength Bit Encodings

18.7.2 SDRAM Chip Select Configuration Registers (CSnCFG)

18.7.3 SDRAM Mode/Extended Mode Register (SDMR)

18.7.4 SDRAM Control Register (SDCR)

Figure 18-11. SDRAM Control Register (SDCR) Table 18-11. SDCR Field Descriptions

18.7.5 SDRAM Configuration Register 1 (SDCFG1)

Table 18-11. SDCR Field Descriptions (Continued)

Figure 18-12. SDRAM Configuration Register 1 (SDCFG1) Table 18-12. SDCFG1 Field Descriptions

18.7.6 SDRAM Configuration Register 2 (SDCFG2)

Table 18-12. SDCFG1 Field Descriptions (Continued)

18.8 SDRAM Example

Figure 18-13. SDRAM Configuration Register 2 (SDCFG2) Table 18-13. SDCFG2 Field Descriptions

Table 18-14. SDRAM Example Specifications

18.8.1 SDRAM Signal Drive Strength Settings

This configuration results in a value of SDRAMDS = 0x0000_02AA, as described in Table 18-15.

18.8.2 SDRAM Chip Select Settings

Table 18-14. SDRAM Example Specifications (Continued)

This configuration results in a value of SDRAMDS = 0x0000_0019, as described in Table 18-16.

18.8.3 SDRAM Configuration 1 Register Settings

This configuration results in a value of SDCFG1 = 0x7362_2830, as described in Table 18-17.

The SDCFG1 register should be programmed as shown in Figure 18-16.

18.8.4 SDRAM Configuration 2 Register Settings

The SDCFG2 register should be programmed as shown in Figure 18-17.

This configuration results in a value of SDCFG2 = 0x4677_0000, as described in Table 18-18.

18.8.5 SDRAM Control Register Settings and PALL command

Table 18-17. SDCFG1 Field Descriptions (Continued)

This configuration results in a value of SDCR = 0xE10D_0002, as described in Table 18-19.

18.8.6 Set the Extended Mode Register

The SDMR should be programmed as shown in Figure 18-19. This step enables the DDR memorys DLL.

Figure 18-20. SDRAM Mode/Extended Mode Register Settings (SDMR)

This configuration results in a value of SDMR = 0x048D_0000, as described in Table 18-21.

This configuration results in a value of SDMR = 0x4001_0000, as described in Table 18-20.

18.8.8 Issue a PALL command

This configuration results in a value of SDCR = 0xE10D_0002, as described in Table 18-22.

Table 18-21. SDMR Field Descriptions

18.8.9 Perform Two Refresh Cycles

This configuration results in a value of SDCR = 0xE10D_0004, as described in Table 18-19.

Table 18-22. SDCR + MODE_EN and IPALL Field Descriptions (Continued)

18.8.10 Clear the Reset DLL Bit in the Mode Register

This configuration results in a value of SDMR = 0x008D_0000, as described in Table 18-21.

Figure 18-23. SDRAM Mode/Extended Mode Register Settings Table 18-24. SDMR Field Descriptions

Table 18-23. SDCR + MODE_EN and IREF Field Descriptions (Continued)

18.8.11 Enable Automatic Refresh and Lock Mode Register

This configuration results in a value of SDCR = 0x710D_0F00, as described in Table 18-25.

Figure 18-24. SDRAM Control Register Settings + REF Table 18-25. SDCR + REF Field Descriptions

Table 18-24. SDMR Field Descriptions (Continued)

18.8.12 Initialization Code

Page

Page

Chapter 19 PCI Bus Controller

19.1 Introduction

19.1.1 Block Diagram

19.1.2 Overview

19.1.3 Features

19.2 External Signal Description

19.2.1 Address/Data Bus (PCIAD[31:0])

19.2.2 Command/Byte Enables (PCICXBE[3:0])

Page

19.2.13 Target Ready (PCITRDY)

19.3 Memory Map/Register Definition

Table 19-2. PCI Memory Map (Continued)

19.3.1 PCI Type 0 Configuration Registers

Table 19-2. PCI Memory Map (Continued)

19.3.1.1 Device ID/Vendor ID Register (PCIIDR)PCI Dword Addr 0

19.3.1.2 PCI Status/Command Register (PCISCR)PCI Dword Addr 1

Figure 19-3. PCI Status/Command Register (PCISCR)

Figure 19-2. Device ID/Vendor ID Register (PCIIDR) Table 19-3. PCIIDR Field Descriptions

Table 19-4. PCISCR Field Descriptions

19.3.1.3 Revision ID/Class Code Register (PCICCRIR)PCI Dword 3

Figure 19-4. Revision ID/Class Code Register (PCICCRIR)

Table 19-4. PCISCR Field Descriptions (Continued)

19.3.1.4 Configuration 1 Register (PCICR1)PCI Dword 3

Table 19-5. PCICCRIR Field Descriptions

Figure 19-5. Configuration 1 Register (PCICR1) Table 19-6. PCICR1 Field Descriptions

19.3.1.5 Base Address Register 0 (PCIBAR0)PCI Dword 4

Figure 19-6. Base Address Register 0 (PCIBAR0) Table 19-7. PCIBAR0 Field Descriptions

19.3.1.6 Base Address Register 1 (PCIBAR1)PCI Dword 5

19.3.1.7 CardBus CIS Pointer Register PCICCPRPCI Dword A

19.3.1.8 Subsystem ID/Subsystem Vendor ID Registers PCISIDPCI Dword B

19.3.1.9 Expansion ROM Base Address PCIERBARPCI Dword C

Not implemented. Fixed to 0x0000_0000 at address MBAR + 0xB30.

19.3.2 General Control/Status Registers

Figure 19-8. Configuration 2 Register (PCICR2) Table 19-9. PCICR2 Field Descriptions

19.3.2.1 Global Status/Control Register (PCIGSCR)

Figure 19-9. Global Status/Control Register (PCIGSCR) Table 19-10. PCIGSCR Field Descriptions

19.3.2.2 Target Base Address Translation Register 0 (PCITBATR0)

Table 19-10. PCIGSCR Field Descriptions (Continued)

19.3.2.3 Target Base Address Translation Register 1 (PCITBATR1)

19.3.2.4 Target Control Register (PCITCR)

Figure 19-12. Target Control Register (PCITCR)

19.3.2.5 Initiator Window 0 Base/Translation Address Register (PCIIW0BTAR)

Table 19-13. PCITCR Field Descriptions

Figure 19-13. Initiator Window 0 Base/Translation Address Register (PCIIW0BTAR)

19.3.2.6 Initiator Window 1 Base/Translation Address Register (PCIIW1BTAR)

Table 19-14. PCIIW0BTAR Field Descriptions

Figure 19-14. Initiator Window 1 Base/Translation Address Register (PCIIW1BTAR)

19.3.2.7 Initiator Window 2 Base/Translation Address Register (PCIIW2BTAR)

Figure 19-16. Initiator Window Configuration Register (PCIIWCR)

19.3.2.8 Initiator Window Configuration Register (PCIIWCR)

Figure 19-15. Initiator Window 2 Base/Translation Address Register (PCIIW2BTAR)

19.3.2.9 Initiator Control Register (PCIICR)

Table 19-15. PCIIWCR Field Descriptions

Figure 19-17. Initiator Control Register (PCIICR)

19.3.2.10 Initiator Status Register (PCIISR)

Table 19-16. PCIICR Field Descriptions

Figure 19-18. Initiator Status Register (PCIISR)

19.3.2.11 Configuration Address Register (PCICAR)

Table 19-17. PCIISR Field Descriptions

Figure 19-19. Configuration Address Register (PCICAR) Table 19-18. PCICAR Field Descriptions

19.3.3 Communication Subsystem Interface Registers

Figure 19-20. Tx Packet Size Register (PCITPSR)

19.3.3.1 Comm Bus FIFO Transmit Interface

Table 19-18. PCICAR Field Descriptions (Continued)

19.3.3.1.2 Tx Start Address Register (PCITSAR)

Table 19-19. PCITPSR Field Descriptions

19.3.3.1.3 Tx Transaction Control Register (PCITTCR)

Figure 19-22. Tx Transaction Control Register (PCITTCR) Table 19-21. PCITTCR Field Descriptions

19.3.3.1.4 Tx Enables Register (PCITER)

Figure 19-23. Tx Enables Register (PCITER) Table 19-22. PCITER Field Descriptions

19.3.3.1.5 Tx Next Address Register (PCITNAR)

Figure 19-24. Tx Next Address Register (PCITNAR)

Table 19-22. PCITER Field Descriptions (Continued)

19.3.3.1.6 Tx Last Word Register (PCITLWR)

19.3.3.1.7 Tx Done Counts Register (PCITDCR)

Figure 19-26. Tx Done Counts Register (PCITDCR)

Table 19-23. PCITNAR Field Descriptions

Figure 19-25. Tx Last Word Register (PCITLWR) Table 19-24. PCITLWR Field Descriptions

19.3.3.1.8 Tx Status Register (PCITSR)

Table 19-25. PCITDCR Field Descriptions

Figure 19-27. Tx Status Register (PCITSR) Table 19-26. PCITSR Field Descriptions

Table 19-26. PCITSR Field Descriptions (Continued)

19.3.3.1.9 Tx FIFO Data Register (PCITFDR)

19.3.3.1.10 Tx FIFO Status Register (PCITFSR)

Figure 19-29. Tx FIFO Status Register (PCITFSR)

Figure 19-28. Tx FIFO Data Register (PCITFDR) Table 19-27. PCITFDR Field Descriptions

19.3.3.1.11 Tx FIFO Control Register (PCITFCR)

Table 19-28. PCITFSR Field Descriptions

Figure 19-30. Tx FIFO Control Register (PCITFCR)

19.3.3.1.12 Tx FIFO Alarm Register (PCITFAR)

Table 19-29. PCITFCR Field Descriptions

Figure 19-31. Tx FIFO Alarm Register (PCITFAR)

19.3.3.1.13 Tx FIFO Read Pointer Register (PCITFRPR)

Table 19-30. PCITFAR Field Descriptions

Figure 19-32. Tx FIFO Read Pointer Register (PCITFRPR) Table 19-31. PCITFRPR Field Descriptions

19.3.3.1.14 Tx FIFO Write Pointer Register (PCITFWPR)

This marks the end of the PCI Comm Bus FIFO Transmit Interface description.

19.3.3.2 Comm Bus FIFO Receive Interface

Figure 19-33. Tx FIFO Write Pointer Register (PCITFWPR) Table 19-32. PCITFWPR Field Descriptions

19.3.3.2.1 Rx Packet Size Register (PCIRPSR)

19.3.3.2.2 Rx Start Address Register (PCIRSAR)

Figure 19-35. Rx Start Address Register (PCIRSAR)

Figure 19-34. Rx Packet Size Register (PCIRPSR) Table 19-33. PCIRPSR Field Descriptions

19.3.3.2.3 Rx Transaction Control Register (PCIRTCR)

Table 19-34. PCIRSAR Field Descriptions

Figure 19-36. Rx Transaction Control Register (PCIRTCR) Table 19-35. PCIRTCR Field Descriptions

19.3.3.2.4 Rx Enables Register (PCIRER)

Figure 19-37. Rx Enables Register (PCIRER)

Table 19-35. PCIRTCR Field Descriptions (Continued)

Table 19-36. PCIRER Field Descriptions

19.3.3.2.5 Rx Next Address Register (PCIRNAR)

Figure 19-38. Rx Next Address Register (PCIRNAR) Table 19-37. PCIRNAR Field Descriptions

Table 19-36. PCIRER Field Descriptions (Continued)

19.3.3.2.6 Rx Done Counts Register (PCIRDCR)

Figure 19-39. Rx Done Counts Register (PCIRDCR) Table 19-38. PCIRDCR Field Descriptions

19.3.3.2.7 Rx Status Register (PCIRSR)

Figure 19-40. Rx Status Register (PCIRSR) Table 19-39. PCIRSR Field Descriptions

Figure 19-41. Rx FIFO Data Register (PCIRFDR) Table 19-40. PCIRFDR Field Description

Table 19-39. PCIRSR Field Descriptions (Continued)

19.3.3.2.9 Rx FIFO Status Register (PCIRFSR)

Figure 19-42. Rx FIFO Status Register (PCIRFSR) Table 19-41. PCIRFSR Field Descriptions

19.3.3.2.10 Rx FIFO Control Register (PCIRFCR)

Figure 19-43. Rx FIFO Control Register (PCIRFCR) Table 19-42. PCIRFCR Field Descriptions

Table 19-41. PCIRFSR Field Descriptions (Continued)

19.3.3.2.11 Rx FIFO Alarm Register (PCIRFAR)

Figure 19-44. Rx FIFO Alarm Register (PCIRFAR) Table 19-43. PCIRFAR Field Descriptions

Table 19-42. PCIRFCR Field Descriptions (Continued)

19.3.3.2.12 Rx FIFO Read Pointer Register (PCIRFRPR)

19.3.3.2.13 Rx FIFO Write Pointer Register (PCIRFWPR)

Figure 19-46. Rx FIFO Write Pointer Register (PCIRFWPR)

Figure 19-45. Rx FIFO Read Pointer Register (PCIRFRPR) Table 19-44. PCIRFRPR Field Descriptions

19.4 Functional Description

19.4.1 PCI Bus Protocol

19.4.1.1 PCI Bus Background

19.4.1.2 Basic Transfer Control

19.4.1.3 PCI Transactions

Page

Figure 19-48. PCI Write Terminated by Target

19.4.1.4 PCI Bus Commands

Table 19-47. PCI Bus Commands

19.4.1.5 Addressing

Page

Page

19.4.2 Initiator Arbitration

.

19.4.2.1 Priority Scheme

19.4.3 Configuration Interface

19.4.4 XL Bus Initiator Interface

Page

19.4.4.1 Endian Translation

Table 19-49. XL Bus to PCI Byte Lanes for Memory1 Transactions

Table 19-49. XL Bus to PCI Byte Lanes for Memory1 Transactions (Continued)

19.4.4.2 Configuration Mechanism

Page

19.4.4.3 Interrupt Acknowledge Transactions

19.4.4.4 Special Cycle Transactions

19.4.4.5 Transaction Termination

19.4.5 XL Bus Target Interface

19.4.5.1 Reads from Local Memory

19.4.5.2 Local Memory Writes

19.4.5.3 Data Translation

Table 19-53. Aligned PCI to XL Bus Transfers

Table 19-54. Non-Contiguous PCI to XL Bus Transfers (Requires Two XL Bus Accesses)

19.4.5.4 Target Abort

19.4.5.5 Latrule Disable

19.4.6 Communication Subsystem Initiator Interface

19.4.6.1 Access Width

19.4.6.2 Addressing

19.4.6.3 Data Translation

19.4.6.4 Initialization

19.4.6.5 Restart and Reset

19.4.6.6 PCI Commands

19.4.6.7 FIFO Considerations

19.4.6.8 Alarms

19.4.6.9 Bus Errors

19.4.7 PCI Clock Scheme

19.5 Application Information

19.5.1 XL Bus-Initiated Transaction Mapping

19.5.2 Address Maps

Table 19-57. Transaction Mapping: XL Bus PCI

19.5.2.1 Address Translation

Figure 19-54. Inbound Address Map

Figure 19-55. Outbound Address Map

Table 19-58. Address Register Accessibility

19.6 XL Bus Arbitration Priority

Page

Chapter 20 PCI Bus Arbiter Module

20.1 Introduction

20.1.1 Block Diagram

Figure 20-1. PCI Arbiter Interface Diagram

20.1.2 Overview

20.2 External Signal Description

20.2.1 Frame (PCIFRM)

20.2.2 Initiator Ready (PCIIRDY)

20.2.3 PCI Clock (CLKIN)

20.2.4 External Bus Grant (PCIBG[4:1])

20.3 Register Definition

20.3.1 PCI Arbiter Control Register (PACR)

Table 20-2. PACR Field Descriptions

20.3.2 PCI Arbiter Status Register (PASR)

20.4 Functional Description

20.4.1 External PCI Requests

Figure 20-3. PCI Arbiter Status Register (PASR) Table 20-3. PASR Field Descriptions

20.4.2 Arbitration

20.4.2.1 Hidden Bus Arbitration

20.4.2.2 Arbitration Scheme

20.4.2.3 Arbitration Latency

20.4.2.4 Arbitration Examples

Page

20.4.3 Master Time-Out

20.5 Reset

20.6 Interrupts

Chapter 21 FlexCAN

21.1 Introduction

21.1.1 Block Diagram

21.1.2 The CAN System

A typical CAN system is shown below in Figure 21-3.

21.1.3 Features

21.1.4 Modes of Operation

21.1.4.1 Normal Mode

21.1.4.2 Freeze Mode

21.1.4.3 Module Disabled Mode

21.1.4.4 Loop-Back Mode

21.1.4.5 Listen-Only Mode

21.2 External Signals

21.2.1 CANTX[1:0]

21.2.2 CANRX[1:0]

21.3 Memory Map/Register Definition

21.3.1 FlexCAN Memory Map

21.3.2 Register Descriptions

21.3.2.1 FlexCAN Module Configuration Register (CANMCR)

Table 21-2. CANMCR Field Descriptions

21.3.2.2 FlexCAN Control Register (CANCTRL)

Figure 21-5. FlexCAN Control Register (CANCTRL)

Table 21-2. CANMCR Field Descriptions (Continued)

Table 21-3. CANCTRL Field Descriptions

21.3.2.3 FlexCAN Timer Register (TIMER)

Table 21-3. CANCTRL Field Descriptions (Continued)

21.3.2.4 Rx Mask Registers

Figure 21-7. FlexCAN Rx Global Mask Register (RXGMASK) Table 21-5. RXGMASK Field Descriptions

Table 21-4. Mask Examples for Normal/Extended Messages (Continued)

Page

21.3.2.5 FlexCAN Error Counter Register (ERRCNT)

21.3.2.6 FlexCAN Error and Status Register (ERRSTAT)

Table 21-8 describes the ERRSTAT fields.

Figure 21-11. FlexCAN Error and Status Register (ERRSTAT) Table 21-8. ERRSTAT Field Descriptions

21.3.2.7 Interrupt Mask Register (IMASK)

Table 21-8. ERRSTAT Field Descriptions (Continued)

Table 21-10 describes the IMASK fields.

21.3.2.8 Interrupt Flag Register (IFLAG)

Table 21-11. FlexCAN Interrupt Flags Register (IFLAG)

Table 21-12 describes the IFLAG fields.

Table 21-9. FlexCAN Interrupt Mask Register (IMASK) Table 21-10. IMASK Field Descriptions

21.4 Functional Overview

21.4.1 Message Buffer Structure

Page

Table 21-14. Message Buffer Codes for Rx Buffers

Table 21-13. Message Buffer Field Descriptions (Continued)

21.4.2 Message Buffer Memory Map

Table 21-15. Message Buffer Code for Tx Buffers

21.4.3 Transmit Process

21.4.4 Arbitration Process

21.4.5 Receive Process

21.4.5.1 Self-Received Frames

21.4.6 Message Buffer Handling

21.4.6.1 Serial Message Buffers (SMBs)

21.4.6.2 Transmit Message Buffer Deactivation

21.4.6.3 Receive Message Buffer Deactivation

21.4.6.4 Locking and Releasing Message Buffers

21.4.7 CAN Protocol Related Frames

21.4.7.1 Remote Frames

21.4.7.2 Overload Frames

21.4.8 Time Stamp

21.4.9 Bit Timing

21.4.9.1 Configuring the FlexCAN Bit Timing

21.4.10 FlexCAN Error Counters

21.5 FlexCAN Initialization Sequence

21.5.1 Interrupts

Page

Chapter 22 Integrated Security Engine (SEC)

22.1 Features

22.2 ColdFire Security Architecture

22.3 Block Diagram

22.4 Overview

22.4.1 Bus Interface

22.4.2 SEC Controller Unit

22.4.2.1 Static EU Access

22.4.2.2 Dynamic EU Access

22.4.3 Crypto-Channels

22.4.4 Execution Units (EUs)

22.4.4.1 Data Encryption Standard Execution Unit (DEU)

22.4.4.2 Arc Four Execution Unit (AFEU)

22.4.4.3 Advanced Encryption Standard Execution Unit (AESU)

22.4.4.4 Message Digest Execution Unit (MDEU)

Page

22.4.4.5 Random Number Generator (RNG)

22.5 Memory Map/Register Definition

Table 22-3. SEC Register Map (Continued)

22.6 Controller

22.6.1 EU Access

22.6.2 Multiple EU Assignment

22.6.3 Multiple Channels

22.6.4 Controller Registers

22.6.4.1 EU Assignment Control Registers (EUACRH and EUACRL)

Table 22-4 describes the EUACRH and EUACRL fields.

Figure 22-7. EU Assignment Control Register High (EUACRH)

Table 22-5. Channel Assignment Value

22.6.4.2 EU Assignment Status Registers (EUASRH and EUASRL)

Figure 22-10. EU Assignment Status Register Low (EUASRL)

Figure 22-9. EU Assignment Status Register High (EUASRH)

Table 22-5. Channel Assignment Value (Continued)

22.6.4.3 SEC Interrupt Mask Registers (SIMRH and SIMRL)

22.6.4.4 SEC Interrupt Status Registers (SISRH and SISRL)

22.6.4.5 SEC Interrupt Control Registers (SICRH and SICRL)

Page

22.6.4.6 SEC ID Register (SIDR)

22.6.4.7 SEC Master Control Register (SMCR)

Figure 22-13. ID Register (SIDR)

Figure 22-14. SEC Master Control Register (SMCR) Table 22-9. SMCR Field Descriptions

22.6.4.8 Master Error Address Register (MEAR)

22.7 Channels

22.7.1 Crypto-Channel Registers

22.7.1.1 Crypto-Channel Configuration Registers (CCCRn)

Figure 22-16. Crypto-Channel Configuration Register (CCCRn) Table 22-11. CCCRn Field Descriptions

Table 22-12 defines the burst size according to the value displayed in the BURST_SIZE field.

22.7.1.2 Crypto-Channel Pointer Status Registers (CCPSRHn and CCPSRLn)

Table 22-12. Burst Size Definition

Table 22-11. CCCRn Field Descriptions (Continued)

Figure 22-18. Crypto-Channel Pointer Status Register Low (CCPSRLn)

Table 22-14. CCPSRLn Field Descriptions

Table 22-14. CCPSRLn Field Descriptions (Continued)

Table 22-15 shows the values of crypto-channel states.

Table 22-15. STATE Field Values

Table 22-14. CCPSRLn Field Descriptions (Continued)

Table 22-15. STATE Field Values (Continued)

22.7.1.3 Crypto-Channel Current Descriptor Pointer Register (CDPRn)

22.7.1.4 Fetch Register (FRn)

22.7.1.5 Data Packet Descriptor Buffer (CDBUFn)

22.8 ARC Four Execution Unit (AFEU)

22.8.1 AFEU Register Map

22.8.2 AFEU Reset Control Register (AFRCR)

Figure 22-21. AFEU Reset Control Register (AFRCR)

Table 22-18 describes AFEU reset control register fields.

22.8.3 AFEU Status Register (AFSR)

Table 22-18. AFRCR Field Descriptions

Figure 22-22. AFEU Status Register (AFSR)

Table 22-19 describes AFEU status register fields.

Table 22-19. AFSR Field Descriptions

22.8.4 AFEU Interrupt Status Register (AFISR)

Table 22-20 describes AFEU interrupt status register fields.

Figure 22-23. AFEU Interrupt Status Register (AFISR)

Table 22-20. AFISR Field Descriptions

Table 22-19. AFSR Field Descriptions (Continued)

22.8.5 AFEU Interrupt Mask Register (AFIMR)

Table 22-20. AFISR Field Descriptions (Continued)

Figure 22-24. AFEU Interrupt Mask Register (AFIMR)

Table 22-21 describes AFEU interrupt mask register fields.

Table 22-21. AFIMR Field Descriptions

22.9 Data Encryption Standard Execution Units (DEU)

22.9.1 DEU Register Map

22.9.2 DEU Reset Control Register (DRCR)

Figure 22-25. DEU Reset Control Register (DRCR)

Table 22-22 describes DEU reset control register fields.

22.9.3 DEU Status Register (DSR)

Table 22-22. DRCR Field Descriptions

Figure 22-26. DEU Status Register (DSR)

Table 22-23 describes the DEU status registers bit settings.

Table 22-23. DSR Field Descriptions

22.9.4 DEU Interrupt Status Register (DISR)

Table 22-24 describes DEU interrupt register signals.

Figure 22-27. DEU Interrupt Status Register (DISR)

Table 22-24. DISR Field Descriptions

Table 22-23. DSR Field Descriptions (Continued)

Table 22-24. DISR Field Descriptions (Continued)

22.9.5 DEU Interrupt Mask Register (DIMR)

Figure 22-28. DEU Interrupt Mask Register (DIMR)

Table 22-25. DIMR Field Descriptions

22.10 Message Digest Execution Unit (MDEU)

22.10.1 MDEU Register Map

22.10.2 MDEU Reset Control Register (MDRCR)

Figure 22-29. MDEU Reset Control Register (MDRCR)

Table 22-26 describes MDEU reset control register fields.

22.10.3 MDEU Status Register (MDSR)

Table 22-26. MDEURCR Field Descriptions

Table 22-27 describes MDEU status register fields.

Table 22-27. MDSR Field Descriptions

22.10.4 MDEU Interrupt Status Register (MDISR)

Table 22-28 describes MDEU interrupt status register fields.

Figure 22-31. MDEU Interrupt Status Register (MDISR)

Table 22-28. MDISR Field Descriptions

Table 22-27. MDSR Field Descriptions (Continued)

22.10.5 MDEU Interrupt Mask Register (MDIMR)

Table 22-28. MDISR Field Descriptions (Continued)

Figure 22-32. MDEU Interrupt Mask Register (MDIMR)

Table 22-28 describes MDEU interrupt mask register fields.

Table 22-29. MDIMR Field Descriptions

22.11 RNG Execution Unit (RNG)

22.11.1 RNG Register Map

22.11.2 RNG Reset Control Register (RNGRCR)

22.11.3 RNG Status Register (RNGSR)

Figure 22-34. RNG Status Register (RNGSR)

Table 22-31 describes RNG status register fields.

Table 22-30. RNGRCR Field Descriptions

22.11.4 RNG Interrupt Status Register (RNGISR)

Figure 22-35. RNG Interrupt Status Register (RNGISR)

Table 22-31. RNGSR Field Descriptions

Table 22-32 describes RNG interrupt status register fields.

22.11.5 RNG Interrupt Mask Register (RNGIMR)

Table 22-33 describes RNG interrupt status register fields.

Table 22-32. RNGISR Field Descriptions

22.12 Advanced Encryption Standard Execution Units (AESU)

22.12.1 AESU Register Map

22.12.2 AESU Reset Control Register (AESRCR)

Figure 22-36. AESU Reset Control Register (AESRCR)

Table 22-34 describes AESU reset control register fields.

22.12.3 AESU Status Register (AESSR)

Table 22-34. AESRCR Field Descriptions

Figure 22-37. AESU Status Register (AESSR)

Table 22-35 describes AESU status register fields.

Table 22-35. AESSR Field Descriptions

22.12.4 AESU Interrupt Status Register (AESISR)

Table 22-36 describes AESU interrupt register fields.

Figure 22-38. AESU Interrupt Status Register (AESISR)

Table 22-36. AESISR Field Descriptions

Table 22-35. AESSR Field Descriptions (Continued)

22.12.5 AESU Interrupt Mask Register (AESIMR)

Table 22-36. AESISR Field Descriptions (Continued)

Figure 22-39. AESU Interrupt Mask Register (AESIMR)

Table 22-37 describes the AESU interrupt mask register fields.

Table 22-37. AESIMR Field Descriptions

22.13 Descriptors

22.13.1 Descriptor Structure

Figure 22-40. Data Packet Descriptor Format

22.13.1.1 Descriptor Header

Figure 22-41. Descriptor Header

Table 22-38 defines the header bits.

Page

Table 22-39. Descriptor Types

Table 22-38. Header Bit Definitions (Continued)

22.13.1.2 Descriptor Length and Pointer Fields

22.13.1.3 Null Fields

22.13.1.4 Next Descriptor Pointer

22.13.2 Descriptor Chaining

22-62 Freescale Semiconductor

Figure 22-45. Chain of Descriptors

22.13.3 Descriptor Type Formats

Table 22-43. Descriptor Types

Some of the inputs and outputs will be optional depending on the exact usage of the descriptor.

Table 22-44. Descriptor Length/Pointer Mapping

Table 22-43. Descriptor Types (Continued)

22.13.4 Descriptor Classes

22.13.4.1 Dynamic Descriptors

22.13.4.2 Static Descriptors

Page

22.14 EU Specific Data Packet Descriptors

22.14.1 AFEU Mode Options and Data Packet Descriptors

22.14.1.1 Dynamically Assigned AFEU

Table 22-49. AFEU Mode Register Field Descriptions

Table 22-50. Descriptor for a Dynamically Assigned AFEU Using a Key

22.14.1.2 Statically Assigned AFEU

Table 22-51. Descriptor for a Dynamically Assigned AFEU Using Context

Table 22-52. First Descriptor for a Statically Assigned AFEU Using a Key

Table 22-50. Descriptor for a Dynamically Assigned AFEU Using a Key (Continued)

Table 22-53 shows the descriptor format to load a previously generated context into the AFEU.

Table 22-53. First Descriptor for a Statically Assigned AFEU Using a Context

Table 22-52. First Descriptor for a Statically Assigned AFEU Using a Key (Continued)

Table 22-54. Middle Descriptor for a Statically Assigned AFEU

Table 22-55. Final Descriptor for a Statically Assigned AFEU

Table 22-53. First Descriptor for a Statically Assigned AFEU Using a Context (Continued)

22.14.2 DEU Mode Options and Data Packet Descriptors

Table 22-56 describes DEU mode register fields.

Figure 22-47. DEU Mode Options Table 22-56. DEU Mode Option Field Descriptions

Table 22-55. Final Descriptor for a Statically Assigned AFEU (Continued)

22.14.2.1 Dynamically Assigned DEU

Table 22-58 lists several different descriptors that use the format shown in Table 22-57.

Table 22-57. Descriptor for a Dynamically Assigned DEU

Table 22-58. Typical Header Values for Dynamic DEU Descriptor Format

22.14.2.2 Statically Assigned DEU

Table 22-62 lists the specific descriptors that use the format shown in Table 22-61.

Table 22-61. Middle Descriptor for a Statically Assigned DEU

Table 22-62. Typical Header Values for Middle Static DEU Descriptor Format

Table 22-60. Typical Header Values for First Static DEU Descriptor Format (Continued)

Table 22-64 lists the specific descriptors that use the format shown in Table 22-63.

Table 22-63. Final Descriptor for a Statically Assigned DEU

Table 22-64. Typical Header Values Final Static DEU Descriptor Format

Table 22-62. Typical Header Values for Middle Static DEU Descriptor Format (Continued)

22.14.3 MDEU Mode Options and Data Packet Descriptors

Table 22-65 describes MDEU mode option fields.

Figure 22-48. MDEU Mode Options Table 22-65. MDEU Mode Option Field Descriptions

Table 22-64. Typical Header Values Final Static DEU Descriptor Format (Continued)

22.14.3.1 Recommended Settings for MDEU Mode Register

22.14.3.2 Dynamically Assigned MDEU

Table 22-68 lists several different descriptors that use the format shown in Table 22-67.

Table 22-69 shows the first descriptor for a statically assigned MDEU.

22.14.3.3 Statically Assigned MDEU

Table 22-67. Descriptor for a Dynamically Assigned MDEU

Table 22-68. Typical Header Values for Dynamic MDEU Format

Table 22-70 lists several different descriptors that use the format shown in Table 22-69.

Table 22-71 shows the middle descriptor for a statically assigned MDEU.

Table 22-69. First Descriptor for a Statically Assigned MDEU

Table 22-70. Typical Header Values for Using First Static MDEU Descriptor Format

Table 22-71. Middle Descriptor for a Statically Assigned MDEU

Table 22-73 shows the final descriptor for a statically assigned MDEU.

Table 22-72. Typical Header Values for Using Middle Static MDEU Descriptor Format

Table 22-73. Final Descriptor for a Statically Assigned MDEU

Table 22-71. Middle Descriptor for a Statically Assigned MDEU (Continued)

22.14.4 RNG Data Packet Descriptors

22.14.5 AESU Mode Options and Data Packet Descriptors

Table 22-76 describes AESU mode register fields.

Figure 22-49. AESU Mode Options Table 22-76. AESU Mode Register Field Descriptions

Table 22-75. RNG Descriptor Format (Continued)

22.14.5.1 Dynamically Assigned AESU

Table 22-77. Descriptor for a Dynamically Assigned AESU

Table 22-76. AESU Mode Register Field Descriptions (Continued)

Table 22-78 lists several different descriptors that use the format shown in Table 22-77.

22.14.5.2 Statically Assigned AESU

Table 22-69 shows the first descriptor for a statically assigned AESU.

Table 22-78. Typical Header Values for Dynamic AESU Format

Table 22-79. First Descriptor for a Statically Assigned AESU

Table 22-77. Descriptor for a Dynamically Assigned AESU (Continued)

Table 22-80 lists several different descriptors that use the format shown in Table 22-79.

Table 22-81 shows the middle descriptor for a statically assigned AESU.

Table 22-80. Typical Header Values for Using First Static AESU Descriptor Format

Table 22-81. Middle Descriptor for a Statically Assigned AESU

Table 22-79. First Descriptor for a Statically Assigned AESU (Continued)

Table 22-83 shows the final descriptor for a statically assigned AESU.

Table 22-82. Typical Header Values for Using Middle Static AESU Descriptor Format

Table 22-83. Final Descriptor for a Statically Assigned AESU

Table 22-84. Typical Header Values for Using Final Static AESU Descriptor Format

22.14.5.3 AESU-CCM Mode Descriptor

Table 22-87 shows the format used for the context output for AES-CCM.

Table 22-86. AES-CCM Encryption Context Input Format

Table 22-87. AES-CCM Encryption Context Output Format

Table 22-88. Descriptor for a AES-CCM Decryption

Table 22-89 shows the format used for the context input for AES-CCM.

22.14.6 Multi-Function Data Packet Descriptors

Table 22-89. AES-CCM Decryption Context Input Format

Table 22-90. AES-CCM Decryption Context Output Format

Table 22-88. Descriptor for a AES-CCM Decryption (Continued)

22.14.6.1 Snooping

22.14.6.2 Dynamic Multi-Function Descriptor Formats

Page

Page

Table 22-95 lists typical DEU/HMAC multi-function descriptor header values.

Table 22-94. Descriptor for Dynamic Multi-Function Encryption

Table 22-95. Typical Header Values for Dynamic Multi-Function DEU Descriptors

22.14.6.3 Static Multi-Function Descriptor Formats

Table 22-98 lists typical DEU/HMAC multi-function descriptor header values for the first descriptor.

Table 22-97. First Descriptor for Static Multi-Function Encryption/Decryption

Table 22-98. Typical Header Values for First Static Multi-Function DEU Descriptors

Table 22-99 lists typical AESU/HMAC multi-function descriptor header values.

Table 22-99. Typical Header Values for Dynamic Multi-Function AESU Descriptors

Table 22-98. Typical Header Values for First Static Multi-Function DEU Descriptors (Continued)

Page

Table 22-102 lists typical AESU/HMAC multi-function descriptor header values.

Table 22-102. Typical Header Values for Middle Static Multi-Function AESU Descriptors

Table 22-101. Typical Header Values for Middle Static Multi-Function DEU Descriptors (Continued)

Page

Table 22-104. Typical Header Values for Final Static Multi-Function DEU Descriptors

Table 22-103. Final Descriptor for Multi-Function Encrytion/Decryption (Continued)

22.14.6.4 SSLv3.1/TLS 1.0 Processing Descriptors

Page

Page

Page

Page

Freescale Semiconductor 23-1

Chapter 23 IEEE 1149.1 Test Access Port (JTAG)

to Debug Module

4-BIT TAP INSTRUCTION REGISTER

23.1 Introduction

Figure 23-1. JTAG Block Diagram

23.2 External Signal Description

23.2.1 Detailed Signal Description

23.2.1.1 Test Mode 0 (MTMOD0)

23.2.1.2 Test Clock Input (TCK)

23.2.1.3 Test Mode Select/Breakpoint (TMS/BKPT)

23.2.1.4 Test Data Input/Development Serial Input (TDI/DSI)

23.2.1.5 Test Reset/Development Serial Clock (TRST/DSCLK)

23.2.1.6 Test Data Output/Development Serial Output (TDO/DSO)

23.3 Memory Map/Register Definition

23.3.1 Memory Map

23.3.2 Register Descriptions

23.3.2.1 Instruction Shift Register (IR)

23.3.2.2 IDCODE Register

23.3.2.3 Bypass Register

23.3.2.4 JTAG_CFM_CLKDIV Register

23.3.2.5 TEST_CTRL Register

23.3.2.6 Boundary Scan Register

23.4 Functional Description

23.4.1 JTAG Module

23.4.2 TAP Controller

Figure 23-3. TAP Controller State Machine Flow

23.4.3 JTAG Instructions

Table 23-5 describes public and private instructions.

23.4.3.1 External Test Instruction (EXTEST)

23.4.3.2 IDCODE Instruction

23.4.3.3 SAMPLE/PRELOAD Instruction

23.4.3.4 ENABLE_TEST_CTRL Instruction

23.4.3.5 HIGHZ Instruction

23.5 Initialization/Application Information

23.5.1 Restrictions

23.5.2 Nonscan Chain Operation

Page

Part IV Communications Subsystem

Page

Chapter 24 Multichannel DMA

24.1 Introduction

24.1.1 Block Diagram

24.1.2 Overview

24.1.2.1 Master DMA Engine (MDE)

24.1.2.2 Address and Data Sequencer (ADS)

24.1.2.3 Priority-Task Decoder (PTD)

24.1.2.4 Logic Unit with Redundancy Check (LURC)

24.2 External Signals

24.2.1 DREQ[1:0]

24.2.2 DACK[1:0]

24.3 Memory Map/Register Definitions

24.3.1 DMA Task Memory

24.3.2 Memory Structure

Figure 24-2. DMA Programmer-Maintained Memory Model

24.3.3 DMA Registers

24.3.3.1 DMA Register Map

Table 24-1 shows the memory map of the DMA module.

Table 24-1. DMA Memory Map

24.3.3.2 Task Base Address Register (TaskBAR)

Note that there is a 512-byte alignment restriction on the TaskBAR.

Table 24-1. DMA Memory Map (Continued)

24.3.3.3 Current Pointer (CP)

Figure 24-3. Task Base Address Register (TaskBAR) Table 24-2. TaskBAR Field Descriptions

Figure 24-4. Current Pointer Register (CP) Table 24-3. CP Field Descriptions

24.3.3.4 End Pointer (EP)

24.3.3.5 Variable Pointer (VP)

Figure 24-5. End Pointer Register (EP) Table 24-4. EP Field Descriptions

Figure 24-6. Variable Pointer Register (VP) Table 24-5. VP Field Descriptions

24.3.3.6 PTD Control (PTD)

Figure 24-7. PTD Control Register (PTD) Table 24-6. PTD Field Descriptions

24.3.3.7 DMA Interrupt Pending (DIPR)

24.3.3.8 DMA Interrupt Mask Register (DIMR)

Figure 24-9. DMA Interrupt Mask Register (DIMR)

Figure 24-8. DMA Interrupt Pending Register (DIPR) Table 24-7. DIPR Field Descriptions

24.3.3.9 Task Control Registers (TCRn)

Table 24-8. DIMR Field Descriptions

Figure 24-10. Task Control Register (TCRn) Table 24-9. TCRn Field Descriptions

24.3.3.10 Priority Registers (PRIORn)

Figure 24-11. Priority Register

Table 24-9. TCRn Field Descriptions (Continued)

24.3.3.11 Initiator Mux Control Register (IMCR)

Table 24-10. PRIOR Field Descriptions

Figure 24-12. Initiator Mux Control Register (IMCR) Figure 24-13. Initiator Assignments

24.3.3.12 Task Size Registers (TSKSZ[0:1])

Figure 24-13. Initiator Assignments (Continued)

Figure 24-14. Task Size Register 0 (TSKSZ0)

Figure 24-15. Task Size Register 1 (TSKSZ1) Table 24-11. TSKSZ Field Descriptions

24.3.3.13 Debug Comparator Registers (DBGCOMPn)

24.3.3.14 Debug Control (DBGCTL)

Figure 24-17. Debug Control Register (DBGCTL)

Figure 24-16. Debug Comparator Register (DBGCMPn) Table 24-12. Debug Comparator Field Descriptions

Table 24-13. Debug Control Field Descriptions

Table 24-14. Comparator 1 Type Bit Encoding

24.3.3.15 Debug Status (DBGSTAT)

Table 24-15. Comparator 2 Type Bit Encodings

Figure 24-18. Debug Status Register (DBGSTAT) Table 24-16. Debug Status Field Descriptions

24.3.3.16 PTD Debug Registers

Figure 24-19. PTD Debug Register (PTDDBG) Table 24-17. PTD Debug Register Descriptions

Table 24-16. Debug Status Field Descriptions (Continued)

24.3.4 External Request Module Registers

24.3.4.1 External Request Module Register Map

24.3.4.2 External Request Base Address Register (EREQBAR)

24.3.4.3 External Request Address Mask Register (EREQMASK)

Figure 24-22. External Request Control Register (EREQCTRL)

24.3.4.4 External Request Control Register (EREQCTRL)

Figure 24-20. External Request Base Address Register

Figure 24-21. External Request Address Mask Register (EREQMASK)

24.4 Functional Description

24.4.1 Tasks

24.4.2 Descriptors

24.4.3 Task Initialization

24.4.4 Initiators

24.4.5 Prioritization

24.4.6 Context Switch

24.4.7 Data Movement

24.4.8 Data Manipulation

24.4.8.1 LURC Features

24.4.9 Line Buffers

24.4.9.1 Combine Write Enable

24.4.9.2 Read Line Enable

24.4.9.3 Speculative Prefetch

24.4.10 Termination of Loop

24.5 Programming Model

24.5.1 Register Initialization

24.5.2 Task Memory

24.5.2.1 Task Table

Figure 24-23. Task Descriptor Table Format

...................