SPRS292A − OCTOBER 2005 − REVISED NOVEMBER 2005

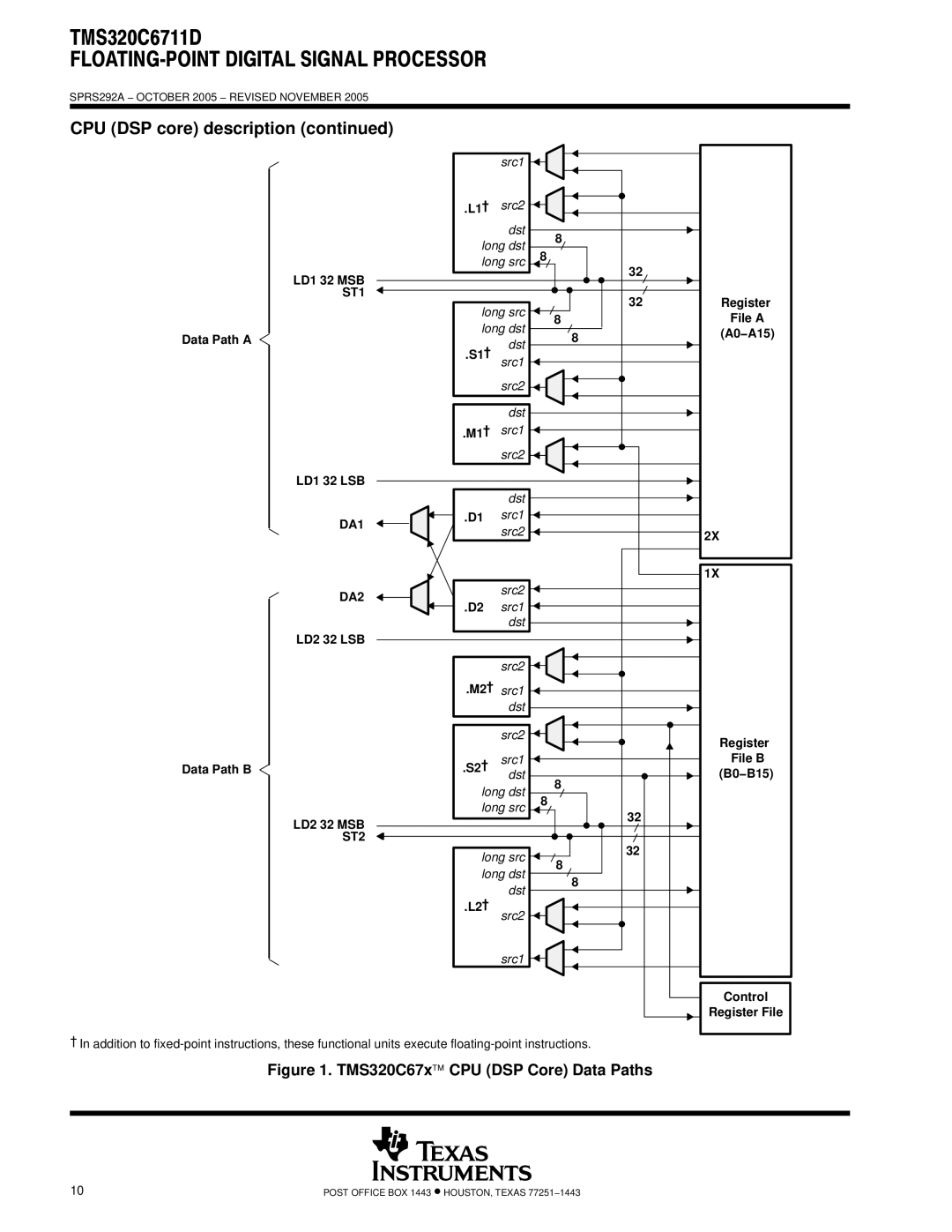

CPU (DSP core) description (continued)

Data Path A

Data Path B

|

| src1 |

|

|

| .L1† | src2 |

|

|

|

| dst | 8 |

|

| long dst |

| ||

| 8 |

| ||

| long src |

| ||

| 32 |

| ||

LD1 32 MSB |

|

|

| |

|

|

|

| |

ST1 |

|

| 32 | Register |

| long src | |||

| 8 | File A | ||

| long dst | |||

| 8 | (A0−A15) | ||

|

| dst | ||

| .S1† |

| ||

|

|

| ||

| src1 |

|

| |

|

|

|

| |

|

| src2 |

|

|

|

| dst |

|

|

| .M1† | src1 |

|

|

|

| src2 |

|

|

LD1 32 LSB |

|

|

|

|

|

| dst |

|

|

DA1 | .D1 | src1 |

|

|

| src2 |

| 2X | |

|

|

| ||

|

|

|

| |

|

|

|

| 1X |

DA2 |

| src2 |

|

|

.D2 | src1 |

|

| |

|

|

| ||

|

| dst |

|

|

LD2 32 LSB |

|

|

|

|

|

| src2 |

|

|

| .M2† | src1 |

|

|

|

| dst |

|

|

|

| src2 |

| Register |

|

|

|

| |

| .S2† | src1 |

| File B |

| dst |

| (B0−B15) | |

|

| 8 | ||

| long dst |

| ||

| 8 |

| ||

| long src |

| ||

| 32 |

| ||

LD2 32 MSB |

|

|

| |

|

|

|

| |

ST2 |

|

| 32 |

|

| long src |

| ||

| 8 |

| ||

| long dst |

| ||

| 8 |

| ||

|

| dst |

| |

| .L2† |

|

| |

| src2 |

|

| |

|

|

|

| |

|

| src1 |

|

|

|

|

|

| Control |

|

|

|

| Register File |

†In addition to

Figure 1. TMS320C67x CPU (DSP Core) Data Paths

10 | POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443 |