SPRS292A − OCTOBER 2005 − REVISED NOVEMBER 2005

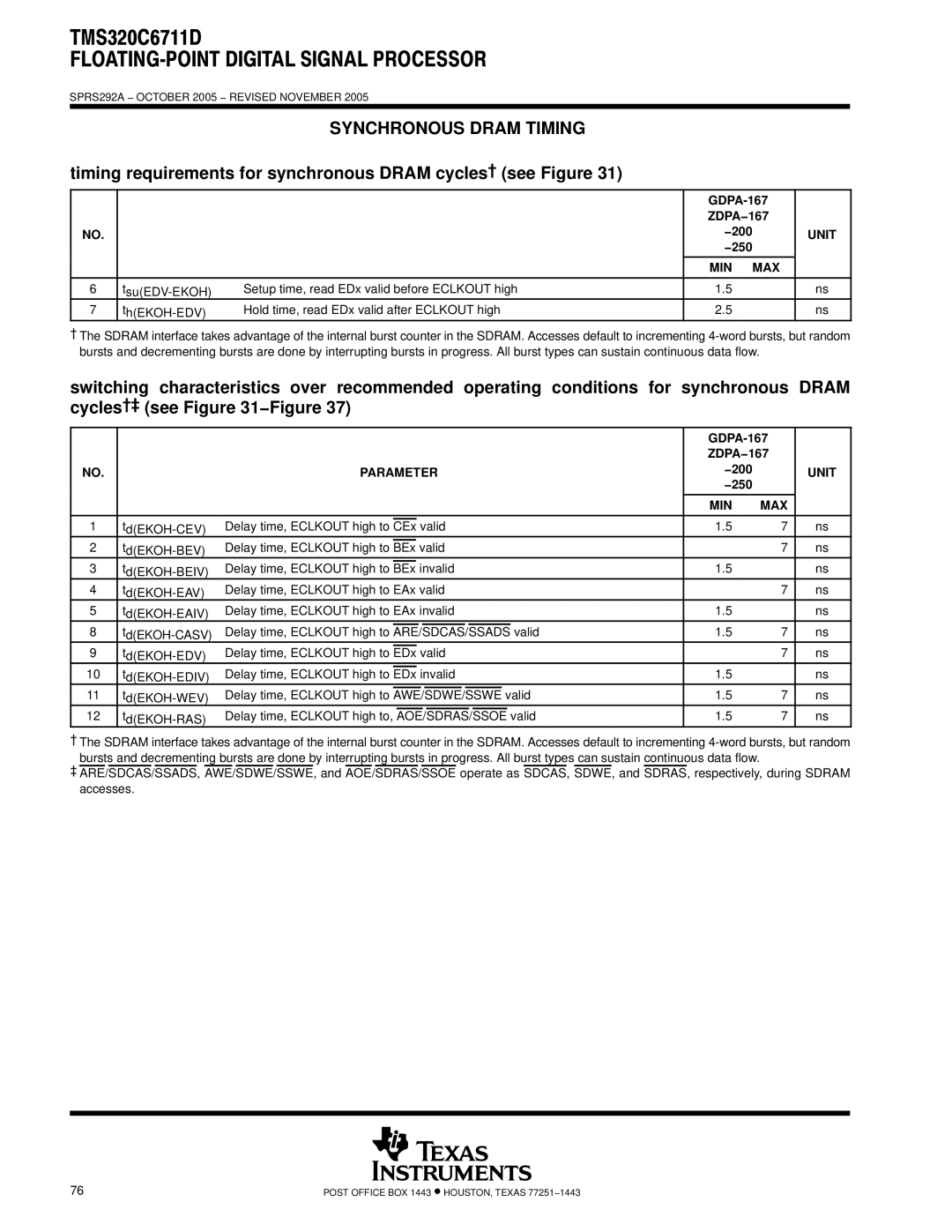

SYNCHRONOUS DRAM TIMING

timing requirements for synchronous DRAM cycles† (see Figure 31)

|

|

|

|

| ||

|

|

| ZDPA−167 |

| ||

NO. |

|

| −200 |

| UNIT | |

|

|

| −250 |

|

| |

|

|

| MIN |

| MAX |

|

|

|

|

|

|

|

|

6 | Setup time, read EDx valid before ECLKOUT high | 1.5 |

|

| ns | |

7 | Hold time, read EDx valid after ECLKOUT high | 2.5 |

|

| ns | |

†The SDRAM interface takes advantage of the internal burst counter in the SDRAM. Accesses default to incrementing

switching characteristics over recommended operating conditions for synchronous DRAM cycles†‡ (see Figure 31−Figure 37)

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ZDPA−167 |

| |

NO. |

| PARAMETER | −200 |

| UNIT | |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| −250 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MIN | MAX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

1 | Delay time, ECLKOUT high to |

|

|

|

|

| valid | 1.5 | 7 | ns | ||||||||||||

CEx |

|

| ||||||||||||||||||||

2 | Delay time, ECLKOUT high to |

|

|

|

|

| valid |

| 7 | ns | ||||||||||||

BEx |

|

|

| |||||||||||||||||||

3 | Delay time, ECLKOUT high to |

|

|

|

|

| invalid | 1.5 |

| ns | ||||||||||||

BEx |

|

|

| |||||||||||||||||||

4 | Delay time, ECLKOUT high to EAx valid |

| 7 | ns | ||||||||||||||||||

5 | Delay time, ECLKOUT high to EAx invalid | 1.5 |

| ns | ||||||||||||||||||

8 | Delay time, ECLKOUT high to |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1.5 | 7 | ns | |

|

|

|

| ARE/SDCAS/SSADS valid | ||||||||||||||||||

9 | Delay time, ECLKOUT high to |

|

|

|

| valid |

| 7 | ns | |||||||||||||

EDx |

| |||||||||||||||||||||

10 | Delay time, ECLKOUT high to |

|

|

|

| invalid | 1.5 |

| ns | |||||||||||||

EDx |

| |||||||||||||||||||||

11 | Delay time, ECLKOUT high to |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1.5 | 7 | ns | |

AWE/SDWE/SSWE valid | ||||||||||||||||||||||

12 | Delay time, ECLKOUT high to, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1.5 | 7 | ns | ||

| AOE/SDRAS/SSOE valid | |||||||||||||||||||||

†The SDRAM interface takes advantage of the internal burst counter in the SDRAM. Accesses default to incrementing

‡ARE/SDCAS/SSADS, AWE/SDWE/SSWE, and AOE/SDRAS/SSOE operate as SDCAS, SDWE, and SDRAS, respectively, during SDRAM accesses.

76 | POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443 |