SPRS292A − OCTOBER 2005 − REVISED NOVEMBER 2005

|

|

|

|

|

|

| HOLD/HOLDA TIMING |

| |||||

timing requirements for the |

|

|

|

|

|

|

|

| (see Figure 38) |

| |||

HOLD/HOLDA cycles† |

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ZDPA−167 |

|

| NO. |

|

|

|

|

|

| −200 | UNIT | ||||

|

|

|

|

|

|

|

|

|

|

|

| −250 |

|

|

|

|

|

|

|

|

|

|

|

|

| MIN MAX |

|

|

|

|

|

|

|

|

| ||||||

| 3 |

| low after |

|

| low |

| E | ns | ||||

| HOLD | HOLDA |

| ||||||||||

| †E = ECLKIN period in ns |

|

|

| |||||||||

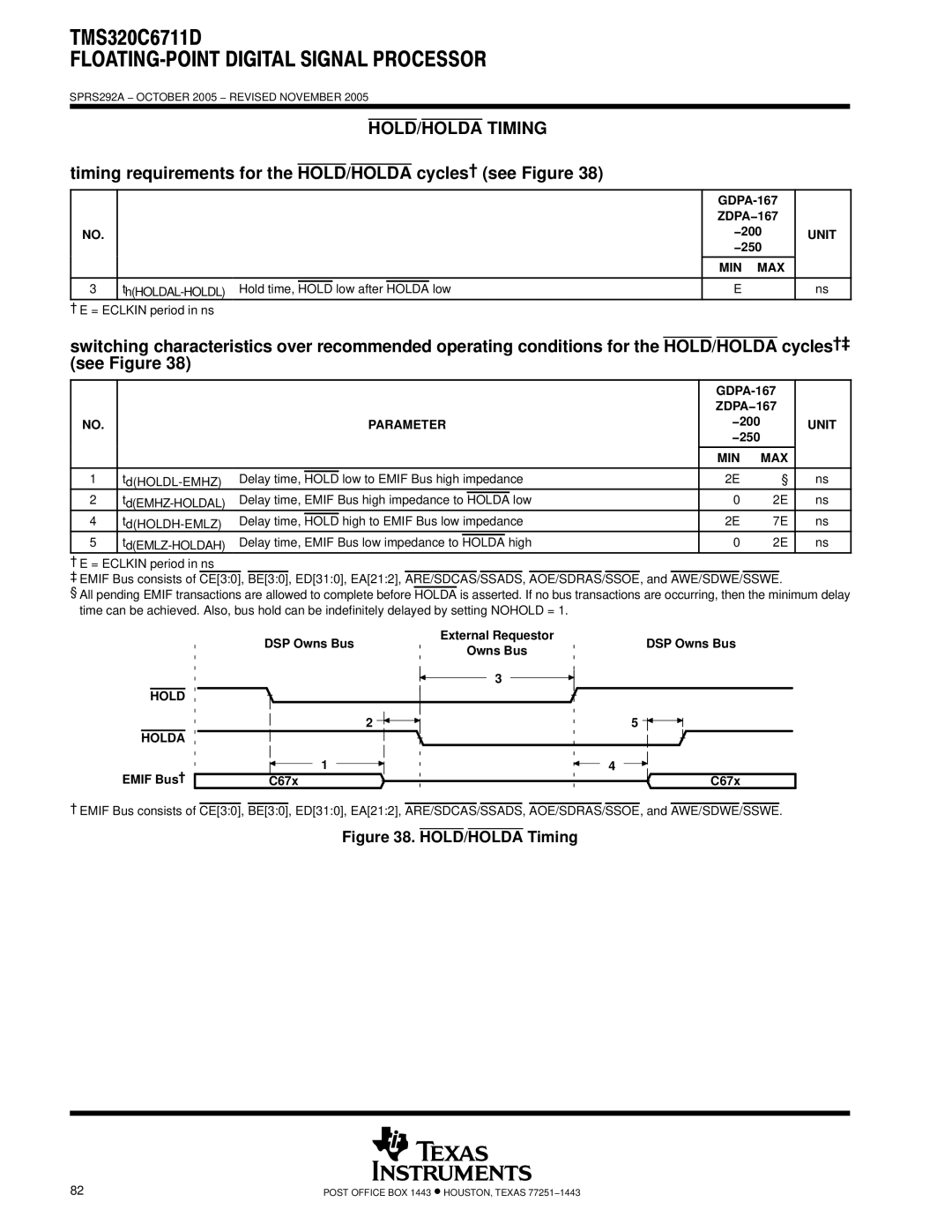

switching characteristics over recommended operating conditions for the HOLD/HOLDA cycles†‡ (see Figure 38)

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| ZDPA−167 |

| |

NO. |

|

|

| PARAMETER | −200 |

| UNIT | ||||

|

|

|

|

|

|

|

|

| −250 |

|

|

|

|

|

|

|

|

|

|

| MIN | MAX |

|

|

|

|

|

|

|

|

|

|

| ||

1 | Delay time, |

| low to EMIF Bus high impedance | 2E | § | ns | |||||

HOLD | |||||||||||

2 | Delay time, EMIF Bus high impedance to |

|

| low | 0 | 2E | ns | ||||

HOLDA | |||||||||||

4 | Delay time, |

| high to EMIF Bus low impedance | 2E | 7E | ns | |||||

HOLD | |||||||||||

5 | Delay time, EMIF Bus low impedance to |

|

| high | 0 | 2E | ns | ||||

HOLDA | |||||||||||

†E = ECLKIN period in ns

‡EMIF Bus consists of CE[3:0], BE[3:0], ED[31:0], EA[21:2], ARE/SDCAS/SSADS, AOE/SDRAS/SSOE, and AWE/SDWE/SSWE.

§All pending EMIF transactions are allowed to complete before HOLDA is asserted. If no bus transactions are occurring, then the minimum delay time can be achieved. Also, bus hold can be indefinitely delayed by setting NOHOLD = 1.

HOLD

HOLDA

EMIF Bus†

DSP Owns Bus | External Requestor | DSP Owns Bus | |

Owns Bus | |||

|

| ||

| 3 |

| |

2 |

| 5 | |

1 |

| 4 | |

C67x |

| C67x |

†EMIF Bus consists of CE[3:0], BE[3:0], ED[31:0], EA[21:2], ARE/SDCAS/SSADS, AOE/SDRAS/SSOE, and AWE/SDWE/SSWE.

Figure 38. HOLD/HOLDA Timing

82 | POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443 |