SPRS292 − OCTOBER 2005

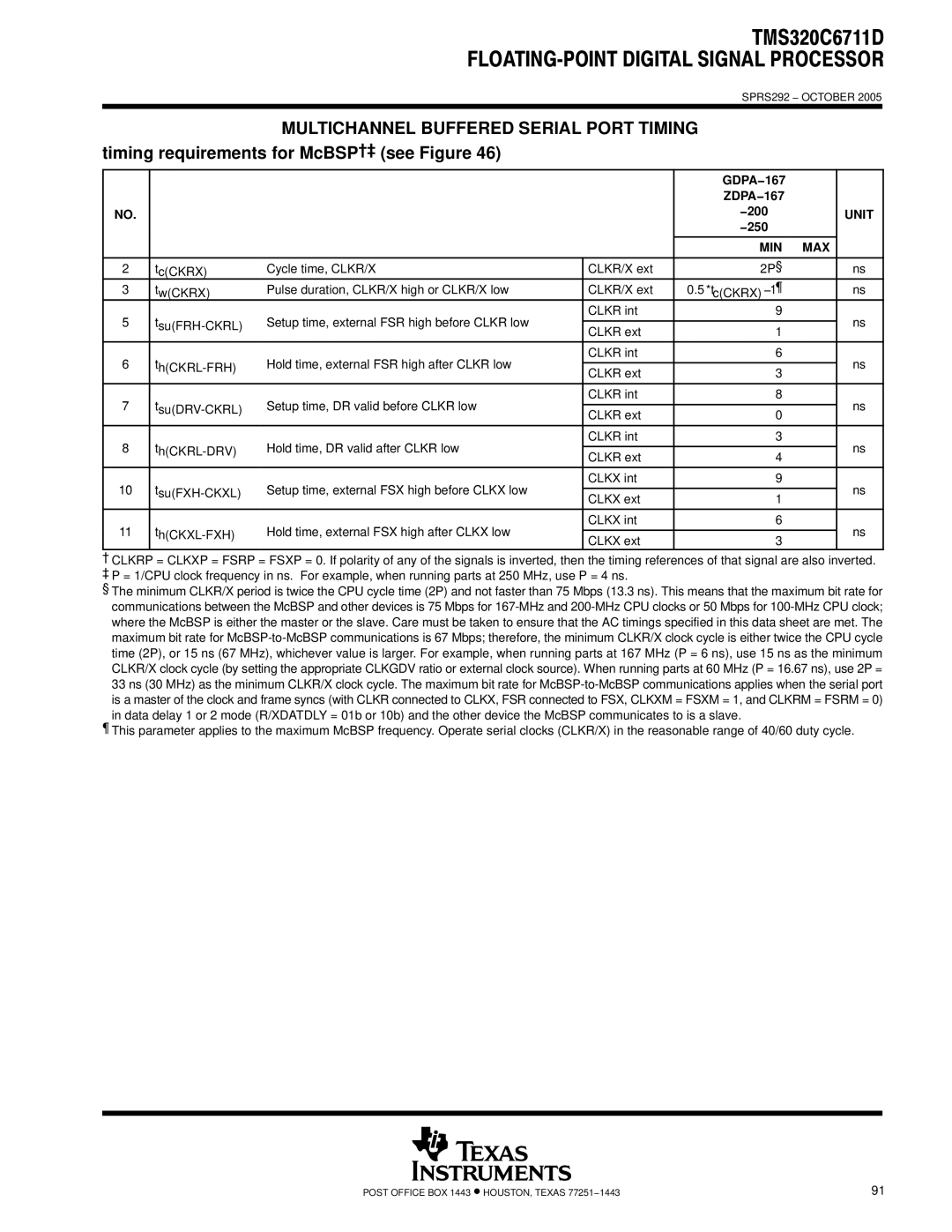

MULTICHANNEL BUFFERED SERIAL PORT TIMING timing requirements for McBSP†‡ (see Figure 46)

|

|

|

|

| GDPA−167 |

|

| |

|

|

|

|

| ZDPA−167 |

|

| |

NO. |

|

|

|

| −200 |

| UNIT | |

|

|

|

|

| −250 |

|

| |

|

|

|

|

| MIN | MAX |

| |

|

|

|

|

|

|

|

| |

2 | tc(CKRX) | Cycle time, CLKR/X | CLKR/X ext |

| 2P§ |

| ns | |

3 | t | Pulse duration, CLKR/X high or CLKR/X low | CLKR/X ext | 0.5 *t |

| −1 ¶ |

| ns |

| w(CKRX) |

|

| c(CKRX) |

|

|

| |

5 | Setup time, external FSR high before CLKR low | CLKR int |

|

| 9 |

| ns | |

|

|

|

|

| ||||

CLKR ext |

|

| 1 |

| ||||

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

6 | Hold time, external FSR high after CLKR low | CLKR int |

|

| 6 |

| ns | |

|

|

|

|

| ||||

CLKR ext |

|

| 3 |

| ||||

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

7 | Setup time, DR valid before CLKR low | CLKR int |

|

| 8 |

| ns | |

|

|

|

|

| ||||

CLKR ext |

|

| 0 |

| ||||

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

8 | Hold time, DR valid after CLKR low | CLKR int |

|

| 3 |

| ns | |

|

|

|

|

| ||||

CLKR ext |

|

| 4 |

| ||||

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

10 | Setup time, external FSX high before CLKX low | CLKX int |

|

| 9 |

| ns | |

|

|

|

|

| ||||

CLKX ext |

|

| 1 |

| ||||

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

11 | Hold time, external FSX high after CLKX low | CLKX int |

|

| 6 |

| ns | |

|

|

|

|

| ||||

CLKX ext |

|

| 3 |

| ||||

|

|

|

|

|

|

| ||

†CLKRP = CLKXP = FSRP = FSXP = 0. If polarity of any of the signals is inverted, then the timing references of that signal are also inverted.

‡P = 1/CPU clock frequency in ns. For example, when running parts at 250 MHz, use P = 4 ns.

§The minimum CLKR/X period is twice the CPU cycle time (2P) and not faster than 75 Mbps (13.3 ns). This means that the maximum bit rate for communications between the McBSP and other devices is 75 Mbps for

33 ns (30 MHz) as the minimum CLKR/X clock cycle. The maximum bit rate for

¶This parameter applies to the maximum McBSP frequency. Operate serial clocks (CLKR/X) in the reasonable range of 40/60 duty cycle.

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443 | 91 |