SPRS292A − OCTOBER 2005 − REVISED NOVEMBER 2005

EDMA module and EDMA selector (continued)

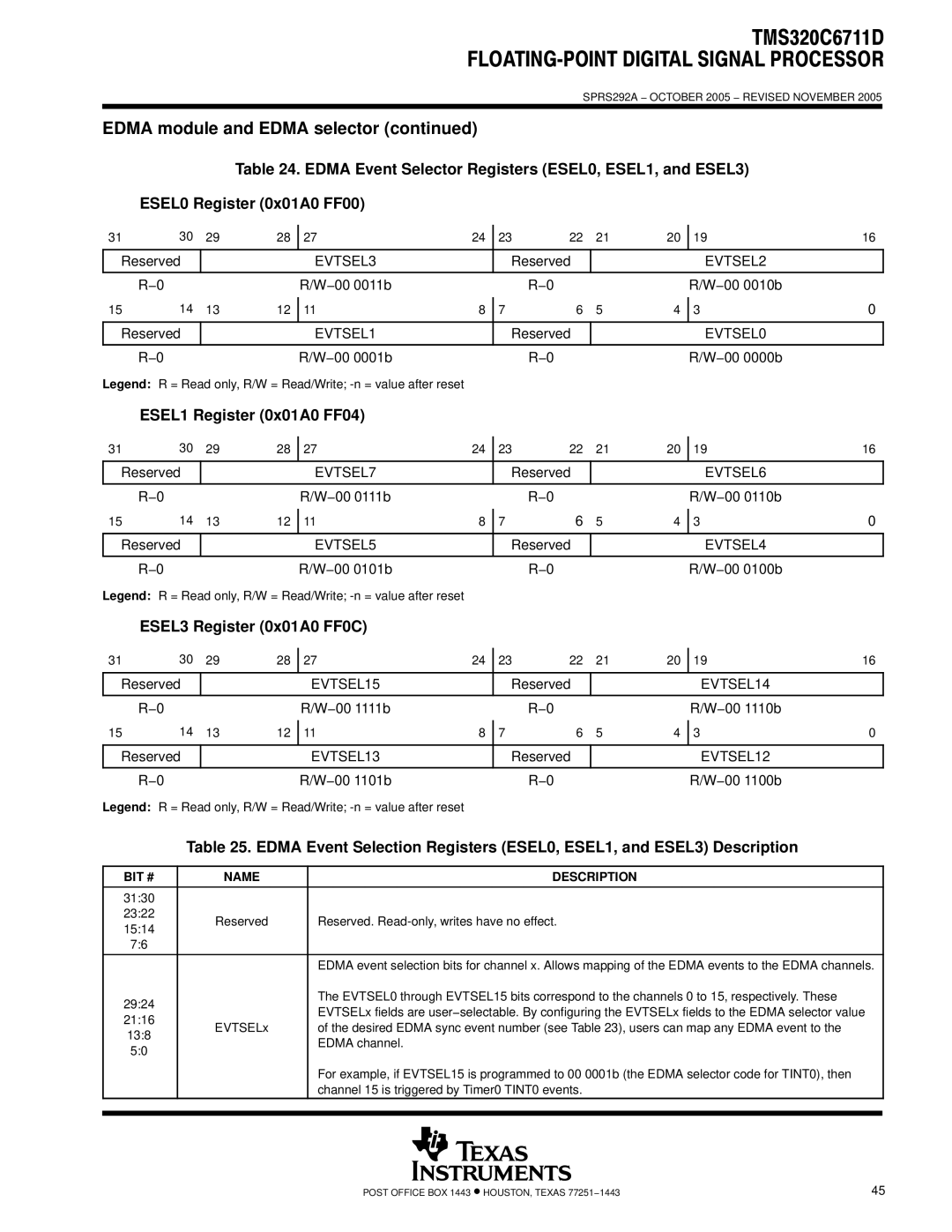

Table 24. EDMA Event Selector Registers (ESEL0, ESEL1, and ESEL3)

ESEL0 Register (0x01A0 FF00)

31 | 30 | 29 | 28 |

| 27 | 24 | 23 | 22 | 21 | 20 | 19 | 16 |

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

Reserved |

|

|

|

| EVTSEL3 |

| Reserved |

|

| EVTSEL2 |

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| R−0 |

|

| R/W−00 0011b |

|

| R−0 |

| R/W−00 0010b |

|

| ||||

15 | 14 | 13 | 12 |

|

| 8 |

| 6 | 5 | 4 |

| 0 |

| ||

| 11 | 7 | 3 |

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

Reserved |

|

|

|

| EVTSEL1 |

| Reserved |

|

| EVTSEL0 |

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| R−0 |

|

| R/W−00 0001b |

|

| R−0 |

| R/W−00 0000b |

|

| ||||

Legend: R = Read only, R/W = Read/Write; |

|

|

|

|

|

|

|

| |||||||

| ESEL1 Register (0x01A0 FF04) |

|

|

|

|

|

|

|

| ||||||

31 | 30 | 29 | 28 |

|

| 24 |

| 22 | 21 | 20 |

| 16 |

| ||

| 27 | 23 | 19 |

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

Reserved |

|

|

|

| EVTSEL7 |

| Reserved |

|

| EVTSEL6 |

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| R−0 |

|

| R/W−00 0111b |

|

| R−0 |

| R/W−00 0110b |

|

| ||||

15 | 14 | 13 | 12 |

|

| 8 |

| 6 | 5 | 4 |

| 0 |

| ||

| 11 | 7 | 3 |

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

Reserved |

|

|

|

| EVTSEL5 |

| Reserved |

|

| EVTSEL4 |

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| R−0 |

|

| R/W−00 0101b |

|

| R−0 |

| R/W−00 0100b |

|

| ||||

Legend: R = Read only, R/W = Read/Write; |

|

|

|

|

|

|

|

| |||||||

| ESEL3 Register (0x01A0 FF0C) |

|

|

|

|

|

|

|

| ||||||

31 | 30 | 29 | 28 |

|

| 24 |

| 22 | 21 | 20 |

| 16 |

| ||

| 27 | 23 | 19 |

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

Reserved |

|

|

|

| EVTSEL15 |

| Reserved |

|

| EVTSEL14 |

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| R−0 |

|

| R/W−00 1111b |

|

| R−0 |

| R/W−00 1110b |

|

| ||||

15 | 14 | 13 | 12 |

|

| 8 |

| 6 | 5 | 4 |

| 0 |

| ||

| 11 | 7 | 3 |

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

Reserved |

|

|

|

| EVTSEL13 |

| Reserved |

|

| EVTSEL12 |

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| R−0 |

|

| R/W−00 1101b |

|

| R−0 |

| R/W−00 1100b |

|

| ||||

Legend: R = Read only, R/W = Read/Write; |

|

|

|

|

|

|

|

| |||||||

|

| Table 25. EDMA Event Selection Registers (ESEL0, ESEL1, and ESEL3) Description |

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| BIT # |

| NAME |

|

|

|

|

|

| DESCRIPTION |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 31:30 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 23:22 |

| Reserved |

|

|

| Reserved. |

|

|

|

|

| |||

| 15:14 |

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| 7:6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

| EDMA event selection bits for channel x. Allows mapping of the EDMA events to the EDMA channels. |

| |||||||

| 29:24 |

|

|

|

|

| The EVTSEL0 through EVTSEL15 bits correspond to the channels 0 to 15, respectively. These |

|

| ||||||

|

|

|

|

|

| EVTSELx fields are user−selectable. By configuring the EVTSELx fields to the EDMA selector value |

|

| |||||||

| 21:16 |

|

|

|

|

|

|

| |||||||

|

| EVTSELx |

|

|

| of the desired EDMA sync event number (see Table 23), users can map any EDMA event to the |

|

| |||||||

| 13:8 |

|

|

|

|

|

| ||||||||

|

|

|

|

|

| EDMA channel. |

|

|

|

|

|

|

|

| |

| 5:0 |

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

| For example, if EVTSEL15 is programmed to 00 0001b (the EDMA selector code for TINT0), then |

|

| ||||||

|

|

|

|

|

|

| channel 15 is triggered by Timer0 TINT0 events. |

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443 | 45 |